Texas Instruments CD74HCT574M96, CD74HCT574M, CD74HCT574E, CD74HCT374M96, CD74HCT374M Datasheet

...

Data sheet acquired from Harris Semiconductor SCHS183

February 1998

CD74HC374, CD74HCT374, CD74HC574, CD74HCT574

High Speed CMOS Logic Octal D-Type Flip-Flop,

Three-State Positive-Edge Triggered

|

Features |

Description |

|

|

|

|

|

|

||||

|

• |

Buffered Inputs |

The Harris CD74HC374, CD74HCT374, CD74HC574 and |

|||||||||

[ /Title |

• |

Common Three-State Output Enable Control |

CD74HCT574 are Octal D-Type Flip-Flops with Three-State |

|||||||||

Outputs and the capability to drive 15 LSTTL loads. The eight |

||||||||||||

(CD74 |

• |

Three-State Outputs |

edge-triggered flip-flops enter data into their registers on the |

|||||||||

HC374 |

• |

Bus Line Driving Capability |

LOW to HIGH transition of clock (CP). The Output Enable |

|||||||||

|

|

|

|

|

|

|

|

|

|

|||

, |

(OE) controls the three-state outputs and is independent of |

|||||||||||

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

||

• Typical Propagation Delay (Clock to Q) = 15ns at |

the register operation. When Output Enable (OE) is HIGH the |

|||||||||||

CD74 |

||||||||||||

|

VCC = 5V, CL = 15pF, TA = 25oC |

outputs will be in the high impedance state. The 374 and 574 |

||||||||||

HCT37 |

• |

Fanout (Over Temperature Range) |

are identical in |

function and differ |

only in their pinout |

|||||||

4, |

arrangements. |

|

|

|

|

|

|

|||||

|

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads |

|

|

|

|

|

|

|||||

CD74 |

|

Ordering Information |

|

|

|

|

||||||

|

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads |

|

|

|

|

|||||||

HC574 |

|

|

|

|

|

|||||||

• Wide Operating Temperature Range . . . -55oC to 125oC |

|

|

|

|

|

|

|

|

|

|||

, |

|

|

|

TEMP. RANGE (oC) |

|

|

|

|

PKG. |

|||

• |

Balanced Propagation Delay and Transition Times |

|

PART NUMBER |

|

PACKAGE |

NO. |

||||||

CD74 |

|

|

||||||||||

|

CD74HC374E |

-55 to 125 |

|

20 Ld PDIP |

E20.3 |

|||||||

HCT57 |

• |

Significant Power Reduction Compared to LSTTL |

|

|

||||||||

|

|

|

|

|

|

|

|

|

||||

|

CD74HCT374E |

-55 to 125 |

|

20 Ld PDIP |

E20.3 |

|||||||

|

|

Logic ICs |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

CD74HCT574E |

-55 to 125 |

|

20 Ld PDIP |

E20.3 |

|||||

|

|

|

|

|

||||||||

|

• HC Types |

|

|

|

|

|

|

|||||

|

|

CD74HC574E |

-55 to 125 |

|

20 Ld PDIP |

E20.3 |

||||||

|

|

- 2V to 6V Operation |

|

|

|

|

|

|

||||

|

|

|

CD74HC574M |

-55 to 125 |

|

20 Ld SOIC |

M20.3 |

|||||

|

|

- High Noise Immunity: NIL = 30%, NIH = 30% of VCC |

|

|

|

|

|

|

||||

|

|

|

CD74HC374M |

-55 to 125 |

|

20 Ld SOIC |

M20.3 |

|||||

|

|

at VCC = 5V |

|

|

|

|

|

|

||||

|

|

|

CD74HCT374M |

-55 to 125 |

|

20 Ld SOIC |

M20.3 |

|||||

|

• HCT Types |

|

CD74HCT574M |

-55 to 125 |

|

20 Ld SOIC |

M20.3 |

|||||

|

|

- 4.5V to 5.5V Operation |

|

|

|

|

|

|

|

|||

|

|

NOTES: |

|

|

|

|

|

|

||||

|

|

- Direct LSTTL Input Logic Compatibility, |

|

1. When ordering, use the entire part number. Add the suffix 96 to |

||||||||

|

|

VIL= 0.8V (Max), VIH = 2V (Min) |

|

obtain the variant in the tape and reel. |

|

|

|

|

||||

|

|

- CMOS Input Compatibility, Il ≤ 1μA at VOL, VOH |

|

2. Wafer and die for this part number is available which meets all |

||||||||

|

|

|

|

electrical specifications. Please contact your local sales office or |

||||||||

|

|

|

|

Harris customer service for ordering information. |

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

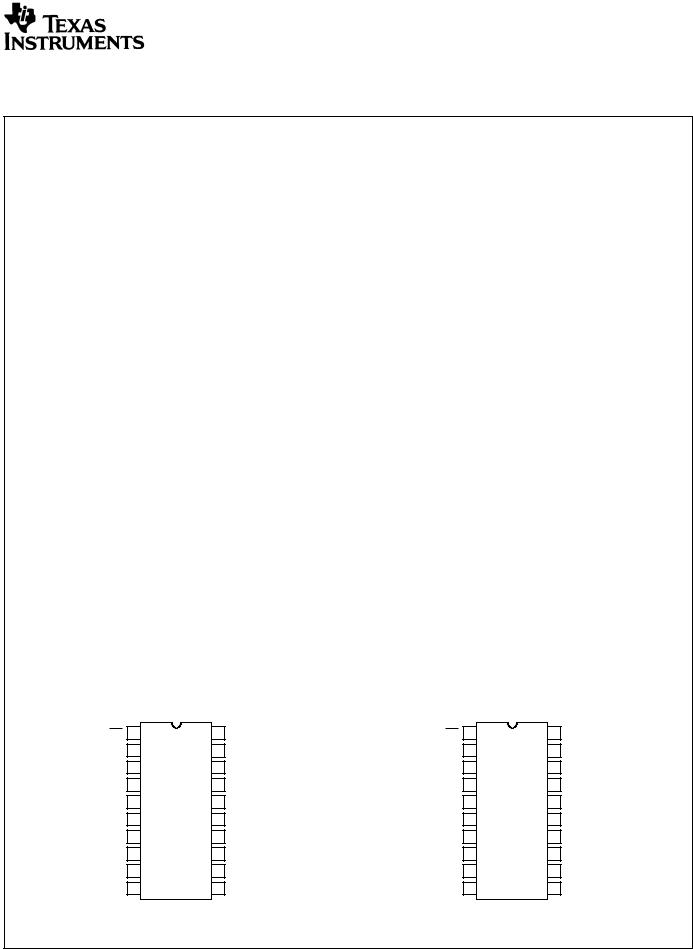

Pinouts |

|

|

|

|

|

|

|

|

|

||

|

|

CD74HC374, CD74HCT374 |

|

|

|

CD74HCT574 |

|

|

|

|

||

|

|

(PDIP, SOIC) |

|

|

|

(PDIP, SOIC) |

|

|

|

|

||

|

|

TOP VIEW |

|

|

|

TOP VIEW |

|

|

|

|

||

OE |

1 |

20 |

VCC |

OE |

1 |

20 |

VCC |

Q0 |

2 |

19 |

Q7 |

D0 |

2 |

19 |

Q0 |

D0 |

3 |

18 |

D7 |

D1 |

3 |

18 |

Q1 |

D1 |

4 |

17 |

D6 |

D2 |

4 |

17 |

Q2 |

Q1 |

5 |

16 |

Q6 |

D3 |

5 |

16 |

Q3 |

Q2 |

6 |

15 |

Q5 |

D4 |

6 |

15 |

Q4 |

D2 |

7 |

14 |

D5 |

D5 |

7 |

14 |

Q5 |

D3 |

8 |

13 |

D4 |

D6 |

8 |

13 |

Q6 |

Q3 |

9 |

12 |

Q4 |

D7 |

9 |

12 |

Q7 |

GND |

10 |

11 CP |

GND |

10 |

11 CP |

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. |

File Number 1663.1 |

|

Copyright © Harris Corporation 1998

1

CD74HC374, CD74HCT374, CD74HC574, CD74HCT574 |

|

|||||||

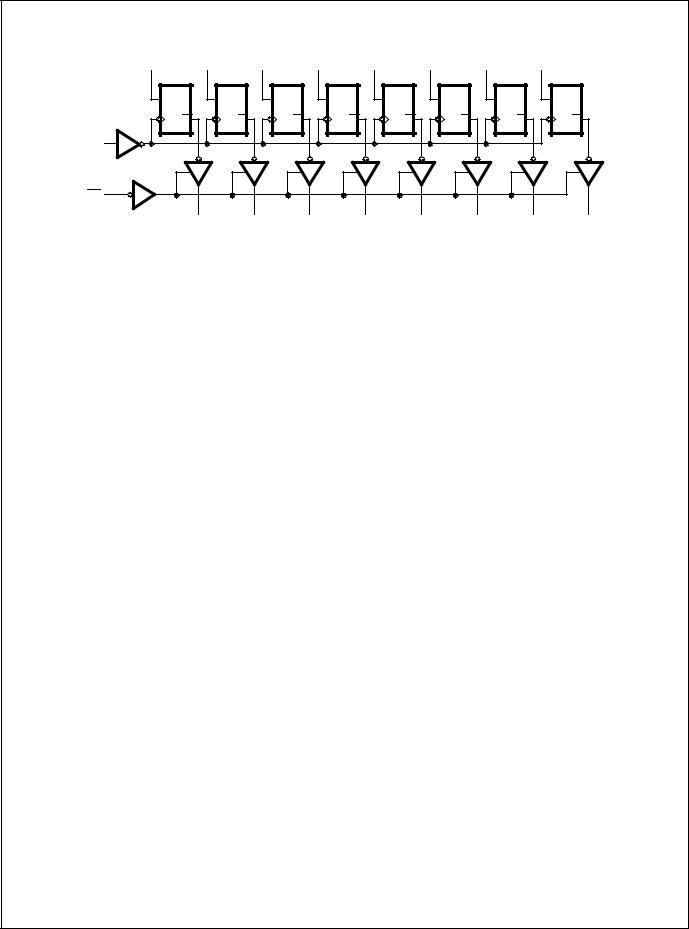

Functional Diagram |

|

|

|

|

|

|

|

|

D0 |

D1 |

D2 |

D3 |

D4 |

D5 |

D6 |

D7 |

|

D |

D |

D |

D |

D |

D |

D |

|

D |

CP Q |

CP Q |

CP Q |

CP Q |

CP Q |

CP Q |

CP Q |

|

CP Q |

CP |

|

|

|

|

|

|

|

|

OE |

|

|

|

|

|

|

|

|

|

Q0 |

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q6 |

Q7 |

TRUTH TABLE

|

|

|

INPUTS |

|

OUTPUT |

|

|

|

|

|

|

|

|

|

CP |

Dn |

Qn |

|

OE |

||||

|

|

|

|

|

|

|

L |

|

− |

H |

H |

|

|

|

|

|

|

|

L |

|

− |

L |

L |

|

|

|

|

|

|

|

L |

|

L |

X |

Q0 |

|

|

|

|

|

|

|

H |

|

X |

X |

Z |

|

|

|

|

|

|

NOTE:

H = High Level (Steady State)

L = Low Level (Steady State) X = Don’t Care

− = Transition from Low to High Level

Q0 = The level of Q before the indicated steady-state input conditions were established

Z = High Impedance State

2

CD74HC374, CD74HCT374, CD74HC574, CD74HCT574

Absolute Maximum Ratings

DC Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . |

-0.5V to 7V |

DC Input Diode Current, IIK |

±20mA |

For VI < -0.5V or VI > VCC + 0.5V . . . . . . . . . . . . . . . . . . |

|

DC Output Diode Current, IOK |

±20mA |

For VO < -0.5V or VO > VCC + 0.5V . . . . . . . . . . . . . . . . |

|

DC Drain Current, per Output, IO |

±35mA |

For -0.5V < VO < VCC + 0.5V. . . . . . . . . . . . . . . . . . . . . . |

|

DC Output Source or Sink Current per Output Pin, IO |

±25mA |

For VO > -0.5V or VO < VCC + 0.5V . . . . . . . . . . . . . . . . |

|

DC VCC or Ground Current, ICC . . . . . . . . . . . . . . . . . . . . . |

. . . .±50mA |

Thermal Information |

|

Thermal Resistance (Typical, Note 3) |

θJA (oC/W) |

PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 125 |

SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 120 |

Maximum Junction Temperature . . . . . . . . . . . . . . . . |

. . . . . . . 150oC |

Maximum Storage Temperature Range . . . . . . . . . . |

-65oC to 150oC |

Maximum Lead Temperature (Soldering 10s) . . . . . . |

. . . . . . . 300oC |

(SOIC - Lead Tips Only) |

|

Operating Conditions

Temperature Range, TA . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC Supply Voltage Range, VCC

HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V

DC Input or Output Voltage, VI, VO . . . . . . . . . . . . . . . . . 0V to VCC Input Rise and Fall Time

2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns (Max) 4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns (Max)

6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400ns (Max)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

3. θJA is measured with the component mounted on an evaluation PC board in free air.

DC Electrical Specifications

|

|

TEST |

|

|

25oC |

|

-40oC TO 85oC |

-55oC TO 125oC |

|

|||

|

|

CONDITIONS |

VCC |

|

|

|

||||||

PARAMETER |

SYMBOL |

VI (V) |

IO (mA) |

(V) |

MIN |

TYP |

MAX |

MIN |

MAX |

MIN |

MAX |

UNITS |

HC TYPES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

High Level Input |

VIH |

- |

- |

2 |

1.5 |

- |

- |

1.5 |

- |

1.5 |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

3.15 |

- |

- |

3.15 |

- |

3.15 |

- |

V |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

4.2 |

- |

- |

4.2 |

- |

4.2 |

- |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

Low Level Input |

VIL |

- |

- |

2 |

- |

- |

0.5 |

- |

0.5 |

- |

0.5 |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

- |

1.35 |

- |

1.35 |

- |

1.35 |

V |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

1.8 |

- |

1.8 |

- |

1.8 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

High Level Output |

VOH |

VIH or VIL |

-0.02 |

2 |

1.9 |

- |

- |

1.9 |

- |

1.9 |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-0.02 |

4.5 |

4.4 |

- |

- |

4.4 |

- |

4.4 |

- |

V |

|

CMOS Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-0.02 |

6 |

5.9 |

- |

- |

5.9 |

- |

5.9 |

- |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

High Level Output |

|

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-6 |

4.5 |

3.98 |

- |

- |

3.84 |

- |

3.7 |

- |

V |

|

TTL Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-7.8 |

6 |

5.48 |

- |

- |

5.34 |

- |

5.2 |

- |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Low Level Output |

VOL |

VIH or VIL |

0.02 |

2 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.02 |

4.5 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

|

CMOS Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.02 |

6 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Low Level Output |

|

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

4.5 |

- |

- |

0.26 |

- |

0.33 |

- |

0.4 |

V |

|

TTL Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7.8 |

6 |

- |

- |

0.26 |

- |

0.33 |

- |

0.4 |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Leakage |

II |

VCC or |

- |

6 |

- |

- |

±0.1 |

- |

±1 |

- |

±1 |

μA |

Current |

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3

Loading...

Loading...