Texas Instruments CD74HCT4060M96, CD74HCT4060M, CD74HCT4060E, CD74HC4060M96, CD74HC4060M Datasheet

...

Data sheet acquired from Harris Semiconductor SCHS207

February 1998

CD74HC4060,

CD74HCT4060

High Speed CMOS Logic 14-Stage Binary Counter with Oscillator

|

Features |

||

|

• |

Onboard Oscillator |

|

[ /Title |

• Common Reset |

||

(CD74 |

• |

Negative Edge Clocking |

|

HC406 |

• Typical fMAX = 50MHz at VCC = 5V, CL = 15pF, |

||

0, |

|||

|

T = 25oC |

||

CD74 |

|

A |

|

• |

Fanout (Over Temperature Range) |

||

HCT40 |

|||

|

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads |

||

60)- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

/Sub- |

• |

Wide Operating Temperature Range . . . -55oC to 125oC |

|

ject |

• |

Balanced Propagation Delay and Transition Times |

|

(High |

|||

• |

Significant Power Reduction Compared to LSTTL |

||

Speed |

|||

CMOS |

|

Logic ICs |

|

|

|

•HC Types

-2V to 6V Operation

-High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

•HCT Types

-4.5V to 5.5V Operation

-Direct LSTTL Input Logic Compatibility, VIL= 0.8V (Max), VIH = 2V (Min)

-CMOS Input Compatibility, Il ≤ 1μA at VOL, VOH

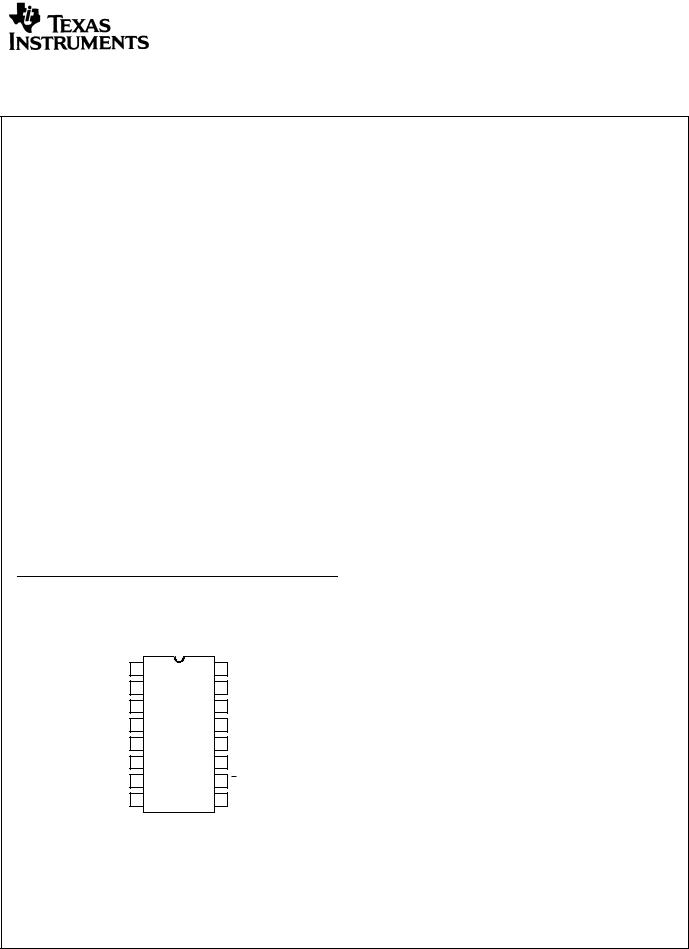

Pinout

CD74HC4060, CD74HCT4060

(PDIP, SOIC)

TOP VIEW

Q12 |

1 |

16 VCC |

Q13 |

2 |

15 |

Q10 |

Q14 |

3 |

14 |

Q8 |

Q6 |

4 |

13 |

Q9 |

Q5 |

5 |

12 |

MR |

Q7 |

6 |

11 |

φI |

Q4 |

7 |

10 |

φO |

GND |

8 |

9 |

φO |

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. |

File Number 1654.1 |

|

Copyright © Harris Corporation 1998

1

CD74HC4060, CD74HCT4060

Description

The Harris CD74HC4060 and CD74HCT4060 each consist of an oscillator section and 14 ripple-carry binary counter stages. The oscillator configuration allows design of either RC or crystal oscillator circuits. A Master Reset input is provided which resets the counter to the all-0’s state and disables the oscillator. A high level on the MR line accomplishes the reset function. All counter stages are master-slave flip-flops. The state of the counter is advanced one step in binary order on the negative transition of φI (and φO). All inputs and outputs are buffered. Schmitt trigger action on the input-pulse-line permits unlimited rise and fall times.

In order to achieve a symmetrical waveform in the oscillator section the HCT4060 input pulse switch points are the same as in the HC4060; only the MR input in the HCT4060 has

TTL switching levels.

Ordering Information

|

TEMP. RANGE (oC) |

|

PKG. |

PART NUMBER |

PACKAGE |

NO. |

|

CD74HC4060E |

-55 to 125 |

16 Ld PDIP |

E16.3 |

|

|

|

|

CD74HCT4060E |

-55 to 125 |

16 Ld PDIP |

E16.3 |

|

|

|

|

CD74HC4060M |

-55 to 125 |

16 Ld SOIC |

M16.15 |

|

|

|

|

CD74HCT4060M |

-55 to 125 |

16 Ld SOIC |

M16.15 |

|

|

|

|

NOTES: |

|

|

|

1.When ordering, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

2.Wafer and die for this part number is available which meets all electrical specifications. Please contact your local sales office or Harris customer service for ordering information.

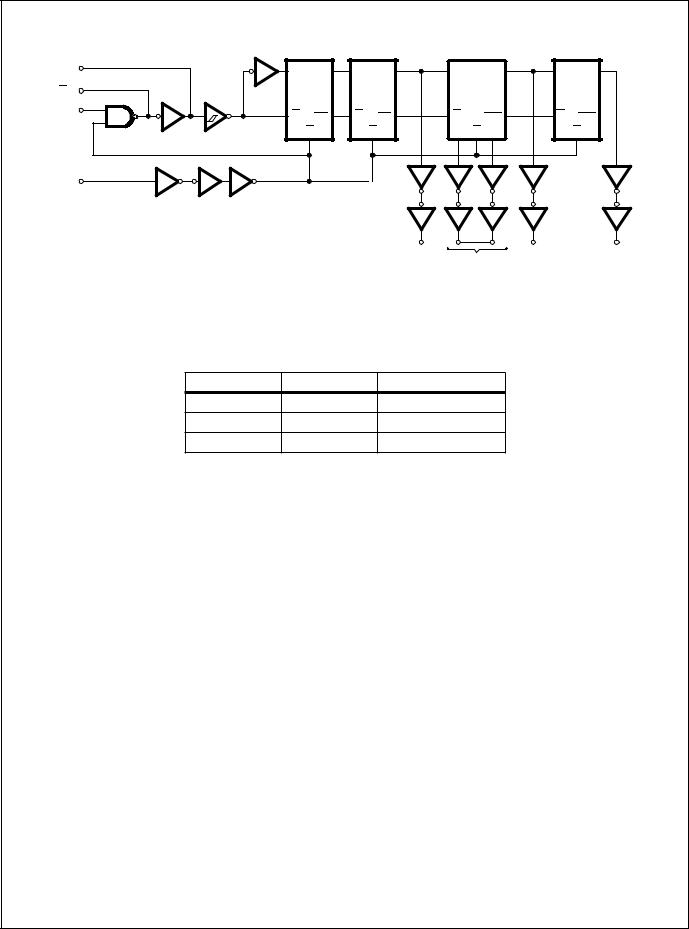

Functional Diagram

|

|

|

|

|

|

|

|

|

|

7 |

Q4 |

|

|

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

Q5 |

|

|

|

|

|

|

|

|

|

|

|

4 |

|

12 |

|

|

|

Q6 |

|||||||

|

|

|

|

||||||||

MR |

|

|

|

|

|

6 |

|||||

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

Q7 |

|

|

|

|

|

|

|

|

|

|

|

14 |

|

|

|

|

|

|

|

|

14-STAGE |

Q8 |

|||

|

|

|

|

|

|

|

RIPPLE |

13 |

|||

11 |

COUNTER |

|

|||||||||

|

φI |

|

|

|

|

AND |

|

Q9 |

|||

|

|

|

|

|

15 |

||||||

|

|

|

|

|

|

|

OSCILLATOR |

Q10 |

|||

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

Q12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

Q13 |

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

Q14 |

|

9 |

|

|

|

|

|||||||

|

|

|

|

||||||||

|

|

|

|

|

|||||||

|

|

|

|

|

|||||||

|

φO |

|

|

|

|

|

|

GND = 8 |

|||

|

|

|

|

|

|

||||||

|

|

10 |

|

|

|

VCC = 16 |

|||||

|

φO |

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

||||

2

CD74HC4060, CD74HCT4060

9 |

ø1 |

|

ø4 |

|

ø5 |

|

|

ø14 Q14 |

øO |

Q1 |

Q4 |

Q13 |

|

||||

10 |

|

|

|

|

|

|

|

|

øO |

FF1 |

FF4 |

FF5 - FF13 |

|

FF14 |

|||

11 |

|

|||||||

ø1 |

ø1 |

Q1 |

ø4 |

Q4 |

ø5 |

Q13 |

|

ø14 Q14 |

|

|

|||||||

|

|

R |

|

R |

R |

|

|

R |

12 |

|

|

|

|

|

|

|

|

MR |

|

|

|

|

|

|

|

|

|

|

|

|

7 |

|

|

2 |

3 |

|

|

|

|

Q4 |

5, 4, 6, 14, 13, 15, 1 |

Q13 |

Q14 |

|

|

|

|

|

|

Q5 - Q10, Q12 |

|

|

|

|

FIGURE 1. LOGIC BLOCK DIAGRAM |

|

|

|

||||

|

|

TRUTH TABLE |

|

|

|

|

||

øI |

|

MR |

|

OUTPUT STATE |

|

|

|

|

− |

|

L |

|

No Change |

|

|

|

|

↓ |

|

L |

|

Advance to Next State |

|

|

||

X |

|

H |

|

All Outputs are Low |

|

|

||

3

Loading...

Loading...