Texas Instruments CD74HCT40103M96, CD74HCT40103M, CD74HCT40103E, CD74HC40103M96, CD74HC40103M Datasheet

...

Data sheet acquired from Harris Semiconductor SCHS221

November 1997

CD74HC40103,

CD74HCT40103

High Speed CMOS Logic

8-Stage Synchronous Down Counters

[ /Title (CD74H C40103, CD74H CT4010 3)

/Subject (High Speed CMOS Logic 8-

Features

•Synchronous or Asynchronous Preset

•Cascadable in Synchronous or Ripple Mode

•Fanout (Over Temperature Range)

-Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads

-Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

•Wide Operating Temperature Range . . . -55oC to 125oC

•Balanced Propagation Delay and Transition Times

•Significant Power Reduction Compared to LSTTL Logic ICs

•HC Types

-2V to 6V Operation

-High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

•HCT Types

-4.5V to 5.5V Operation

-Direct LSTTL Input Logic Compatibility, VIL= 0.8V (Max), VIH = 2V (Min)

-CMOS Input Compatibility, Il ≤ 1μA at VOL, VOH

Ordering Information

|

TEMP. RANGE (oC) |

|

PKG. |

PART NUMBER |

PACKAGE |

NO. |

|

CD74HC40103E |

-55 to 125 |

16 Ld PDIP |

E16.3 |

|

|

|

|

CD74HCT40103E |

-55 to 125 |

16 Ld PDIP |

E16.3 |

|

|

|

|

CD74HC40103M |

-55 to 125 |

16 Ld SOIC |

M16.15 |

|

|

|

|

CD74HCT40103M |

-55 to 125 |

16 Ld SOIC |

M16.15 |

|

|

|

|

NOTES: |

|

|

|

1.When ordering, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

2.Wafer or die for this part number is available which meets all electrical specifications. Please contact your local sales office or Harris customer service for ordering information.

Description

The Harris CD74HC40103 and CD74HCT40103 are manufactured with high speed silicon gate technology and consist of an 8-stage synchronous down counter with a single output which is active when the internal count is zero. The 40103 contains a single 8-bit binary counter. Each has control inputs for enabling or disabling the clock, for clearing the counter to its maximum count, and for presetting the counter either synchronously or asynchronously. All control

inputs and the TC output are active-low logic.

In normal operation, the counter is decremented by one count on each positive transition of the CLOCK (CP). Counting is inhibited when the TE input is high. The TC output goes low when the count reaches zero if the TE input is low, and remains low for one full clock period.

When the PE input is low, data at the P0-P7 inputs are clocked into the counter on the next positive clock transition

regardless of the state of the TE input. When the PL input is low, data at the P0-P7 inputs are asynchronously forced into the counter regardless of the state of the PE, TE, or CLOCK inputs. Input P0-P7 represent a single 8-bit binary word for the 40103. When the MR input is low, the counter is asynchronously cleared to its maximum count of 25510, regardless of the state of any other input. The precedence relationship between control inputs is indicated in the truth table.

If all control inputs except TE are high at the time of zero count, the counters will jump to the maximum count, giving a counting sequence of 100 or 256 clock pulses long.

The 40103 may be cascaded using the TE input and the TC output, in either a synchronous or ripple mode. These circuits possess the the low power consumption usually associated with CMOS circuitry, yet have speeds comparable to low power Schottky TTL circuits and can drive up to 10 LSTTL loads.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. |

File Number 1596.1 |

|

|

||

Copyright © Harris Corporation 1997 |

1 |

|

|

|

|

CD74HC40103, CD74HCT40103

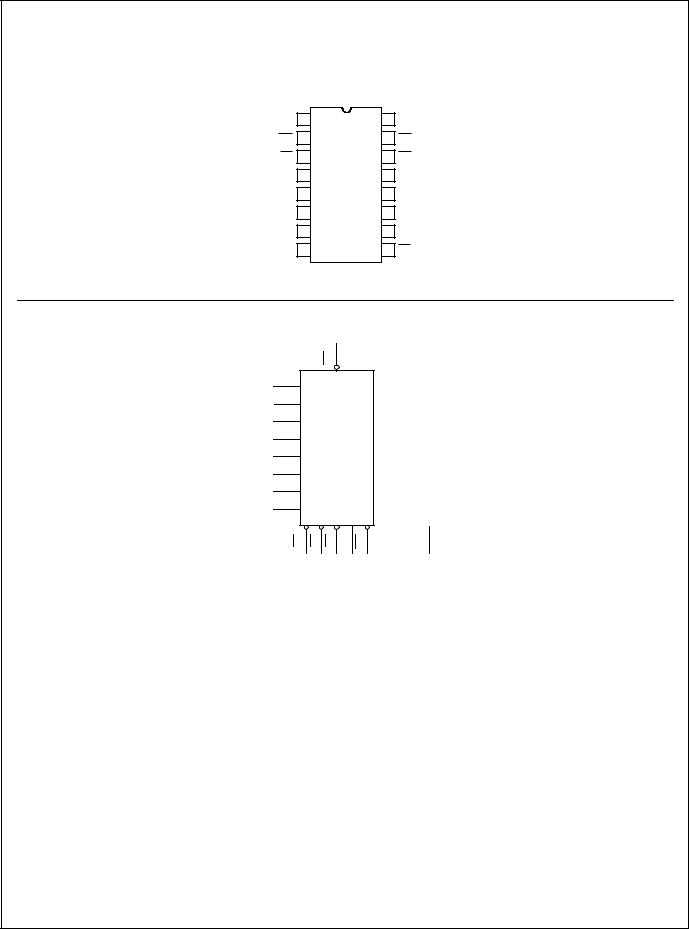

Pinout

CD74HC40103, CD74HCT40103

(PDIP, SOIC)

TOP VIEW

CP |

1 |

16 VCC |

MR |

2 |

15 PE (SYNC) |

TE |

3 |

14 |

TC |

P0 |

4 |

13 |

P7 |

P1 |

5 |

12 |

P6 |

P2 |

6 |

11 |

P5 |

P3 |

7 |

10 |

P4 |

GND |

8 |

9 |

PL (ASYNC) |

Functional Diagram

14 TC

P7

13

P6

12

11 P5

P4

10

P3

7

P2

6

P1

5

P0

4

PE |

PL |

TE |

CP |

|

MR |

15 |

9 |

|

3 |

1 |

2 |

TRUTH TABLE

V |

|

GND |

CC |

|

|

|

|

|

|

16 |

|

8

|

|

|

CONTROL INPUTS |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

PRESET MODE |

ACTION |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

MR |

PL |

PE |

TE |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

1 |

|

1 |

|

1 |

|

|

1 |

|

Synchronous |

Inhibit Counter |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

1 |

|

1 |

|

1 |

|

|

0 |

|

|

Count Down |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

1 |

|

1 |

|

0 |

|

|

X |

|

|

Preset On Next Positive Clock Transition |

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

1 |

|

0 |

|

|

X |

|

X |

|

Asynchronously |

Preset Asychronously |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0 |

|

|

X |

|

|

X |

|

X |

|

|

Clear to Maximum Count |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE:

1 = High Level.

0 = Low Level.

X = Don’t Care.

Clock connected to clock input.

Synchronous Operation: changes occur on negative-to-positive clock transitions. Load Inputs: MSB = P7, LSB = P0.

2

CD74HC40103, CD74HCT40103

Absolute Maximum Ratings

DC Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . |

-0.5V to 7V |

DC Input Diode Current, IIK |

±20mA |

For VI < -0.5V or VI > VCC + 0.5V . . . . . . . . . . . . . . . . . . |

|

DC Output Diode Current, IOK |

±20mA |

For VO < -0.5V or VO > VCC + 0.5V . . . . . . . . . . . . . . . . |

|

DC Output Source or Sink Current per Output Pin, IO |

±25mA |

For VO > -0.5V or VO < VCC + 0.5V . . . . . . . . . . . . . . . . |

|

DC VCC or Ground Current, ICC . . . . . . . . . . . . . . . . . . . . . |

. . . .±50mA |

Thermal Information |

|

Thermal Resistance (Typical, Note 3) |

θJA (oC/W) |

PDIP Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 90 |

SOIC Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 160 |

Maximum Junction Temperature . . . . . . . . . . . . . . . . |

. . . . . . . 150oC |

Maximum Storage Temperature Range . . . . . . . . . . |

-65oC to 150oC |

Maximum Lead Temperature (Soldering 10s) . . . . . . |

. . . . . . . 300oC |

(SOIC - Lead Tips Only) |

|

Operating Conditions

Temperature Range, TA . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC Supply Voltage Range, VCC

HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V

DC Input or Output Voltage, VI, VO . . . . . . . . . . . . . . . . . 0V to VCC Input Rise and Fall Time

2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns (Max) 4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns (Max) 6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400ns (Max)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTE:

3. θJA is measured with the component mounted on an evaluation PC board in free air.

DC Electrical Specifications

|

|

TEST |

|

|

25oC |

|

-40oC TO 85oC |

-55oC TO 125oC |

|

|||

|

|

CONDITIONS |

VCC |

|

|

|

||||||

PARAMETER |

SYMBOL |

VI (V) |

IO (mA) |

(V) |

MIN |

TYP |

MAX |

MIN |

MAX |

MIN |

MAX |

UNITS |

HC TYPES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

High Level Input |

VIH |

- |

- |

2 |

1.5 |

- |

- |

1.5 |

- |

1.5 |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

3.15 |

- |

- |

3.15 |

- |

3.15 |

- |

V |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

4.2 |

- |

- |

4.2 |

- |

4.2 |

- |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

Low Level Input |

VIL |

- |

- |

2 |

- |

- |

0.5 |

- |

0.5 |

- |

0.5 |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

- |

1.35 |

- |

1.35 |

- |

1.35 |

V |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

1.8 |

- |

1.8 |

- |

1.8 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

High Level Output |

VOH |

VIH or VIL |

-0.02 |

2 |

1.9 |

- |

- |

1.9 |

- |

1.9 |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-0.02 |

4.5 |

4.4 |

- |

- |

4.4 |

- |

4.4 |

- |

V |

|

CMOS Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-0.02 |

6 |

5.9 |

- |

- |

5.9 |

- |

5.9 |

- |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

High Level Output |

|

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-4 |

4.5 |

3.98 |

- |

- |

3.84 |

- |

3.7 |

- |

V |

|

TTL Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-5.2 |

6 |

5.48 |

- |

- |

5.34 |

- |

5.2 |

- |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Low Level Output |

VOL |

VIH or VIL |

0.02 |

2 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.02 |

4.5 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

|

CMOS Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.02 |

6 |

- |

- |

0.1 |

- |

0.1 |

- |

0.1 |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Low Level Output |

|

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

4.5 |

- |

- |

0.26 |

- |

0.33 |

- |

0.4 |

V |

|

TTL Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

5.2 |

6 |

- |

- |

0.26 |

- |

0.33 |

- |

0.4 |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Leakage |

II |

VCC or |

- |

6 |

- |

- |

±0.1 |

- |

±1 |

- |

±1 |

μA |

Current |

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Quiescent Device |

ICC |

VCC or |

0 |

6 |

- |

- |

8 |

- |

80 |

- |

160 |

μA |

Current |

|

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

3

Loading...

Loading...