Texas Instruments CD74HCT4538M96, CD74HCT4538M, CD74HCT4538E, CD74HC4538PWR, CD74HC4538M96 Datasheet

...

Data sheet acquired from Harris Semiconductor SCHS123

June 1998

CD54HC4538, CD74HC4538, CD74HCT4538

High Speed CMOS Logic Dual Retriggerable

Precision Monostable Multivibrator

|

Features |

||||||

|

• |

Retriggerable/Resettable Capability |

|||||

[ /Title |

• |

Trigger and Reset Propagation Delays Independent of |

|||||

|

RX, CX |

||||||

(CD54 |

|

||||||

• |

Triggering from the Leading or Trailing Edge |

||||||

HC453 |

|||||||

• |

Q and |

|

Buffered Outputs Available |

||||

8, |

Q |

||||||

|

|

|

|

|

|

||

CD74 |

• |

Separate Resets |

|||||

HC453 |

• |

Wide Range of Output-Pulse Widths |

|||||

8, |

|

|

|

|

|

|

|

• |

Schmitt Trigger Input on A andB Inputs |

||||||

CD74 |

|||||||

• |

Retrigger Time is Independent of CX |

||||||

HCT45 |

|||||||

|

|

|

|

|

|

||

38)• Fanout (Over Temperature Range)

/Sub- |

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads |

|

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads |

||

ject |

||

• Wide Operating Temperature Range . . . -55oC to 125oC |

||

(High |

||

Speed |

• Balanced Propagation Delay and Transition Times |

|

CMOS |

• Significant Power Reduction Compared to LSTTL |

|

Logic |

Logic ICs |

•HC Types

-2V to 6V Operation

-High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

•HCT Types

-4.5V to 5.5V Operation

-Direct LSTTL Input Logic Compatibility, VIL= 0.8V (Max), VIH = 2V (Min)

-CMOS Input Compatibility, Il ≤ 1μA at VOL, VOH

Pinout

CD54HC4538, CD74HC4538, CD74HCT4538

(PDIP, SOIC, CERDIP) |

|||

|

|

TOP VIEW |

|

1CX |

1 |

16 |

VCC |

1RXCX |

2 |

15 |

2CX |

1R |

3 |

14 2RXCX |

1A |

4 |

13 |

2R |

1B |

5 |

12 |

2A |

1Q |

6 |

11 |

2B |

1Q |

7 |

10 |

2Q |

GND |

8 |

9 |

2Q |

Description

The Harris CD54HC4538, CD74HC4538 and CD74HCT4538 are dual retriggerable/resettable monostable precision multivibrators for fixed voltage timing applications. An external resistor (RX) and an external capacitor (CX) control the timing and the accuracy for the circuit. Adjustment of RX and CX provides a wide range of output

pulse widths from the Q and Q terminals. The propagation delay from trigger input-to-output transition and the propagation delay from reset input-to-output transition are independent of RX and CX.

Leading-edge triggering (A) and trailing edge triggering (B) inputs are provided for triggering from either edge of the input pulse. An unused “A” input should be tied to GND and

an unused B should be tied to VCC. On power up the IC is reset. Unused resets and sections must be terminated. In

normal operation the circuit retriggers on the application of each new trigger pulse. To operate in the non-triggerable mode Q is connected to B when leading edge triggering (A) is used or Q is connected to A when trailing edge triggering

(B) is used. The period (τ) can be calculated from τ = (0.7) RX, CX; RMIN is 5kΩ. CMIN is 0pF.

Ordering Information

|

TEMP. RANGE |

|

PKG. |

PART NUMBER |

(oC) |

PACKAGE |

NO. |

CD54HC4538F |

-55 to 125 |

16 Ld CERDIP |

F16.3 |

|

|

|

|

CD74HC4538E |

-55 to 125 |

16 Ld PDIP |

E16.3 |

|

|

|

|

CD74HCT4538E |

-55 to 125 |

16 Ld PDIP |

E16.3 |

|

|

|

|

CD74HC4538M |

-55 to 125 |

16 Ld SOIC |

M16.15 |

|

|

|

|

CD74HCT4538M |

-55 to 125 |

16 Ld SOIC |

M16.15 |

|

|

|

|

NOTES: |

|

|

|

1.When ordering, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

2.Wafer and die for this part number is available which meets all electrical specifications. Please contact your local sales office or Harris customer service for ordering information.

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. |

File Number 1671.2 |

|

|

||

Copyright © Harris Corporation 1998 |

1 |

|

|

|

|

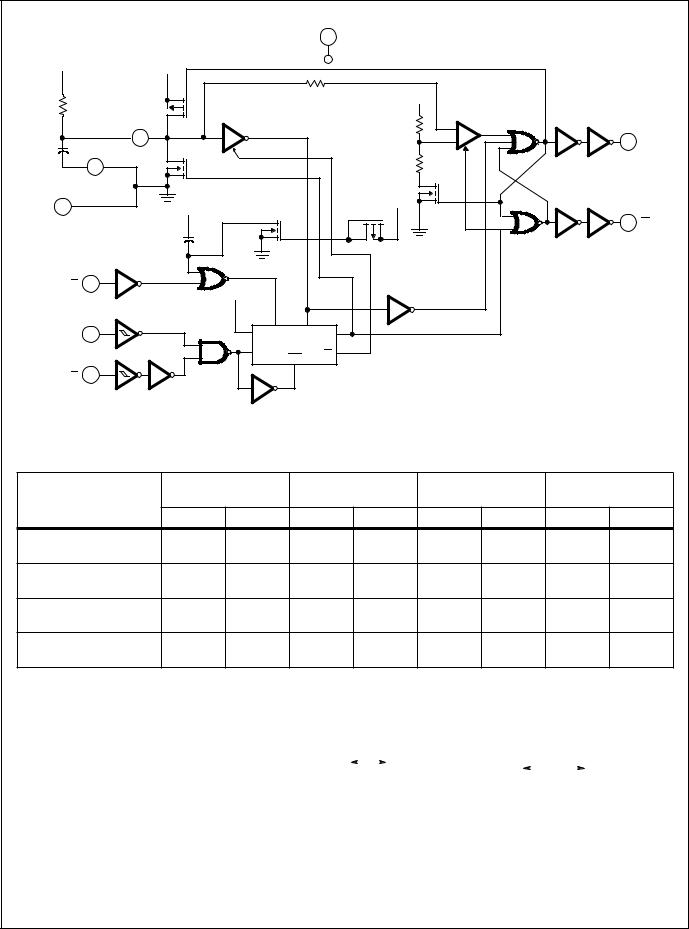

CD54HC4538, CD74HC4538, CD74HCT4538

Functional Diagram

|

1Cx |

1Rx |

|

|

|

|

VCC |

|

1 |

2 |

|

4 |

1Cx |

1RxCx |

6 |

|

|

||

1A |

|

|

1Q |

5 |

MONO 1 |

7 |

|

|

|

||

1B |

|

|

1Q |

3 |

|

|

|

1R |

|

|

|

13 |

|

|

|

2R |

|

|

|

12 |

|

|

10 |

2A |

|

|

2Q |

11 |

MONO 2 |

9 |

|

|

|

||

2B |

|

|

2Q |

|

2Cx |

2RxCx |

|

|

15 |

14 |

|

GND = 8 |

VCC |

VCC = 16 |

2Cx 2Rx |

|

|

TRUTH TABLE |

|

|

|

|

INPUTS |

|

|

OUTPUTS |

|

R |

A |

B |

Q |

CL |

R1 |

Q |

|

||||

L |

X |

X |

L |

H |

|

|

|

|

|

D |

|

X |

H |

X |

L |

H |

|

X |

X |

L |

L |

H |

CL |

|

|||||

H |

L |

↓ |

|

|

p |

|

|

n |

|||

H |

− |

H |

|

|

CL |

R2

CL |

Q |

|

p |

n |

CL

|

Q |

CL |

|

p |

|

n |

R1 |

NOTE: H = High Level, L = Low Level, − = Transition from Low to |

|

CL |

|

||||||||

High, ↓ = Transition from High to Low, |

|

|

|

One High Level Pulse, |

FIGURE 1. FF DETAIL |

||||||

|

|

||||||||||

|

|

|

|

One Low Level Pulse, X = Irrelevant. |

|

||||||

|

|

|

|

|

|||||||

2

CD54HC4538, CD74HC4538, CD74HCT4538

16

|

VCC |

VCC |

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

RX |

|

|

|

|

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2(14) |

|

|

|

|

R1 |

+ |

COMP II |

|

6(10) |

CX |

1(15) |

|

|

|

|

|

- |

|

|

Q |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

R2 |

|

|

|

|

8 |

|

VCC |

|

|

|

VCC |

|

|

|

7(9) |

|

|

|

|

|

|

|

|

|||

|

|

|

HIGH Z |

|

|

|

|

|

|

Q |

|

|

|

|

|

|

|

|

|

|

|

|

3(13) |

|

|

|

|

|

|

|

|

|

|

R |

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4(12) |

|

|

|

|

|

|

|

|

|

|

A |

|

D R1 |

FF |

R2 Q |

|

|

|

|

|

|

|

|

CL |

Q |

|

|

|

|

|

|

|

5(11) |

|

CL |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

||

|

B |

|

|

|

|

|

|

|

|

|

|

|

|

FIGURE 2. LOGIC DIAGRAM (1 MONO) |

|

|

|

||||

|

|

|

FUNCTIONAL TERMINAL CONNECTIONS |

|

|

|

||||

|

|

VCC TO |

|

GND TO |

INPUT PULSE TO |

OTHER |

||||

|

|

TERMINAL NUMBER |

TERMINAL NUMBER |

TERMINAL NUMBER |

CONNECTIONS |

|||||

|

FUNCTION |

MONO1 |

MONO2 |

|

MONO1 |

MONO2 |

MONO1 |

MONO2 |

MONO1 |

MONO2 |

Leading-Edge |

3, 5 |

11, 13 |

|

|

|

4 |

12 |

|

|

|

Trigger/Retriggerable |

|

|

|

|

|

|

|

|

|

|

Leading-Edge |

3 |

13 |

|

|

|

4 |

12 |

5-7 |

11-9 |

|

Trigger/Non-Retriggerable |

|

|

|

|

|

|

|

|

|

|

Trailing-Edge |

3 |

13 |

|

4 |

12 |

5 |

11 |

|

|

|

Trigger/Retriggerable |

|

|

|

|

|

|

|

|

|

|

Trailing-Edge |

3 |

13 |

|

|

|

5 |

11 |

4-6 |

12-10 |

|

Trigger/Non-Retriggerable |

|

|

|

|

|

|

|

|

|

|

NOTES: |

|

|

|

|

|

|

|

|

|

|

3.A retriggerable one-shot multivibrator has an output pulse width which is extended one full time period (T) after application of the last trigger pulse.

4.A non-triggerable one-shot multivibrator has a time period (T) referenced from the application of the first trigger pulse.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T |

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

FIGURE 3. INPUT PULSE TRAIN |

FIGURE 4. RETRIGGERABLE MODE |

FIGURE 5. NON-RETRIGGERABLE MODE |

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PULSE WIDTH (A MODE) |

|

|

PULSE WIDTH |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(A MODE) |

||||

3

CD54HC4538, CD74HC4538, CD74HCT4538

Absolute Maximum Ratings

DC Supply Voltage, VCC . . . . . . . . . . . . . . . . . . . . . . . . |

-0.5V to 7V |

DC Input Diode Current, IIK |

±20mA |

For VI < -0.5V or VI > VCC + 0.5V . . . . . . . . . . . . . . . . . . |

|

DC Output Diode Current, IOK |

±20mA |

For VO < -0.5V or VO > VCC + 0.5V . . . . . . . . . . . . . . . . |

|

DC Output Source or Sink Current per Output Pin, IO |

±25mA |

For VO > -0.5V or VO < VCC + 0.5V . . . . . . . . . . . . . . . . |

|

DC VCC or Ground Current, ICC . . . . . . . . . . . . . . . . . . . . . |

. . . .±50mA |

Thermal Information

Thermal Resistance (Typical, Note 7) |

θJA (oC/W) |

θJC (oC/W) |

|

PDIP Package . . . . . . . . . . . . . . . . . . . |

|

90 |

N/A |

SOIC Package . . . . . . . . . . . . . . . . . . . |

|

160 |

N/A |

CERDIP Package . . . . . . . . . . . . . . . . |

|

130 |

55 |

Maximum Junction Temperature . . . . . . . . |

. . . |

. . . . . . . . |

. . . . 150oC |

Maximum Storage Temperature Range . . . |

. . . |

. . . .-65oC to 150oC |

|

Maximum Lead Temperature (Soldering 10s) . . |

. . . . . . . |

. . . . 300oC |

|

(SOIC - Lead Tips Only)

Operating Conditions

Temperature Range, TA . . . . . . . . . . . . . . . . . . . . . . -55oC to 125oC Supply Voltage Range, VCC (Note 5)

HC Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2V to 6V HCT Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4.5V to 5.5V

DC Input or Output Voltage, VI, VO . . . . . . . . . . . . . . . . . 0V to VCC Input Rise and Fall Times, tr, tf

Reset Input:

2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1000ns (Max) 4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500ns (Max) 6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400ns (Max)

Trigger Inputs A or B:

2V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Unlimited (Max) 4.5V. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Unlimited (Max) 6V . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Unlimited (Max)

External Timing Resistor, RX (Note 6) . . . . . . . . . . . . . . . .5kΩ (Min) External Timing Capacitor, CX (Note 6) . . . . . . . . . . . . . . . . . 0 (Min)

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

NOTES:

5.Unless otherwise specified, all voltages are referenced to ground.

6.The maximum allowable values of RX and CX are a function of leakage of capacitor CX, the leakage of the HC4538, and leakage due to

board layout and surface resistance. Values of RX and CX should be chosen so that the maximum current into pin 2 or pin 14 is 30mA. Susceptibility to externally induced noise signals may occur for RX > 1MΩ.

7.θJA is measured with the component mounted on an evaluation PC board in free air.

DC Electrical Specifications

|

|

TEST |

|

|

25oC |

|

-40oC TO 85oC |

-55oC TO 125oC |

|

|||

|

|

CONDITIONS |

VCC |

|

|

|

||||||

PARAMETER |

SYMBOL |

VI (V) |

IO (mA) |

(V) |

MIN |

TYP |

MAX |

MIN |

MAX |

MIN |

MAX |

UNITS |

HC TYPES |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

High Level Input |

VIH |

- |

- |

2 |

1.5 |

- |

- |

1.5 |

- |

1.5 |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

3.15 |

- |

- |

3.15 |

- |

3.15 |

- |

V |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

4.2 |

- |

- |

4.2 |

- |

4.2 |

- |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

Low Level Input |

VIL |

- |

- |

2 |

- |

- |

0.5 |

- |

0.5 |

- |

0.5 |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

4.5 |

- |

- |

1.35 |

- |

1.35 |

- |

1.35 |

V |

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

- |

- |

1.8 |

- |

1.8 |

- |

1.8 |

V |

|

|

|

|

|

|

|

|

|

|

|

|

|

High Level Output |

VOH |

VIH or VIL |

-0.02 |

2 |

1.9 |

- |

- |

1.9 |

- |

1.9 |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-0.02 |

4.5 |

4.4 |

- |

- |

4.4 |

- |

4.4 |

- |

V |

|

CMOS Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-0.02 |

6 |

5.9 |

- |

- |

5.9 |

- |

5.9 |

- |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

High Level Output |

|

|

- |

- |

- |

- |

- |

- |

- |

- |

- |

V |

Voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-4 |

4.5 |

3.98 |

- |

- |

3.84 |

- |

3.7 |

- |

V |

|

TTL Loads |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-5.2 |

6 |

5.48 |

- |

- |

5.34 |

- |

5.2 |

- |

V |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

4

Loading...

Loading...