Texas Instruments CD74HCT393M96, CD74HCT393M, CD74HCT393E, CD74HC393M96, CD74HC393M Datasheet

...

[ /Title (CD74 HC393

,

CD74

HCT39

3) /Subject (High Speed CMOS

Data sheet acquired from Harris Semiconductor SCHS186

September 1997

CD74HC393,

CD74HCT393

High Speed CMOS Logic

Dual 4 -Stage Binary Counter

Features

•Fully Static Operation

•Buffered Inputs

•Common Reset

•Negative-Edge Clocking

•Typical fMAX = 60 MHz at VCC = 5V, CL = 15pF, TA = 25oC

•Fanout (Over Temperature Range)

-Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads

-Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

•Wide Operating Temperature Range . . . -55oC to 125oC

•Balanced Propagation Delay and Transition Times

•Significant Power Reduction Compared to LSTTL Logic ICs

•HC Types

-2V to 6V Operation

-High Noise Immunity: NIL = 30%, NIH = 30%of VCC at

VCC = 5V

•HCT Types

-4.5V to 5.5V Operation

-Direct LSTTL Input Logic Compatibility, VIL= 0.8V (Max), VIH = 2V (Min)

-CMOS Input Compatibility, Il ≤ 1μA at VOL, VOH

Description

The Harris CD74HC393 and CD74HCT393 are 4-stage ripple-carry binary counters. Al counter stages are masterslave flip-flops. The state of the stage advances one count on the negative transition of each clock pulse; a high voltage level on the MR line resets all counters to their zero state. All inputs and outputs are buffered.

Ordering Information

|

TEMP. RANGE (oC) |

|

PKG. |

PART NUMBER |

PACKAGE |

NO. |

|

CD74HC393E |

-55 to 125 |

14 Ld PDIP |

E14.3 |

|

|

|

|

CD74HCT393E |

-55 to 125 |

14 Ld PDIP |

E14.3 |

|

|

|

|

Pinout

CD74HC393, CD74HCT393

(PDIP, SOIC)

TOP VIEW

|

1CP |

|

1 |

|

14 |

|

VCC |

|

1MR |

|

|

|

|

|

|

||

|

2 |

|

13 |

|

2CP |

|

||

|

1Q0 |

|

|

|

|

2MR |

||

|

|

3 |

|

12 |

|

|||

|

1Q1 |

|

|

|

|

2Q0 |

||

|

|

4 |

|

11 |

|

|||

|

1Q2 |

|

|

|

|

2Q1 |

||

|

|

5 |

|

10 |

|

|||

|

1Q3 |

|

|

|

|

2Q2 |

||

|

|

6 |

|

9 |

|

|||

GND |

|

|

|

|

2Q3 |

|||

|

7 |

|

8 |

|

||||

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. |

File Number 1653.1 |

|

|

||

Copyright © Harris Corporation 1997 |

1 |

|

|

|

|

CD74HC393, CD74HCT393

Functional Diagram

|

|

1 |

|

|

|

3 |

1Q0 |

|

|

|

|

|

|

4 |

|||

|

|

|

|

|

|

|||

1CP |

|

|

|

BINARY |

|

|

1Q1 |

|

2 |

|

|

5 |

|||||

1MR |

|

COUNTER |

|

1Q2 |

||||

|

|

|

|

|

||||

|

|

|

|

|

6 |

|||

|

|

|

|

|

|

|

1Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

11 |

|

|

|

13 |

|

|

|

2Q0 |

||

|

|

|

|

|

||||

|

|

|

|

|||||

|

|

|

|

|

|

|||

|

|

|

|

|

10 |

|||

|

|

|

|

|

|

|||

2CP |

|

|

|

BINARY |

|

2Q1 |

||

|

|

|

|

|

||||

12 |

|

|

9 |

|||||

|

|

|

|

|||||

2MR |

|

COUNTER |

|

|

||||

|

|

|

|

2Q2 |

||||

|

|

|

|

|

||||

|

|

|

|

|

8 |

|||

|

|

|

|

|

|

|

2Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND = 7 |

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

VCC = 14 |

|

TRUTH TABLE

|

|

|

OUTPUTS |

|

|

|

|

|

|

|

|

CP COUNT |

Q0 |

Q1 |

|

Q2 |

Q3 |

0 |

L |

L |

|

L |

L |

|

|

|

|

|

|

1 |

H |

L |

|

L |

L |

|

|

|

|

|

|

2 |

L |

H |

|

L |

L |

|

|

|

|

|

|

3 |

H |

H |

|

L |

L |

|

|

|

|

|

|

4 |

L |

L |

|

H |

L |

|

|

|

|

|

|

5 |

H |

L |

|

H |

L |

|

|

|

|

|

|

6 |

L |

H |

|

H |

L |

|

|

|

|

|

|

7 |

H |

H |

|

H |

L |

|

|

|

|

|

|

8 |

L |

L |

|

L |

H |

|

|

|

|

|

|

9 |

H |

L |

|

L |

H |

|

|

|

|

|

|

10 |

L |

H |

|

L |

H |

|

|

|

|

|

|

11 |

H |

H |

|

L |

H |

|

|

|

|

|

|

12 |

L |

L |

|

H |

H |

|

|

|

|

|

|

13 |

H |

L |

|

H |

H |

|

|

|

|

|

|

14 |

L |

H |

|

H |

H |

|

|

|

|

|

|

15 |

H |

H |

|

H |

H |

|

|

|

|

|

|

|

|

|

|

|

|

CP COUNT |

MR |

|

|

OUTPUT |

|

|

|

|

|

|

|

− |

L |

|

|

No Change |

|

|

|

|

|

|

|

↓ |

L |

|

|

Count |

|

|

|

|

|

|

|

X |

H |

|

|

L L L L |

|

|

|

|

|

|

|

NOTE: H = High Voltage Level, L = Low Voltage Level, X = Don’t Care, − = Transition from Low to High Level, ↓ = Transition from High to Low.

2

|

|

|

CD74HC393, CD74HCT393 |

|

|

|||

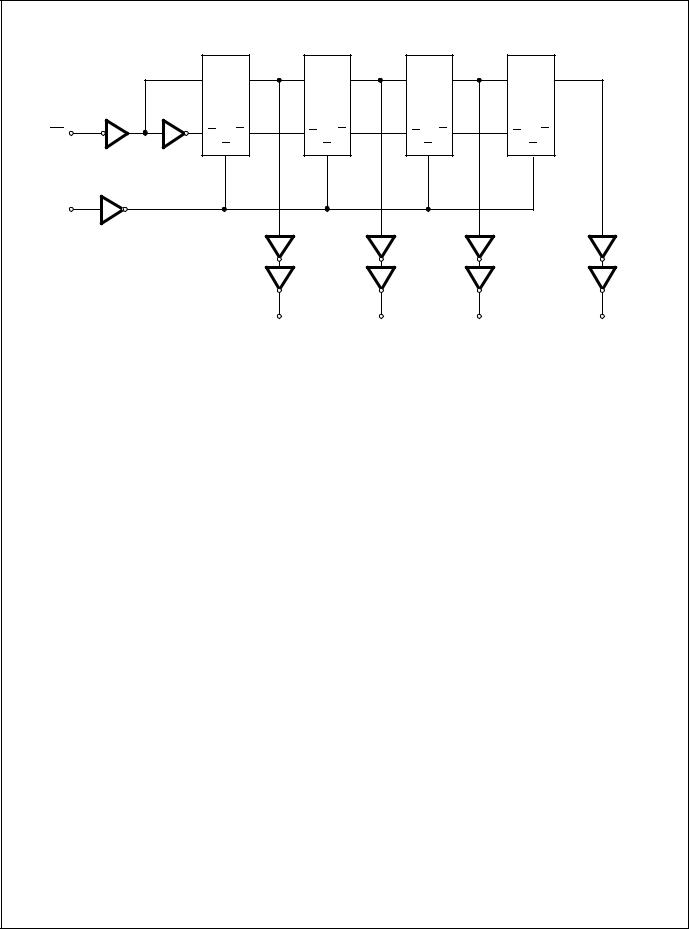

Logic Diagram |

|

|

|

|

|

|

|

|

|

Φ |

Q |

Φ |

Q |

Φ |

Q |

Φ |

Q |

1(13) |

|

|

|

|

|

|

|

|

CP |

Φ |

Q |

Φ |

Q |

Φ |

Q |

Φ |

Q |

|

|

R |

|

R |

|

R |

|

R |

2(12) |

|

|

|

|

|

|

|

|

MR |

|

|

|

|

|

|

|

|

|

|

|

3(11) |

|

4(10) |

|

5(9) |

6(8) |

|

|

|

Q0 |

|

Q1 |

|

Q2 |

Q3 |

|

|

|

|

3 |

|

|

|

|

Loading...

Loading...