Texas Instruments CD74HCT32M96, CD74HCT32M, CD74HCT32E, CD74HC32M96, CD74HC32M Datasheet

...

[ /Title (CD54 HCT32

,

CD74

HC32,

CD74

HCT32

)

/Subject (High

Data sheet acquired from Harris Semiconductor SCHS274

September 1997

CD54HCT32, CD74HC32, CD74HCT32

High Speed CMOS Logic

Quad 2-Input OR Gate

Features

•Typical Propagation Delay: 7ns at VCC = 5V, CL = 15pF, TA = 25oC

•Fanout (Over Temperature Range)

-Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads

-Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads

•Wide Operating Temperature Range . . . -55oC to 125oC

•Balanced Propagation Delay and Transition Times

•Significant Power Reduction Compared to LSTTL Logic ICs

•HC Types

-2V to 6V Operation

-High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

•HCT Types

-4.5V to 5.5V Operation

-Direct LSTTL Input Logic Compatibility, VIL= 0.8V (Max), VIH = 2V (Min)

-CMOS Input Compatibility, Il ≤ 1μA at VOL, VOH

•Related Literature

-CD54HC32F3A and CD54HCT32F3A Military Data Sheet, Document Number 3765

Description

The Harris CD74HC32, CD74HCT32 contain four 2-input OR gates in one package. Logic gates utilize silicon gate CMOS technology to achieve operating speeds similar to LSTTL gates with the low power consumption of standard CMOS integrated circuits. All devices have the ability to drive 10 LSTTL loads. The 74HCT logic family is functionally pin compatible with the standard 74LS logic family.

Ordering Information

|

TEMP. RANGE |

|

PKG. |

PART NUMBER |

(oC) |

PACKAGE |

NO. |

CD74HC32E |

-55 to 125 |

14 Ld PDIP |

E14.3 |

|

|

|

|

CD74HCT32E |

-55 to 125 |

14 Ld PDIP |

E14.3 |

|

|

|

|

CD74HC32M |

-55 to 125 |

14 Ld SOIC |

M14.15 |

|

|

|

|

CD74HCT32M |

-55 to 125 |

14 Ld SOIC |

M14.15 |

|

|

|

|

CD54HCT32F |

-55 to 125 |

14 Ld CERDIP |

F14.3 |

|

|

|

|

CD54HC32W |

-55 to 125 |

Wafer |

|

|

|

|

|

NOTES: |

|

|

|

1.When ordering, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

2.Die for this part number is available which meets all electrical specifications. Please contact your local sales office or Harris customer service for ordering information.

Pinout

CD54HCT32, CD74HC32, CD74HCT32

(PDIP, CERDIP, SOIC)

TOP VIEW

1A |

1 |

|

14 |

VCC |

1B |

|

|

|

4B |

2 |

|

13 |

||

1Y |

|

|

|

4A |

3 |

|

12 |

||

2A |

|

|

|

4Y |

4 |

|

11 |

||

2B |

|

|

|

3B |

5 |

|

10 |

||

2Y |

|

|

|

3A |

6 |

|

9 |

||

GND |

|

|

|

3Y |

7 |

|

8 |

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. |

File Number 1643.2 |

|

|

||

Copyright © Harris Corporation 1997 |

1 |

|

|

|

|

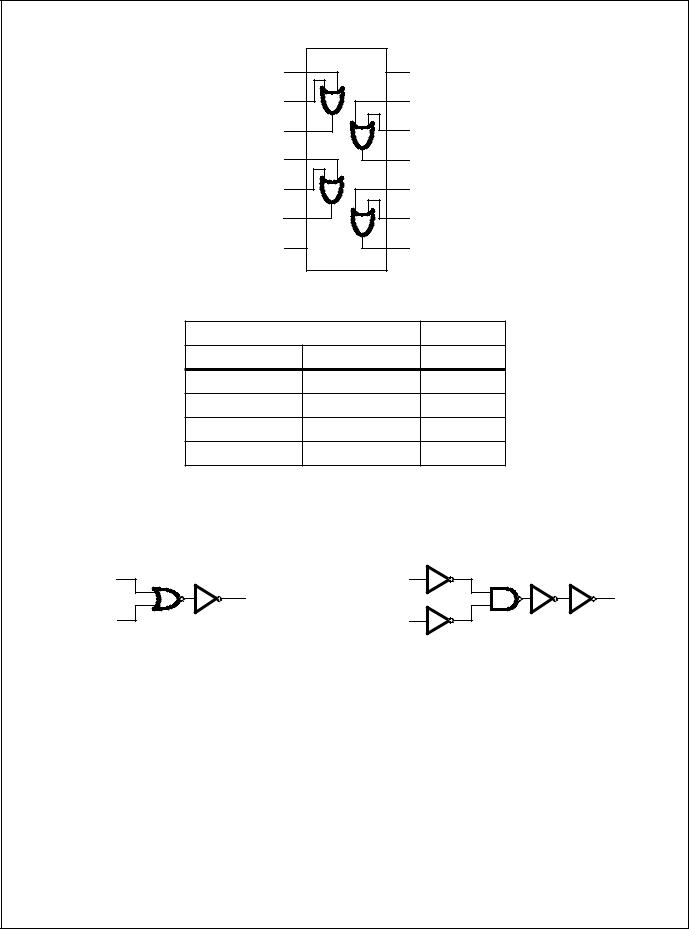

CD54HCT32, CD74HC32, CD74HCT32

Functional Diagram

1 |

14 |

|

1A |

VCC |

|

2 |

13 |

|

1B |

4B |

|

3 |

12 |

|

1Y |

4A |

|

4 |

11 |

|

2A |

4Y |

|

5 |

10 |

|

2B |

3B |

|

6 |

9 |

|

2Y |

3A |

|

7 |

8 |

|

GND |

3Y |

|

TRUTH TABLE |

|

|

INPUTS |

|

OUTPUT |

nA |

nB |

nY |

L |

L |

L |

L |

H |

H |

H |

L |

H |

H |

H |

H |

NOTE: H = High Voltage Level, L = Low Voltage Level |

|

|

HC Logic Symbol |

HCT Logic Symbol |

|

nA |

nA |

|

nY |

|

nY |

nB |

nB |

|

2

Loading...

Loading...