Texas Instruments CD74HCT139M96, CD74HCT139M, CD74HCT139E, CD74HC139M96, CD74HC139M Datasheet

...

Data sheet acquired from Harris Semiconductor SCHS148A

September 1997 - Revised May 1999

CD74HC139,

CD74HCT139

High-Speed CMOS Logic

Dual 2-to-4 Line Decoder/Demultiplexer

|

Features |

Description |

|

|

|

|

|

|

|

|

||

|

• |

Multifunction Capability |

The CD74HC139 and CD74HCT139 devices contain two |

|||||||||

[ /Title |

|

- Binary to 1 of 4 Decoders or 1 to 4 Line |

independent binary to one of four decoders each with a |

|||||||||

|

Demultiplexer |

single active low enable input |

(1E |

or |

2E) |

. Data on the select |

||||||

(CD74 |

• |

Active Low Mutually Exclusive Outputs |

inputs (1A0 and 1A1 or 2A0 and 2A1) cause one of the four |

|||||||||

HC139 |

normally high outputs to go low. |

|

|

|

||||||||

|

|

|

|

|

||||||||

• |

Fanout (Over Temperature Range) |

|

|

|

|

|

|

|

|

|

||

, |

If the enable input is high all four outputs remain high. For |

|||||||||||

|

- Standard Outputs . . . . . . . . . . . . . . . 10 LSTTL Loads |

|||||||||||

CD74 |

|

demultiplexer operation the enable input is the data input. |

||||||||||

|

- Bus Driver Outputs . . . . . . . . . . . . . 15 LSTTL Loads |

The enable input also functions as a chip select when these |

||||||||||

HCT13 |

|

|||||||||||

• Wide Operating Temperature Range . . . -55oC to 125oC |

devices are cascaded. This device is functionally the same |

|||||||||||

9) |

as the CD4556B and is pin compatible with it. |

|

||||||||||

|

|

|

||||||||||

/Sub- |

• |

Balanced Propagation Delay and Transition Times |

The outputs of these devices can drive 10 low power |

|||||||||

ject |

• |

Significant Power Reduction Compared to LSTTL |

Schottky TTL equivalent loads. The 74HCT logic family is |

|||||||||

(High |

|

Logic ICs |

functionally as well as pin equivalent to the 74LS logic family. |

|||||||||

Speed |

• HC Types |

Ordering Information |

|

|

|

|||||||

CMOS |

|

- 2V to 6V Operation |

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|||

Logic |

|

- High Noise Immunity: NIL = 30%, NIH = 30%of VCC at |

|

TEMP. RANGE (oC) |

|

|

|

PKG. |

||||

Dual |

|

VCC = 5V |

PART NUMBER |

|

PACKAGE |

NO. |

||||||

2-to-4 |

• HCT Types |

CD74HC139E |

-55 to 125 |

|

16 Ld PDIP |

E16.3 |

||||||

Line |

|

- 4.5V to 5.5V Operation |

|

|

|

|

|

|||||

|

CD74HCT139E |

-55 to 125 |

|

16 Ld PDIP |

E16.3 |

|||||||

Decod |

|

- Direct LSTTL Input Logic Compatibility, |

|

|

|

|

|

|

|

|

|

|

|

CD74HC139M |

-55 to 125 |

|

16 Ld SOIC |

M16.15 |

|||||||

|

|

VIL= 0.8V (Max), VIH = 2V (Min) |

|

|||||||||

|

|

- CMOS Input Compatibility, Il ≤ 1μA at VOL, VOH |

|

|

|

|

|

|||||

|

|

CD74HCT139M |

-55 to 125 |

|

16 Ld SOIC |

M16.15 |

||||||

|

• |

Memory Decoding, Data Routing, Code Conversion |

|

|

|

|

|

|

|

|

|

|

|

NOTES: |

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

1. When ordering, use the entire part number. Add the suffix 96 to |

|||||||||

|

|

|

obtain the variant in the tape and reel. |

|

|

|

||||||

|

|

|

2. Die is available which meets all electrical specifications. Please |

|||||||||

|

|

|

contact your local sales office or customer service for ordering |

|||||||||

|

|

|

information. |

|

|

|

|

|

|

|

|

|

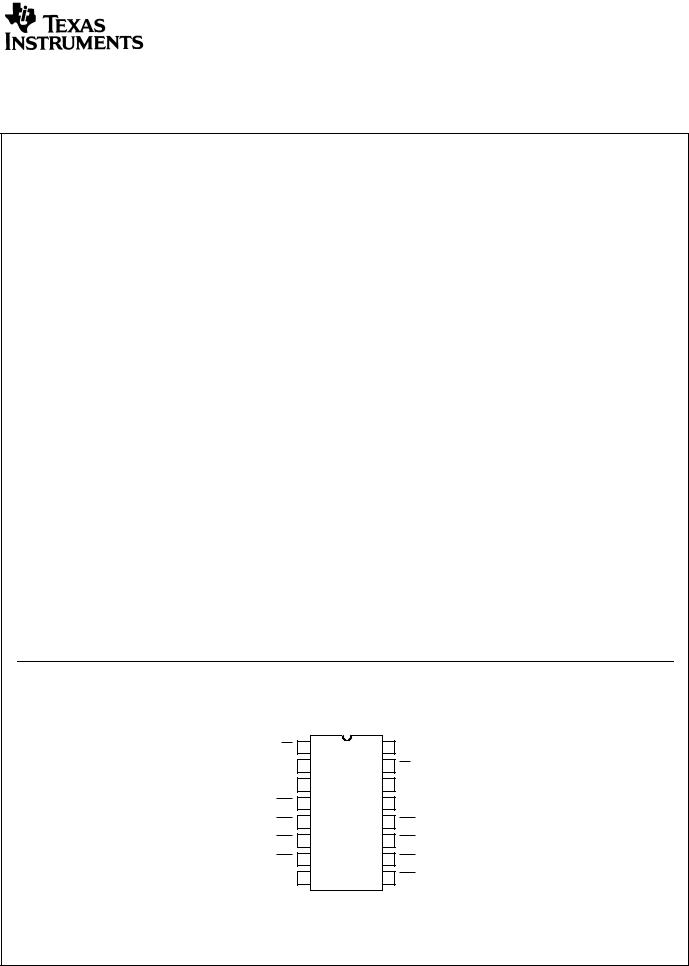

Pinout

CD74HC139, CD74HCT139

(PDIP, SOIC)

TOP VIEW

1E |

1 |

16 VCC |

1A0 |

2 |

15 |

2E |

1A1 |

3 |

14 |

2A0 |

1Y0 |

4 |

13 |

2A1 |

1Y1 |

5 |

12 |

2Y0 |

1Y2 |

6 |

11 |

2Y1 |

1Y3 |

7 |

10 |

2Y2 |

GND |

8 |

9 |

2Y3 |

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright © Texas Instruments Incorporated 1999

1

CD74HC139, CD74HCT139

Functional Diagram

|

|

|

|

|

|

|

4 |

(12) |

|

|

2 (14) |

|

|

|

|

|

Y0 |

||||

|

|

5 |

(11) |

|||||||

|

|

|

||||||||

A0 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

Y1 |

|||

3 (13) |

|

|

6 |

(10) |

||||||

|

|

|

||||||||

|

|

|

|

|

Y2 |

|||||

A1 |

|

|

|

|

7 |

(9) |

|

|||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

||

1 |

(15) |

|

|

|

|

|

Y3 |

|||

|

|

|

|

|||||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

E |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

TRUTH TABLE

INPUTS ENABLE SELECT |

|

|

|

|

OUTPUTS |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A1 |

A0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

E |

Y3 |

Y2 |

Y1 |

Y0 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

0 |

|

0 |

0 |

|

1 |

|

1 |

|

1 |

|

0 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

0 |

|

0 |

1 |

|

1 |

|

1 |

|

0 |

|

1 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

0 |

|

1 |

0 |

|

1 |

|

0 |

|

1 |

|

1 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

0 |

|

1 |

1 |

|

0 |

|

1 |

|

1 |

|

1 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

1 |

|

X |

X |

|

1 |

|

1 |

|

1 |

|

1 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE: X = Don’t Care, Logic 1 = High, Logic 0 = Low

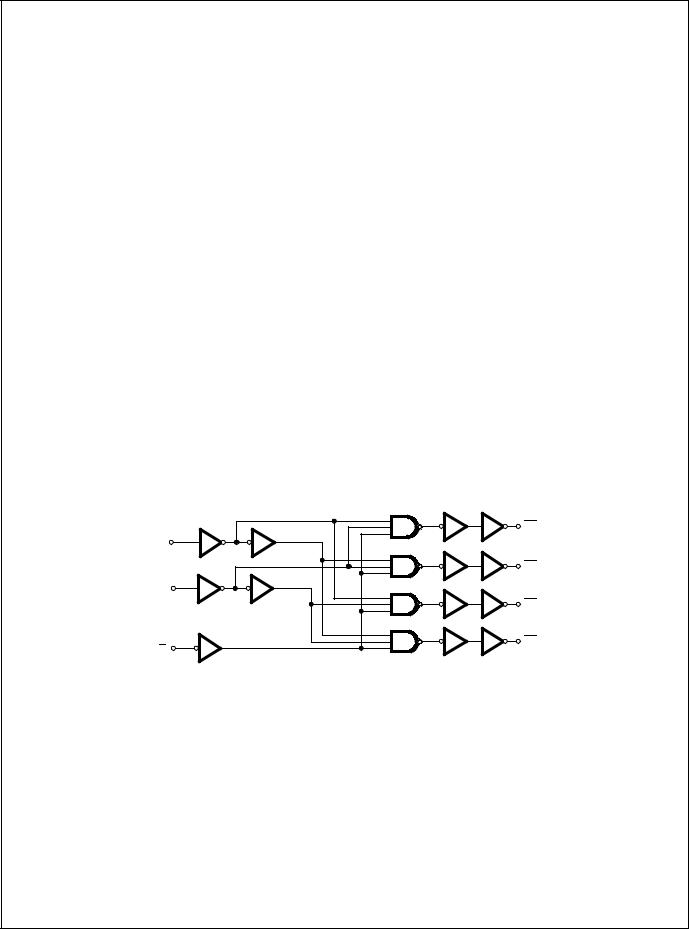

Logic Diagram

|

4 (12) |

|

2 (14) |

Y0 |

|

|

||

A0 |

5 (11) |

|

|

||

3 (13) |

Y1 |

|

|

||

A1 |

6 (10) |

|

|

||

|

Y2 |

|

1 (15) |

7 (9) |

|

Y3 |

||

E |

||

|

2

Loading...

Loading...