Texas Instruments CD74FCT244SM, CD74FCT244M96, CD74FCT244M, CD74FCT244E, CD74FCT244ATE Datasheet

...

1

Data sheet acquired from Harris Semiconductor

SCHS270A

Features

• CD54/74FCT240, CD54/74FCT240AT - Inverting

• CD54/74FCT241, CD54/74FCT244, CD54/74FCT244AT -

Non-Inverting

• Buffered Inputs

• Typical Propagation Delay:

4.1ns at VCC = 5V, TA = 25

o

C (FCT240AT, FCT244AT)

• SCR-Latchup-Resistant BiCMOS Process and Circuit

Design

• FCTXXX Types - Speed of Bipolar FAST®/AS/S;

FCTXXXAT Types - 30% Faster Than FAST/AS/S with

Significantly Reduced Power Consumption

• 48mA to 64mA Output Sink Current (Commer-

cial/Extended Industrial)

• Output Voltage Swing Limited to 3.7V at VCC = 5V

• Controlled Output-Edge Rates

• Input/Output Isolation to VCC

• BiCMOS Technology with Low Quiescent Power

Description

The CD54/74FCT240, 240AT, 241, 244 and 244AT three-

state octal buffers/line drivers use a small-geometry

BiCMOS technology. The output stage is a combination of

bipolar and CMOS transistors that limits the output-HIGH

level to two diode drops below VCC. This resultant lowering

of output swing (0V to 3.7V) reduces power bus ringing (a

source of EMI) and minimizes VCC bounce and ground

bounce and their effects during simultaneous output

switching. The output configuration also enhances switching

speed and is capable of sinking 48mA to 64mA.

The CD54/74FCT240, 240AT, 244 and 244AT have active-

LOW output enables (

1OE, 2OE). The CD54/74FCT241 and

CD54/74FCT241AT have one active-LOW (

1OE) and one

active-HIGH (2OE) output enable.

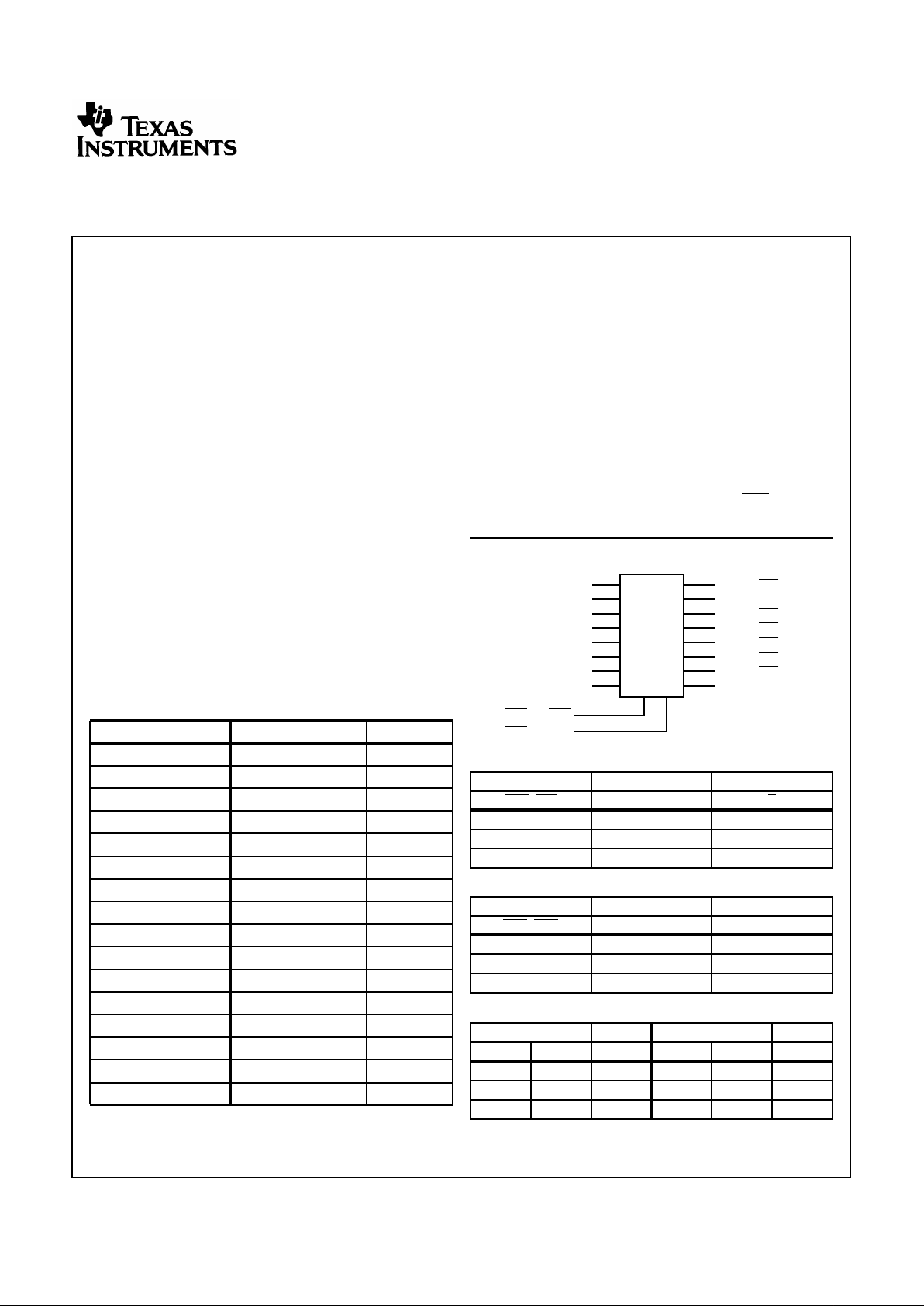

Functional Diagram

NOTE: H = High Voltage Level, L = LOW Voltage Level

X = Immaterial, Z = HIGH Impedance

Ordering Information

PART NUMBER TEMP. RANGE (

o

C) PACKAGE

CD54/74FCT240E -55 to 125, 0 to 70 20 Ld PDIP

CD54/74FCT240ATE -55 to 125, 0 to 70 20 Ld PDIP

CD54/74FCT241E -55 to 125, 0 to 70 20 Ld PDIP

CD54/74FCT244E -55 to 125, 0 to 70 20 Ld PDIP

CD54/74FCT244ATE -55 to 125, 0 to 70 20 Ld PDIP

CD54/74FCT240M -55 to 125, 0 to 70 20 Ld SOIC

CD54/74FCT240ATM -55 to 125, 0 to 70 20 Ld SOIC

CD54/74FCT241M -55 to 125, 0 to 70 20 Ld SOIC

CD54/74FCT244M -55 to 125, 0 to 70 20 Ld SOIC

CD54/74FCT244ATM -55 to 125, 0 to 70 20 Ld SOIC

CD54/74FCT240SM -55 to 125, 0 to 70 20 Ld SSOP

CD54/74FCT241SM -55 to 125, 0 to 70 20 Ld SSOP

CD54/74FCT244SM -55 to 125, 0 to 70 20 Ld SSOP

CD54FCT240H -55 to 125

CD54FCT241H -55 to 125

CD54FCT244H -55 to 125

CD54/74FCT240, CD54/74FCT240AT TRUTH TABLE

INPUT INPUT OUTPUT

1OE, 20E A Y

LLH

LHL

HXZ

CD54/74FCT244, CD54/74FCT244AT TRUTH TABLE

INPUT INPUT OUTPUT

1OE, 2OE A Y

LLH

LHL

HXZ

CD54/74FCT241 TRUTH TABLE

INPUT OUTPUT INPUT OUTPUT

1OE 1A 1Y 2OE 2A 2Y

LLLLXZ

LHHHLL

HXZHHH

18

16

14

12

9

7

5

3

2

4

6

8

11

13

15

17

119

1A0

1A1

1A2

1A3

2A0

2A1

2A2

2A3

1OE

2OE

1Y0

1Y1

1Y2

1Y3

2Y0

2Y1

2Y2

2Y3

1Y0

1Y1

1Y2

1Y3

2Y0

2Y1

2Y2

2Y3

241, 244 240

1OE

2OE

240, 244 241

VCC = 20

GND = 10

February 1996

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures.

Copyright

© Harris Corporation 1996

File Number 2227.3

CD54/74FCT240, CD54/74FCT240AT,

CD54/74FCT241, CD54/74FCT244,

CD54/74FCT244AT

FCT Interface Logic

Octal Buffers/Line Drivers, Three-State

FAST® is a registered trademark of Fairchild Semiconductor Corporation.

CD74FCT240AT and CD74FCT244AT were not acquired from Harris Semiconductor.

Loading...

Loading...