Texas Instruments CD74FCT574SM, CD74FCT574M96, CD74FCT574M, CD74FCT574E, CD74FCT564M Datasheet

...

Data sheet acquired from Harris Semiconductor

SCHS259

January 1997 |

|

RECOMMENDED |

|||

|

|

|

|

||

|

NOT |

|

NEW |

DESIGNS |

|

Features |

FOR |

echnology |

|||

|

|||||

CMOS |

T |

||||

|

Use |

|

|||

|

|

|

|||

•Buffered Inputs

•Typical Propagation Delay: 5.6ns at VCC = 5V, TA = 25oC

•Positive Edge Triggered

•CD74FCT564

-Inverting

•CD74FCT574

-Noninverting

•SCR Latchup Resistant BiCMOS Process and Circuit Design

•Speed of Bipolar FAST™/AS/S

•48mA Output Sink Current

•Output Voltage Swing Limited to 3.7V at VCC = 5V

•Controlled Output Edge Rates

•Input/Output Isolation to VCC

•BiCMOS Technology with Low Quiescent Power

CD74FCT564,

CD74FCT574

BiCMOS FCT Interface Logic,

Octal D-Type Flip-Flops, Three-State

Description

The CD74FCT564 and CD74FCT574 are octal D-Type, three-state, positive edge triggered flip-flops which use a small geometry BiCMOS technology. The output stage is a combination of bipolar and CMOS transistors that limits the output HIGH level to two diode drops below VCC. This resultant lowering of output swing (0V to 3.7V) reduces power bus ringing (a source of EMI) and minimizes VCC bounce and ground bounce and their effects during simultaneous output switching. The output configuration also enhances switching speed and is capable of sinking 48 milliamperes.

The eight flip-flops enter data into their registers on the LOW to HIGH transition of the clock (CP). The Output Enable (OE) controls the three state outputs and is independent of the register operation. When the Output Enable (OE) is HIGH, the outputs are in the high impedance state. The CD74FCT564 and CD74FCT574 share the same configurations; the CD74FCT564, however, has inverted outputs and the CD74FCT574 has noninverted outputs.

Ordering Information

|

TEMP. |

|

PKG. |

PART NUMBER |

RANGE (oC) |

PACKAGE |

NO. |

CD74FCT564E |

0 to 70 |

20 Ld PDIP |

E20.3 |

|

|

|

|

CD74FCT574E |

0 to 70 |

20 Ld PDIP |

E20.3 |

|

|

|

|

CD74FCT564M |

0 to 70 |

20 Ld SOIC |

M20.3 |

|

|

|

|

CD74FCT574M |

0 to 70 |

20 Ld SOIC |

M20.3 |

|

|

|

|

CD74FCT574SM |

0 to 70 |

20 Ld SSOP |

M20.209 |

|

|

|

|

NOTE: When ordering the suffix M and SM packages, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

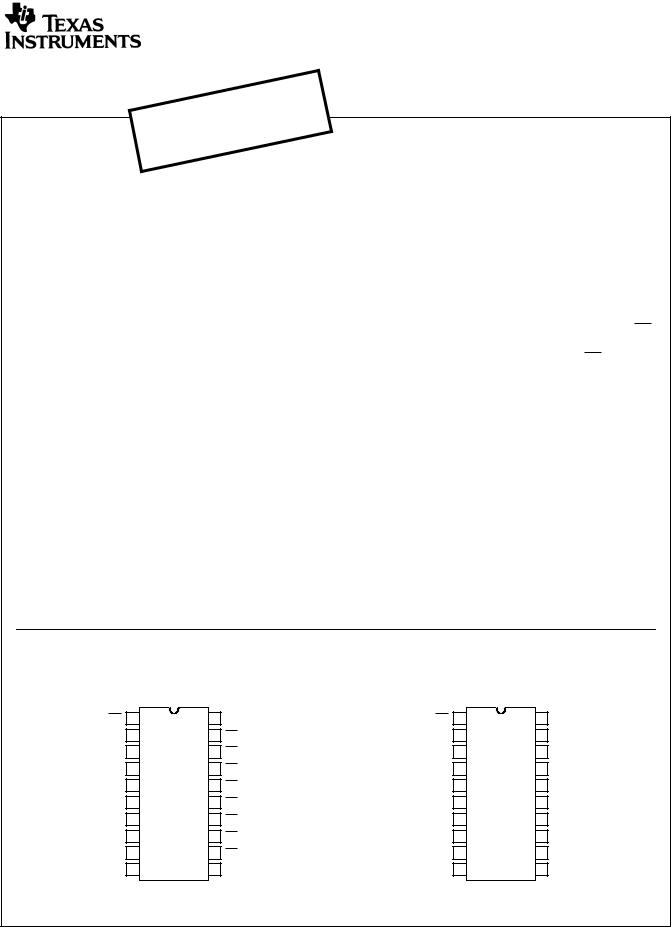

Pinouts

CD74FCT564 |

CD74FCT574 |

(PDIP, SOIC, SSOP) |

(PDIP, SOIC, SSOP) |

TOP VIEW |

TOP VIEW |

OE |

1 |

20 |

VCC |

D0 |

2 |

19 |

Q0 |

D1 |

3 |

18 |

Q1 |

D2 |

4 |

17 |

Q2 |

D3 |

5 |

16 |

Q3 |

D4 |

6 |

15 |

Q4 |

D5 |

7 |

14 |

Q5 |

D6 |

8 |

13 |

Q6 |

D7 |

9 |

12 |

Q7 |

GND |

10 |

11 CP |

OE |

1 |

20 |

VCC |

D0 |

2 |

19 |

Q0 |

D1 |

3 |

18 |

Q1 |

D2 |

4 |

17 |

Q2 |

D3 |

5 |

16 |

Q3 |

D4 |

6 |

15 |

Q4 |

D5 |

7 |

14 |

Q5 |

D6 |

8 |

13 |

Q6 |

D7 |

9 |

12 |

Q7 |

GND |

10 |

11 CP |

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. |

File Number 2295.2 |

|

|

||

FAST™ is a trademark of Fairchild Semiconductor. |

8-1 |

|

Copyright © Harris Corporation 1997 |

|

|

|

|

|

CD74FCT564, CD74FCT574

Functional Diagram

|

|

|

2 |

|

|

|

19 |

CD74FCT574 |

CD74FCT564 |

|

D0 |

|

|

|

|

Q0 |

Q0 |

||||

3 |

|

|

|

18 |

|

|||||

D1 |

|

|

|

|

Q1 |

Q1 |

||||

4 |

|

|

|

17 |

|

|||||

D2 |

|

|

|

|

Q2 |

Q2 |

||||

5 |

|

|

|

16 |

|

|||||

D3 |

|

|

|

|

Q3 |

Q3 |

||||

6 |

|

|

|

15 |

|

|||||

D4 |

|

|

|

|

Q4 |

Q4 |

||||

7 |

|

|

|

14 |

|

|||||

D5 |

|

|

|

|

Q5 |

Q5 |

||||

8 |

|

|

|

13 |

|

|||||

D6 |

|

|

|

|

Q6 |

Q6 |

||||

9 |

|

|

|

12 |

|

|||||

D7 |

|

|

|

|

Q7 |

Q7 |

||||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

11 |

|

|

|

|

|

|

OE |

|

|

GND = PIN 10 |

|

||||||

|

|

|

|

|

|

|||||

CP |

|

|

|

|

|

|

||||

|

|

|

|

|

VCC = PIN 20 |

|

||||

|

|

|

|

|

|

|||||

TRUTH TABLE (NOTE 1)

|

|

|

|

|

|

|

OUTPUTS |

|

|

|

|

|

|

|

|

||

|

|

|

INPUTS |

|

CD74FCT564 |

CD74FCT574 |

||

|

|

|

|

|

|

|

|

|

|

|

|

CP |

DN |

|

|

|

QN |

|

OE |

QN |

||||||

|

|

|

|

|

|

|

||

|

L |

− |

H |

|

L |

H |

||

|

|

|

|

|

|

|

||

|

L |

− |

L |

|

H |

L |

||

|

|

|

|

|

|

|

||

|

L |

L |

X |

|

Qo |

Qo |

||

|

|

|

|

|

|

|

||

|

H |

X |

X |

|

Z |

Z |

||

|

|

|

|

|

|

|

|

|

NOTE:

1. H = High Level (Steady State) L = Low Level (Steady State) X = Don't Care

− = Transition from low to high level

Qo = The level of Q before the indicated steady state input conditions were established.

Z = HIGH Impedance

IEC Logic Symbols

|

CD74FCT564 |

|

|

CD74FCT574 |

|

|||||||

1 |

|

|

EN |

|

1 |

|

|

EN |

|

|||

11 |

|

|

|

11 |

|

|

|

|||||

|

|

>C1 |

|

|

|

>C1 |

|

|||||

2 |

|

|

1D |

19 |

2 |

|

|

1D |

19 |

|||

|

|

|

|

|

|

|

|

|||||

3 |

|

|

|

|

18 |

3 |

|

|

|

|

|

18 |

4 |

|

|

|

|

17 |

4 |

|

|

|

|

|

17 |

5 |

|

|

|

|

16 |

5 |

|

|

|

|

|

16 |

6 |

|

|

|

|

15 |

6 |

|

|

|

|

|

15 |

|

|

|

|

|

|

|

|

|

||||

7 |

|

|

|

|

14 |

7 |

|

|

|

|

|

14 |

|

|

|

|

|

|

|

|

|

||||

8 |

|

|

|

|

13 |

8 |

|

|

|

|

|

13 |

|

|

|

|

|

|

|

|

|

||||

9 |

|

|

|

|

12 |

9 |

|

|

|

|

|

12 |

|

|

|

|

|

|

|

|

|

||||

8-2

Loading...

Loading...