Texas Instruments CD74FCT842AM96, CD74FCT842AM, CD74FCT841AM96, CD74FCT841AM, CD74FCT841AEN Datasheet

Data sheet acquired from Harris Semiconductor

SCHS266

January 1997 |

T RECOMMENDED |

||

|

|

|

|

|

NO |

NEW |

DESIGNS |

|

FOR |

echnology |

|

|

|

||

Features |

CMOS |

T |

|

Use |

|

||

|

|

|

|

•Buffered Inputs

•Typical Propagation Delay: 6.8ns at VCC = 5V, TA = 25oC, CL = 50pF (CD74FCT841A)

•CD74FCT841A

-Noninverting

•CD74FCT842A

-Inverting

•SCR Latchup Resistant BiCMOS Process and

Pinouts

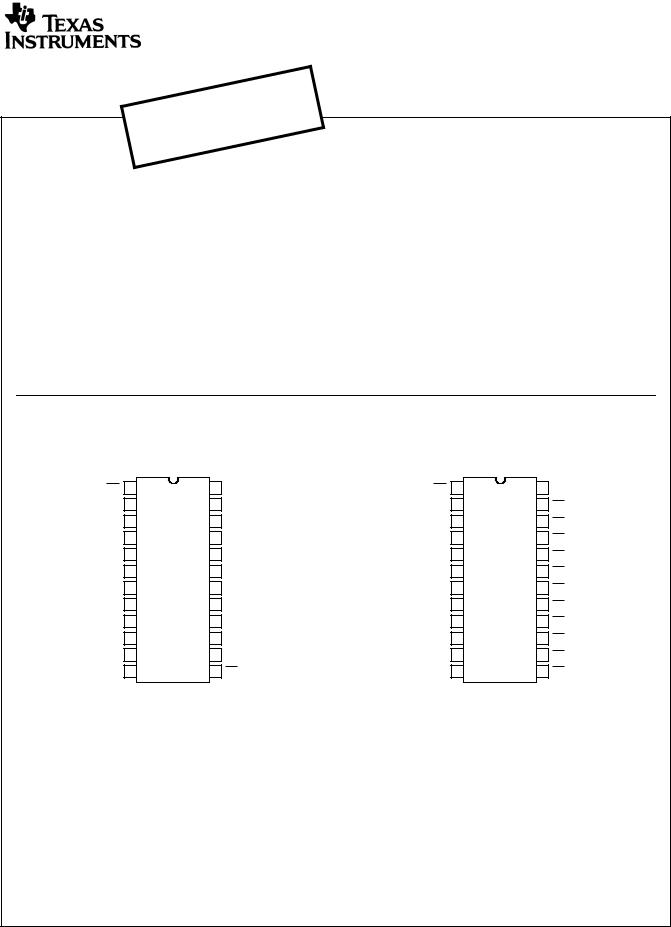

CD74FCT841A

(PDIP, SOIC)

TOP VIEW

OE |

1 |

24 |

VCC |

D0 |

2 |

23 |

Q0 |

D1 |

3 |

22 |

Q1 |

D2 |

4 |

21 |

Q2 |

D3 |

5 |

20 |

Q3 |

D4 |

6 |

19 |

Q4 |

D5 |

7 |

18 |

Q5 |

D6 |

8 |

17 |

Q6 |

D7 |

9 |

16 |

Q7 |

D8 |

10 |

15 |

Q8 |

D9 |

11 |

14 |

Q9 |

GND 12 |

13 LE |

CD74FCT841A,

CD74FCT842A

BiCMOS FCT Interface Logic,

10-Bit Transparent Latches, Three-State

Circuit Design

•Speed of Bipolar FAST™/AS/S

•48mA Output Sink Current

•Output Voltage Swing Limited to 3.7V at VCC = 5V

•Controlled Output Edge Rates

•Input/Output Isolation to VCC

•BiCMOS Technology with Low Quiescent Power

Ordering Information

|

TEMP. |

|

PKG. |

PART NUMBER |

RANGE (oC) |

PACKAGE |

NO. |

CD74FCT841AEN |

0 to 70 |

24 Ld PDIP |

E24.3 |

|

|

|

|

CD74FCT841AM |

0 to 70 |

24 Ld SOIC |

M24.3 |

|

|

|

|

CD74FCT842AM |

0 to 70 |

24 Ld SOIC |

M24.3 |

NOTE: When ordering the suffix M packages, use the entire part number. Add the suffix 96 to obtain the variant in the tape and reel.

CD74FCT842A (PDIP, SOIC)

TOP VIEW

OE |

1 |

24 |

VCC |

D0 |

2 |

23 |

Q0 |

D1 |

3 |

22 |

Q1 |

D2 |

4 |

21 |

Q2 |

D3 |

5 |

20 |

Q3 |

D4 |

6 |

19 |

Q4 |

D5 |

7 |

18 |

Q5 |

D6 |

8 |

17 |

Q6 |

D7 |

9 |

16 |

Q7 |

D8 |

10 |

15 |

Q8 |

D9 |

11 |

14 |

Q9 |

GND 12 |

13 LE |

CAUTION: These devices are sensitive to electrostatic discharge. Users should follow proper IC Handling Procedures. |

File Number 2397.2 |

|

|

||

FAST™ is a trademark of Fairchild Semiconductor. |

8-1 |

|

Copyright © Harris Corporation 1997 |

|

|

|

|

|

Loading...

Loading...