Motorola MC10E143FN, MC10E143FNR2, MC100E143FNR2, MC100E143FN Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

9 Bit Hold Register

The MC10E/100E143 is a 9-bit holding register, designed with byte-parity applications in mind. The E143 holds current data or loads new data, with the nine inputs D0 ± D8 accepting parallel input data.

•700MHz Min. Operating Frequency

•9-Bit for Byte-Parity Applications

•Asynchronous Master Reset

•Dual Clocks

•Extended 100E VEE Range of ± 4.2V to ± 5.46V

•75kΩ Input Pulldown Resistors

MC10E143

MC100E143

9-BIT HOLD REGISTER

The SEL (Select) input pin is used to switch between the two modes of operation Ð HOLD and LOAD. Input data is accepted by the registers a set-up time before the positive going edge of CLK1 or CLK2. A HIGH on the Master Reset pin (MR) asynchronously resets all the registers to zero.

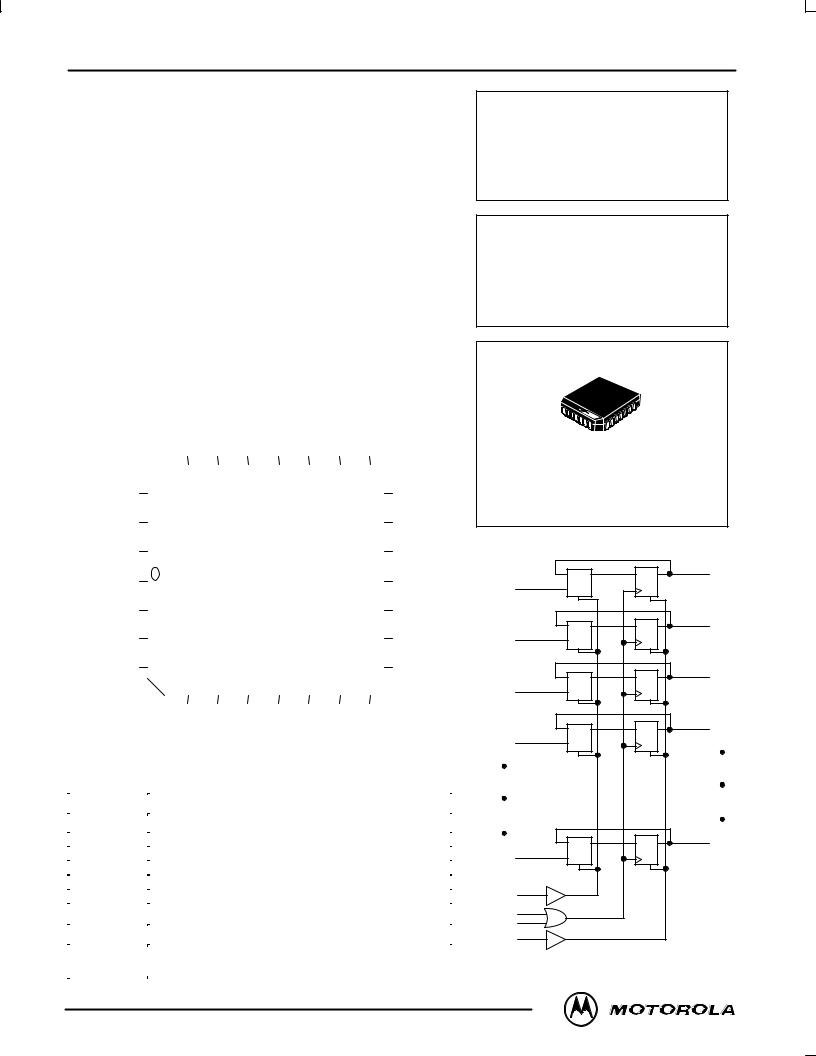

Pinout: 28-Lead PLCC (Top View)

|

|

|

|

SEL |

D8 |

|

D7 |

|

D6 |

D5 |

VCCO |

Q8 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MR |

|

|

25 |

|

24 |

23 |

22 |

|

21 |

20 |

|

19 |

|

|

|

||||

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|

Q7 |

||

CLK1 |

|

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|

Q6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

CLK2 |

|

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

VEE |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q5 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

NC |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCCO |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

D0 |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q4 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

D1 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q3 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

5 |

|

6 |

7 |

8 |

|

9 |

10 |

|

11 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D2 |

|

D3 |

|

D4 |

V |

CCO |

Q0 |

|

Q1 |

Q2 |

|

||||

|

* All VCC and VCCO pins are tied together on the die. |

|

|||||||||||||||||

PIN NAMES

Pin |

Function |

|

|

D0 ± D8 |

Parallel Data Inputs |

SEL |

Mode Select Input |

CLK1, CLK2 |

Clock Inputs |

MR |

Master Reset |

Q0 ± Q8 |

Data Outputs |

NC |

No Connection |

|

|

FUNCTIONS |

|

SEL |

Mode |

|

|

L |

Load |

H |

Hold |

|

|

FN SUFFIX

PLASTIC PACKAGE

CASE 776-02

LOGIC DIAGRAM |

||

MUX |

D |

Q0 |

|

R |

|

D0 |

|

|

MUX |

D |

Q1 |

|

R |

|

D1 |

|

|

MUX |

D |

Q2 |

|

R |

|

D2 |

|

|

MUX |

D |

Q3 |

|

R |

|

D3 |

|

|

MUX |

D |

Q8 |

|

R |

|

D8 |

|

|

SEL |

|

|

CLK1 |

|

|

CLK2 |

|

|

MR |

|

|

12/93

Motorola, Inc. 1996 |

REV 2 |

MC10E143 MC100E143

DC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

min typ |

max |

min |

typ |

max |

min |

typ |

max |

Unit |

Condition |

|

|

|

|

|

|

|

|

|

|

|

|

IIH |

Input HIGH Current |

|

150 |

|

|

150 |

|

|

150 |

μA |

|

IEE |

Power Supply Current |

|

|

|

|

|

|

|

|

mA |

|

|

10E |

120 |

145 |

|

120 |

145 |

|

120 |

145 |

|

|

|

100E |

120 |

145 |

|

120 |

145 |

|

138 |

165 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

min |

typ |

max |

min |

typ |

max |

min |

typ |

max |

Unit |

Condition |

|

|

|

|

|

|

|

|

|

|

|

|

|

fMAX |

Max. Toggle Frequency |

700 |

900 |

|

700 |

900 |

|

700 |

900 |

|

MHz |

|

tPLH |

Propagation Delay to Output |

|

|

|

|

|

|

|

|

|

ps |

|

tPHL |

Clk |

600 |

800 |

1000 |

600 |

800 |

1000 |

600 |

800 |

1000 |

|

|

|

MR |

600 |

800 |

1000 |

600 |

800 |

1000 |

600 |

800 |

1000 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ts |

Setup Time |

|

|

|

|

|

|

|

|

|

ps |

|

|

D |

50 |

±100 |

|

50 |

±100 |

|

50 |

±100 |

|

|

|

|

SEL |

300 |

150 |

|

300 |

150 |

|

300 |

150 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

th |

Hold Time |

|

|

|

|

|

|

|

|

|

ps |

|

|

D |

300 |

100 |

|

300 |

100 |

|

300 |

100 |

|

|

|

|

SEL |

75 |

±150 |

|

75 |

±150 |

|

75 |

±150 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tRR |

Reset Recovery Time |

900 |

700 |

|

900 |

700 |

|

900 |

700 |

|

ps |

|

tPW |

Minimum Pulse Width |

|

|

|

|

|

|

|

|

|

ps |

|

|

Clk, MR |

400 |

|

|

400 |

|

|

400 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tSKEW |

Within-Device Skew |

|

75 |

|

|

75 |

|

|

75 |

|

ps |

1 |

tr |

Rise/Fall Times |

|

|

|

|

|

|

|

|

|

ps |

|

tf |

20 - 80% |

300 |

525 |

800 |

300 |

525 |

800 |

300 |

525 |

800 |

|

|

1. Within-device skew is defined as identical transitions on similar paths through a device.

MOTOROLA |

2±2 |

Loading...

Loading...