Motorola MC10E112FN, MC100E112FN, MC100E112FNR2, MC10E112FNR2 Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

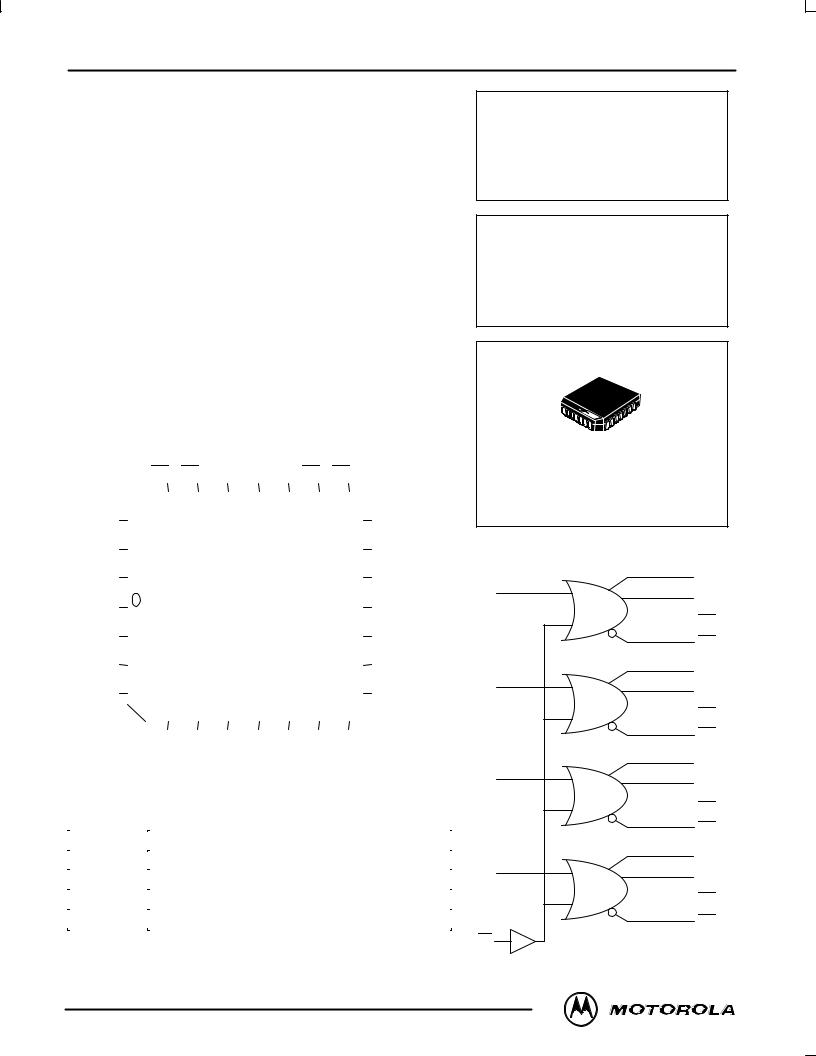

Quad Driver

The MC10E/100E112 is a quad driver with two pairs of OR/NOR outputs from each gate, and a common, buffered enable input. Using the data inputs the device can serve as an ECL memory address fan-out driver. Using just the enable input, the device serves as a clock driver, although the MC10E/100E111 is designed specifically for this purpose, and offers lower skew than the E112. For memory address driver applications where scan capabilities are required, please refer to the E212 device.

•600ps Max. Propagation Delay

•Common Enable Input

•Extended 100E VEE Range of ± 4.2V to ± 5.46V

•75kΩ Input Pulldown Resistors

Pinout: 28-Lead PLCC (Top View)

|

|

|

|

|

|

|

Q3b |

|

Q3a |

Q3b |

Q3a |

VCCO |

Q2b |

Q2a |

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCCO |

|

|

|

25 |

|

24 |

|

23 |

|

22 |

|

21 |

|

20 |

|

19 |

|

|

|

Q2b |

||||||||||

|

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|

|

|||||||

|

D3 |

|

|

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|

|

Q2a |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

D2 |

|

|

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

|

VCC |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

VEE |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1b |

||||||||

|

D1 |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1a |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

D0 |

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

|

Q1b |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

EN |

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

|

Q1a |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

5 |

|

6 |

|

7 |

|

8 |

|

9 |

|

10 |

|

11 |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

VCCO |

Q0a |

Q0b |

Q0a |

Q0b |

VCCO |

|

|

|

||||||||||||||

|

|

|

* All VCC and VCCO pins are tied together on the die. |

|

|

|

||||||||||||||||||||||||

PIN NAMES

|

|

|

Pin |

Function |

||

|

|

|

|

|

|

|

|

D0 ± D3 |

Data Inputs |

||||

|

EN |

|

Enable Input |

|||

|

Qna, Qnb |

True Outputs |

||||

|

|

|

|

|

|

|

|

Qna, Qnb |

Inverting Outputs |

||||

D0

D1

D2

D3

EN

MC10E112

MC100E112

QUAD DRIVER

FN SUFFIX

PLASTIC PACKAGE

CASE 776-02

LOGIC DIAGRAM

Q0a

Q0b

Q0a

Q0a

Q0b

Q1a

Q1b

Q1a

Q1a

Q1b

Q2a

Q2b

Q2a

Q2a

Q2b

Q3a

Q3b

Q3a

Q3a

Q3b

12/93

Motorola, Inc. 1996 |

REV 2 |

MC10E112 MC100E112

DC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

|

|

0°C |

|

|

25°C |

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

|

|

Characteristic |

min typ |

max |

min |

typ |

max |

min typ |

max |

Unit |

Condition |

|

|

|

|

|

|

|

|

|

|

|

|

|

IIH |

Input HIGH Current |

|

|

|

|

|

|

|

μA |

|

||

|

|

D |

|

|

200 |

|

|

200 |

|

200 |

|

|

|

|

EN |

|

200 |

|

|

200 |

|

200 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

IEE |

Power Supply Current |

|

|

|

|

|

|

|

mA |

|

||

|

|

10E |

47 |

56 |

|

47 |

56 |

47 |

56 |

|

|

|

|

|

100E |

47 |

56 |

|

47 |

56 |

54 |

65 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

|

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

|

|

Characteristic |

min |

typ |

max |

min |

typ |

max |

min |

typ |

max |

Unit |

Condition |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tPLH |

Propagation Delay to Output |

|

|

|

|

|

|

|

|

|

ps |

|

||

tPHL |

|

D |

|

200 |

400 |

600 |

200 |

400 |

600 |

200 |

400 |

600 |

|

|

|

|

EN |

275 |

450 |

675 |

275 |

450 |

675 |

275 |

450 |

675 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

tSKEW |

Within-Device Skew |

|

|

|

|

|

|

|

|

|

ps |

|

||

|

|

Dn to Qn, Qn |

|

80 |

|

|

80 |

|

|

80 |

|

|

1 |

|

|

|

Qna to Qnb |

|

40 |

|

|

40 |

|

|

40 |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

tr |

Rise/Fall Times |

|

|

|

|

|

|

|

|

|

ps |

|

||

tf |

20 - 80% |

275 |

425 |

700 |

275 |

425 |

700 |

275 |

425 |

700 |

|

|

||

1.Within-device skew is defined as identical transitions on similar paths through a device.

2.Skew defined between common OR or common NOR outputs of a single gate.

MOTOROLA |

2±2 |

Loading...

Loading...