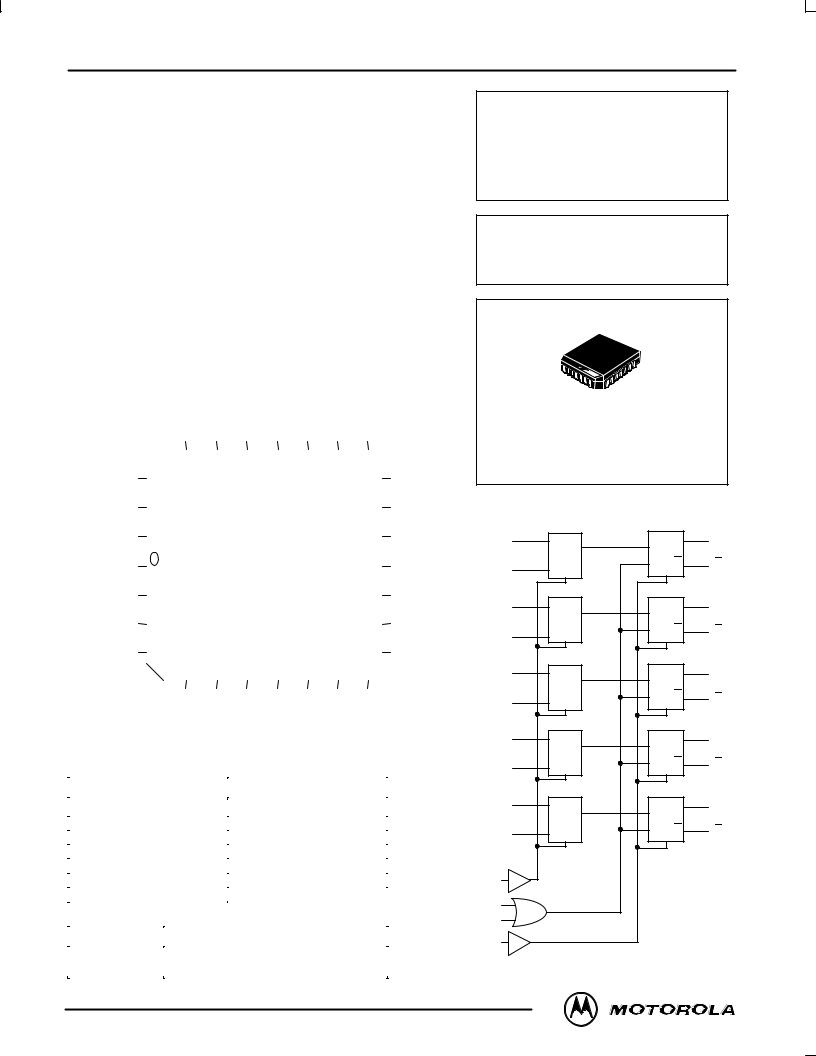

Motorola MC10E154FN, MC10E154FNR2, MC100E154FNR2, MC100E154FN Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

5 Bit 2:1 Mux Latch

The MC10E/100E154 contains five 2:1 multiplexers followed by transparent latches with differential outputs. When both Latch Enables (LEN1, LEN2) are LOW, the latch is transparent, and output data is controlled by the multiplexer select control, SEL. A logic HIGH on either LEN1 or LEN2 (or both) latches the outputs. The Master Reset (MR) overrides all other controls to set the Q outputs LOW.

•850ps Max. LEN to Output

•825ps Max. D to Output

•Differential Outputs

•Asynchronous Master Reset

•Dual Latch-Enables

•Extended 100E VEE Range of ± 4.2V to ± 5.46V

•75kΩ Input Pulldown Resistors

Pinout: 28-Lead PLCC (Top View)

|

|

|

|

D4b |

D4a |

D3b |

D3a |

VCCO |

Q4 |

|

Q4 |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SEL |

|

|

25 |

|

24 |

|

23 |

|

22 |

|

21 |

|

20 |

19 |

|

|

|

|

|

|

|||

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|

|

Q3 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

LEN1 |

|

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|

|

Q3 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

LEN2 |

|

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

|

VCC |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

VEE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

Q2 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

MR |

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

|

|

Q2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

D0a |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

|

Q1 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

D0b |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

|

Q1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

5 |

|

6 |

|

7 |

|

8 |

|

9 |

|

10 |

11 |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1a |

D1b |

D2a |

D2b |

VCCO |

Q0 |

|

Q0 |

|

|

||||||||||

|

* All VCC and VCCO pins are tied together on the die. |

|

|

||||||||||||||||||||

PIN NAMES

Pin |

Function |

|

|

D0a ± D4a |

Input Data a |

D0b ± D4b |

Input Data b |

SEL |

Data Select Input |

LEN1, LEN2 |

Latch Enables |

MR |

Master Reset |

Q0 ± Q4 |

True Outputs |

Q0 ± Q4 |

Inverted Outputs |

TRUTH TABLE |

|

SEL |

Data |

|

|

H |

a |

L |

b |

MC10E154

MC100E154

5-BIT 2:1

MUX-LATCH

FN SUFFIX

PLASTIC PACKAGE

CASE 776-02

LOGIC DIAGRAM

D0a |

MUX |

Q |

D |

||

D |

SEL |

ENR Q |

0b |

|

|

D1a |

MUX |

Q |

D |

||

D |

SEL |

ENR Q |

1b |

|

|

D2a |

MUX |

Q |

D |

||

D |

SEL |

ENR Q |

2b |

|

|

D3a |

MUX |

Q |

|

D |

|

D |

SEL |

ENR Q |

3b |

|

|

D4a |

MUX |

Q |

|

D |

|

D4b |

SEL |

ENR Q |

SEL |

|

|

LEN1 |

|

|

LEN2 |

|

|

MR |

|

|

12/93

Motorola, Inc. 1996 |

REV 2 |

Q0

Q0

Q1

Q1

Q2

Q2

Q3

Q3

Q4

Q4

MC10E154 MC100E154

DC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

min typ |

max |

min |

typ |

max |

min |

typ |

max |

Unit |

Condition |

|

|

|

|

|

|

|

|

|

|

|

|

IIH |

Input HIGH Current |

|

150 |

|

|

150 |

|

|

150 |

μA |

|

IEE |

Power Supply Current |

|

|

|

|

|

|

|

|

mA |

|

|

10E |

76 |

91 |

|

76 |

91 |

|

76 |

91 |

|

|

|

100E |

76 |

91 |

|

76 |

91 |

|

87 |

105 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

min |

typ |

max |

min |

typ |

max |

min |

typ |

max |

Unit |

Condition |

|

|

|

|

|

|

|

|

|

|

|

|

|

tPLH |

Propagation Delay to Output |

|

|

|

|

|

|

|

|

|

ps |

|

tPHL |

D |

325 |

500 |

700 |

325 |

500 |

700 |

325 |

500 |

700 |

|

|

|

SEL |

475 |

650 |

925 |

475 |

650 |

925 |

475 |

650 |

925 |

|

|

|

LEN |

350 |

500 |

750 |

350 |

500 |

750 |

350 |

500 |

750 |

|

|

|

MR |

450 |

600 |

800 |

450 |

600 |

800 |

450 |

600 |

800 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ts |

Setup Time |

|

|

|

|

|

|

|

|

|

ps |

|

|

D |

300 |

100 |

|

300 |

100 |

|

300 |

100 |

|

|

|

|

SEL |

500 |

250 |

|

500 |

250 |

|

500 |

250 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

th |

Hold Time |

|

|

|

|

|

|

|

|

|

ps |

|

|

D |

300 |

±100 |

|

300 |

±100 |

|

300 |

±100 |

|

|

|

|

SEL |

200 |

± 250 |

|

200 |

± 250 |

|

200 |

± 250 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tRR |

Reset Recovery Time |

800 |

600 |

|

800 |

600 |

|

800 |

600 |

|

|

ps |

tPW |

Minimum Pulse Width |

|

|

|

|

|

|

|

|

|

ps |

|

|

MR |

400 |

|

|

400 |

|

|

400 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tSKEW |

Within-Device Skew |

|

50 |

|

|

50 |

|

|

50 |

|

ps |

1 |

tr |

Rise/Fall Times |

|

|

|

|

|

|

|

|

|

ps |

|

tf |

20 - 80% |

300 |

475 |

800 |

300 |

475 |

800 |

300 |

475 |

800 |

|

|

1. Within-device skew is defined as identical transitions on similar paths through a device.

MOTOROLA |

2±2 |

Loading...

Loading...