Motorola MC10175L, MC10175P, MC10175FN Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Quint Latch

The MC10175 is a high speed, low power quint latch. It features five D type latches with common reset and a common two±input clock. Data is transferred on the negative edge of the clock and latched on the positive edge. The two clock inputs are ªORºed together.

Any change on the data input will be reflected at the outputs while the clock is low. The outputs are latched on the positive transition of the clock. While the clock is in the high state, a change in the information present at the data inputs will not affect the output information. The reset input is enabled only when the clock is in the high state.

PD = 400 mW typ/pkg (No Load) tpd = 2.5 ns typ (Data to Output) tr, tf = 2.0 ns typ (20%±80%)

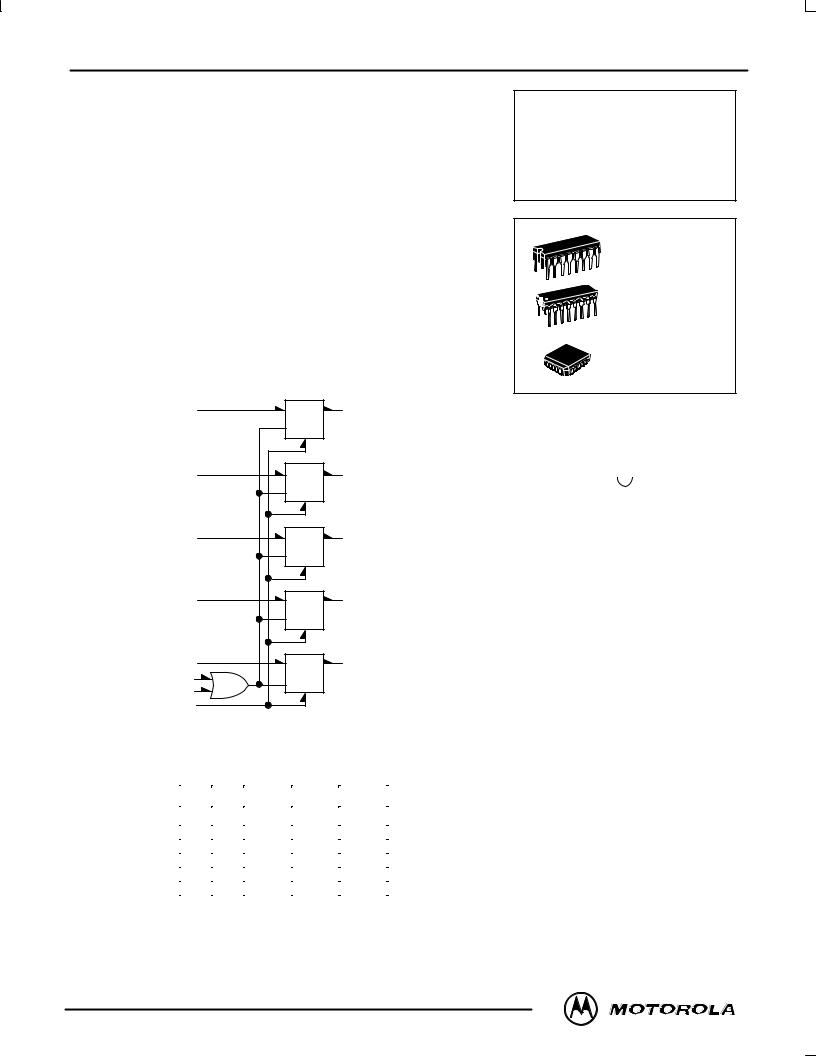

LOGIC DIAGRAM

D0 |

10 |

D |

Q |

14 |

Q0 |

|

|

C |

R |

|

|

D1 |

12 |

D |

Q |

15 |

Q1 |

|

|

C |

R |

|

|

D2 |

13 |

D |

Q |

2 |

Q2 |

|

|

C |

R |

|

|

D3 |

9 |

D |

Q |

3 |

Q3 |

|

|

C |

R |

|

|

D4 |

5 |

D |

Q |

4 |

Q4 |

C0 |

6 |

C |

R |

|

VCC1 = PIN 1 |

C1 |

7 |

|

|||

|

|

|

VCC2 = PIN 16 |

||

RESET |

11 |

|

|

|

|

|

|

|

VEE = PIN 8 |

||

|

|

|

|

|

MC10175

L SUFFIX

CERAMIC PACKAGE

CASE 620±10

P SUFFIX

PLASTIC PACKAGE

CASE 648±08

FN SUFFIX

PLCC

CASE 775±02

DIP

PIN ASSIGNMENT

VCC1 |

|

1 |

|

16 |

|

VCC2 |

||

|

|

|

||||||

Q2 |

|

2 |

|

15 |

|

Q1 |

||

|

|

|

||||||

Q3 |

|

3 |

|

14 |

|

Q0 |

||

|

|

|

||||||

Q4 |

|

4 |

|

13 |

|

D2 |

||

|

|

|

||||||

|

D4 |

|

5 |

|

12 |

|

D1 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

RESET |

|

C0 |

|

6 |

|

11 |

|

||

|

|

|

|

|||||

|

|

|

|

|

|

|

|

D0 |

|

C1 |

|

7 |

|

10 |

|

||

|

|

|

|

|||||

VEE |

|

8 |

|

9 |

|

D3 |

||

|

|

|

||||||

|

|

|

|

|

|

|

|

|

Pin assignment is for Dual±in±Line Package. For PLCC pin assignment, see the Pin Conversion Tables on page 6±11 of the Motorola MECL Data Book (DL122/D).

TRUTH TABLE

D |

C0 |

C1 |

Reset |

Qn+1 |

L |

L |

L |

X |

L |

H |

L |

L |

X |

H |

X |

H |

X |

L |

Q n |

X |

X |

H |

L |

Q n |

X |

H |

X |

H |

L |

X |

X |

H |

H |

L |

|

|

|

|

|

3/93

Motorola, Inc. 1996 |

3±126 |

REV 5 |

MC10175

ELECTRICAL CHARACTERISTICS

|

|

|

|

|

|

|

Test Limits |

|

|

|

|

||

|

|

|

Pin |

|

|

|

|

|

|

|

|

|

|

|

|

|

±30°C |

|

|

+25°C |

|

+85°C |

|

||||

|

|

|

Under |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Characteristic |

Symbol |

Test |

Min |

Max |

Min |

|

Typ |

|

Max |

Min |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply Drain Current |

IE |

8 |

|

107 |

|

|

78 |

|

97 |

|

107 |

mAdc |

|

Input Current |

|

IinH |

6 |

|

460 |

|

|

|

|

290 |

|

290 |

μAdc |

|

|

|

7 |

|

460 |

|

|

|

|

290 |

|

290 |

|

|

|

|

10 |

|

460 |

|

|

|

|

290 |

|

290 |

|

|

|

|

11 |

|

1000 |

|

|

|

|

650 |

|

650 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IinL |

All |

0.5 |

|

0.5 |

|

|

|

|

0.3 |

|

μAdc |

Output Voltage |

Logic 1 |

VOH |

14 |

±1.060 |

±0.890 |

±0.960 |

|

|

|

±0.810 |

±0.890 |

±0.700 |

Vdc |

|

|

|

15 |

±1.060 |

±0.890 |

±0.960 |

|

|

|

±0.810 |

±0.890 |

±0.700 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Voltage |

Logic 0 |

VOL |

14 |

±1.890 |

±1.675 |

±1.850 |

|

|

|

±1.650 |

±1.825 |

±1.615 |

Vdc |

|

|

|

15 |

±1.890 |

±1.675 |

±1.850 |

|

|

|

±1.650 |

±1.825 |

±1.615 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Threshold Voltage |

Logic 1 |

VOHA |

14 |

±1.080 |

|

±0.980 |

|

|

|

|

±0.910 |

|

Vdc |

|

|

|

15 |

±1.080 |

|

±0.980 |

|

|

|

|

±0.910 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Threshold Voltage |

Logic 0 |

VOLA |

14 |

|

±1.655 |

|

|

|

|

±1.630 |

|

±1.595 |

Vdc |

|

|

|

15 |

|

±1.655 |

|

|

|

|

±1.630 |

|

±1.595 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Switching Times |

(50Ω Load) |

|

|

|

|

|

|

|

|

|

|

|

ns |

|

Data Input |

t10+14+ |

14 |

1.0 |

3.6 |

1.0 |

|

|

|

3.5 |

1.0 |

3.6 |

|

|

|

t10±14± |

14 |

1.0 |

3.6 |

1.0 |

|

|

|

3.5 |

1.0 |

3.6 |

|

|

Clock Input |

t6±14+ |

14 |

1.0 |

4.7 |

1.0 |

|

|

|

4.3 |

1.0 |

4.4 |

|

|

|

t6±14± |

14 |

1.0 |

4.7 |

1.0 |

|

|

|

4.3 |

1.0 |

4.4 |

|

|

Reset Input |

t11+4± |

4 |

1.0 |

4.0 |

1.0 |

|

|

|

3.9 |

1.0 |

4.2 |

|

|

|

t11+14± |

14 |

1.0 |

4.0 |

1.0 |

|

|

|

3.9 |

1.0 |

4.2 |

|

Setup TIme |

|

tsetup |

14 |

2.5 |

|

2.5 |

|

|

|

|

2.5 |

|

|

Hold Time |

|

thold |

14 |

1.5 |

|

1.5 |

|

|

|

|

1.5 |

|

|

Rise Time |

(20 to 80%) |

t+ |

14 |

1.0 |

3.6 |

1.1 |

|

|

|

3.5 |

1.1 |

3.7 |

|

Fall Time |

(20 to 80%) |

t± |

14 |

1.0 |

3.6 |

1.1 |

|

|

|

3.5 |

1.1 |

3.7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1.Individually test each input; apply VILmin to pin under test.

2.Output latched to high logic state prior to test.

MECL Data |

3±127 |

MOTOROLA |

DL122 Ð Rev 6 |

|

|

Loading...

Loading...