Motorola MC10115P, MC10115FNR2, MC10115L, MC10115FN Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Quad Line Receiver

The MC10115 is a quad differential amplifier designed for use in sensing differential signals over long lines. The base bias supply (VBB) is made available at pin 9 to make the device useful as a Schmitt trigger, or in other applications where a stable reference voltage is necessary.

Active current sources provide the MC10115 with excellent common mode noise rejection. If any amplifier in a package is not used, one input of that amplifier must be connected to VBB (pin 9) to prevent upsetting the current source bias network.

PD = 110 mW typ/pkg (No Load)

tpd = 2.0 ns typ

tr, tf = 2.0 ns typ (20%±80%)

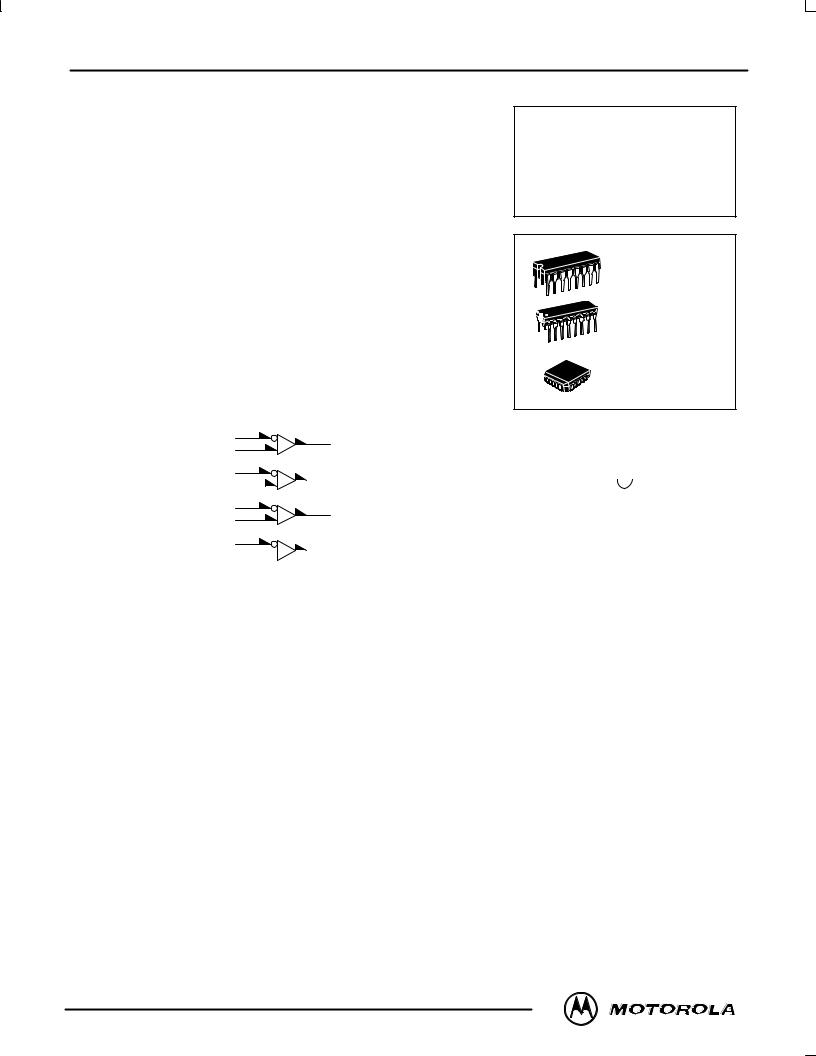

LOGIC DIAGRAM

4

2

5

7

6

3

3

10

14

11

13

12

15

15

9 VBB*

9 VBB*

VCC1 = PIN 1

VCC2 = PIN 16

VEE = PIN 8

*VBB to be used to supply bias to the MC10115 only and bypassed (when used) with 0.01 μF to 0.1 μF capacitor to ground (0 V). VBB can source < 1.0 mA.

When the input pin with the bubble goes positive, the output goes negative.

MC10115

L SUFFIX

CERAMIC PACKAGE

CASE 620±10

P SUFFIX

PLASTIC PACKAGE

CASE 648±08

FN SUFFIX

PLCC

CASE 775±02

DIP

PIN ASSIGNMENT

VCC1 |

|

|

1 |

|

16 |

|

VCC2 |

|||

|

|

|

|

|||||||

AOUT |

|

|

2 |

|

15 |

|

DOUT |

|||

|

|

|

|

|||||||

BOUT |

|

|

3 |

|

14 |

|

COUT |

|||

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

AIN |

|

|

4 |

|

13 |

|

DIN |

||

|

|

|

|

|

||||||

|

AIN |

|

|

5 |

|

12 |

|

DIN |

||

|

|

|

|

|

||||||

|

BIN |

|

|

6 |

|

11 |

|

CIN |

||

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

BIN |

|

|

7 |

|

10 |

|

CIN |

||

|

|

|

|

|

||||||

VEE |

|

|

8 |

|

9 |

|

VBB |

|||

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

Pin assignment is for Dual±in±Line Package. For PLCC pin assignment, see the Pin Conversion Tables on page 6±11 of the Motorola MECL Data Book (DL122/D).

3/93

Motorola, Inc. 1996 |

3±59 |

REV 5 |

MC10115

ELECTRICAL CHARACTERISTICS

|

|

|

|

|

|

|

Test Limits |

|

|

|

|

||

|

|

|

Pin |

|

|

|

|

|

|

|

|

|

|

|

|

|

±30°C |

|

|

+25°C |

|

+85°C |

|

||||

|

|

|

Under |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Characteristic |

Symbol |

Test |

Min |

Max |

Min |

|

Typ |

|

Max |

Min |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply Drain Current |

IE |

8 |

|

29 |

|

|

|

|

26 |

|

29 |

mAdc |

|

Input Current |

|

IinH |

4 |

|

150 |

|

|

|

|

95 |

|

95 |

μAdc |

|

|

ICBO |

4 |

|

1.5 |

|

|

|

|

1.0 |

|

1.0 |

μAdc |

Output Voltage |

Logic 1 |

VOH |

2 |

±1.060 |

±0.890 |

±0.960 |

|

|

|

±0.810 |

±0.890 |

±0.700 |

Vdc |

Output Voltage |

Logic 0 |

VOL |

2 |

±1.890 |

±1.675 |

±1.850 |

|

|

|

±1.650 |

±1.825 |

±1.615 |

Vdc |

Threshold Voltage |

Logic 1 |

VOHA |

2 |

±1.080 |

|

±0.980 |

|

|

|

|

±0.910 |

|

Vdc |

Threshold Voltage |

Logic 0 |

VOLA |

2 |

|

±1.655 |

|

|

|

|

±1.630 |

|

±1.595 |

Vdc |

Reference Voltage |

VBB |

9 |

1.420 |

1.280 |

±1.350 |

|

|

|

±1.230 |

1.295 |

±1.150 |

Vdc |

|

Switching Times |

(50Ω Load) |

|

|

|

|

|

|

|

|

|

|

|

ns |

Propagation Delay |

t4±2+ |

2 |

1.0 |

3.1 |

1.0 |

|

|

|

2.9 |

1.0 |

3.3 |

|

|

|

|

t4+2± |

2 |

1.0 |

3.1 |

1.0 |

|

|

|

2.9 |

1.0 |

3.3 |

|

Rise Time |

(20 to 80%) |

t2+ |

2 |

1.1 |

3.6 |

1.1 |

|

|

|

3.3 |

1.1 |

3.7 |

|

Fall Time |

(20 to 80%) |

t2± |

2 |

1.1 |

3.6 |

1.1 |

|

|

|

3.3 |

1.1 |

3.7 |

|

ELECTRICAL CHARACTERISTICS (continued)

|

|

|

|

|

|

TEST VOLTAGE VALUES (Volts) |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

@ Test Temperature |

VIHmax |

VILmin |

VIHAmin |

|

VILAmax |

VBB |

VEE |

|

||

|

|

|

|

±30°C |

±0.890 |

±1.890 |

±1.205 |

|

±1.500 |

From |

±5.2 |

|

|

|

|

|

+25°C |

|

|

|

|

|

|

|

|

|

|

|

|

±0.810 |

±1.850 |

±1.105 |

|

±1.475 |

Pin |

±5.2 |

|

|

|

|

|

|

+85°C |

|

|

|

|

|

9 |

|

|

|

|

|

|

±0.700 |

±1.825 |

±1.035 |

|

±1.440 |

±5.2 |

|

||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin |

TEST VOLTAGE APPLIED TO PINS LISTED BELOW |

|

||||||

|

|

|

|

Under |

|

|

|

|

|

|

|

(VCC) |

|

|

|

|

|

|

|

|

|

|

|

||

Characteristic |

|

Symbol |

Test |

VIHmax |

VILmin |

VIHAmin |

|

VILAmax |

VBB |

VEE |

Gnd |

|

Power Supply Drain Current |

|

IE |

8 |

|

4,7,10,13 |

|

|

|

5,6,11,12 |

8 |

1, 16 |

|

Input Current |

|

|

IinH |

4 |

4 |

7,10,13 |

|

|

|

5,6,11,12 |

8 |

1, 16 |

|

|

|

ICBO |

4 |

|

7,10,13 |

|

|

|

5,6,11,12 |

8,4 |

1, 16 |

Output Voltage |

Logic 1 |

|

VOH |

2 |

7,10,13 |

4 |

|

|

|

5,6,11,12 |

8 |

1, 16 |

Output Voltage |

Logic 0 |

|

VOL |

2 |

4 |

7,10,13 |

|

|

|

5,6,11,12 |

8 |

1, 16 |

Threshold Voltage |

Logic 1 |

|

VOHA |

2 |

|

7,10,13 |

|

|

4 |

5,6,11,12 |

8 |

1, 16 |

Threshold Voltage |

Logic 0 |

|

VOLA |

2 |

|

7,10,13 |

4 |

|

|

5,6,11,12 |

8 |

1, 16 |

Reference Voltage |

|

|

VBB |

9 |

|

|

|

|

|

5,6,11,12 |

8 |

1, 16 |

Switching Times |

(50Ω Load) |

|

|

|

Pulse In |

Pulse Out |

|

±3.2 V |

+2.0 V |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

Propagation Delay |

|

|

t4±2+ |

2 |

|

4 |

2 |

|

5,6,11,12 |

8 |

1, 16 |

|

|

|

|

t4+2± |

2 |

|

4 |

2 |

|

5,6,11,12 |

8 |

1, 16 |

|

Rise Time |

(20 to 80%) |

|

t2+ |

2 |

|

4 |

2 |

|

5,6,11,12 |

8 |

1, 16 |

|

Fall Time |

(20 to 80%) |

|

t2± |

2 |

|

4 |

2 |

|

5,6,11,12 |

8 |

1, 16 |

|

Each MECL 10,000 series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Outputs are terminated through a 50-ohm resistor to ±2.0 volts. Test procedures are shown for only one gate. The other gates are tested in the same manner.

MOTOROLA |

3±60 |

MECL Data |

|

|

DL122 Ð Rev 6 |

Loading...

Loading...