Motorola MC10E416FN, MC10E416FNR2, MC100E416FN, MC100E416FNR2 Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Quint Differential Line

Receiver

The MC10E416/100E416 is a 5-bit differential line receiving device. The 2.0GHz of bandwidth provided by the high frequency outputs makes the device ideal for buffering of very high speed oscillators.

A VBB pin is available to AC couple an input signal to the device. More information on AC coupling can be found in the design handbook section of this data book.

The design incorporates two stages of gain, internal to the device, making it an excellent choice for use in high bandwidth amplifier applications.

The differential inputs have internal clamp structures which will force the Q output of a gate in an open input condition to go to a LOW state. Thus, inputs of unused gates can be left open and will not affect the operation of the rest of the device. Note that the input clamp will take affect only if both inputs fall 2.5V below VCC.

•Differential D and Q; VBB available

•600ps Max. Propagation Delay

•High Frequency Outputs

•2 Stages of Gain

•Extended 100E VEE Range of ± 4.2V to ± 5.46V

•Internal 75kΩ Input Pulldown Resistors

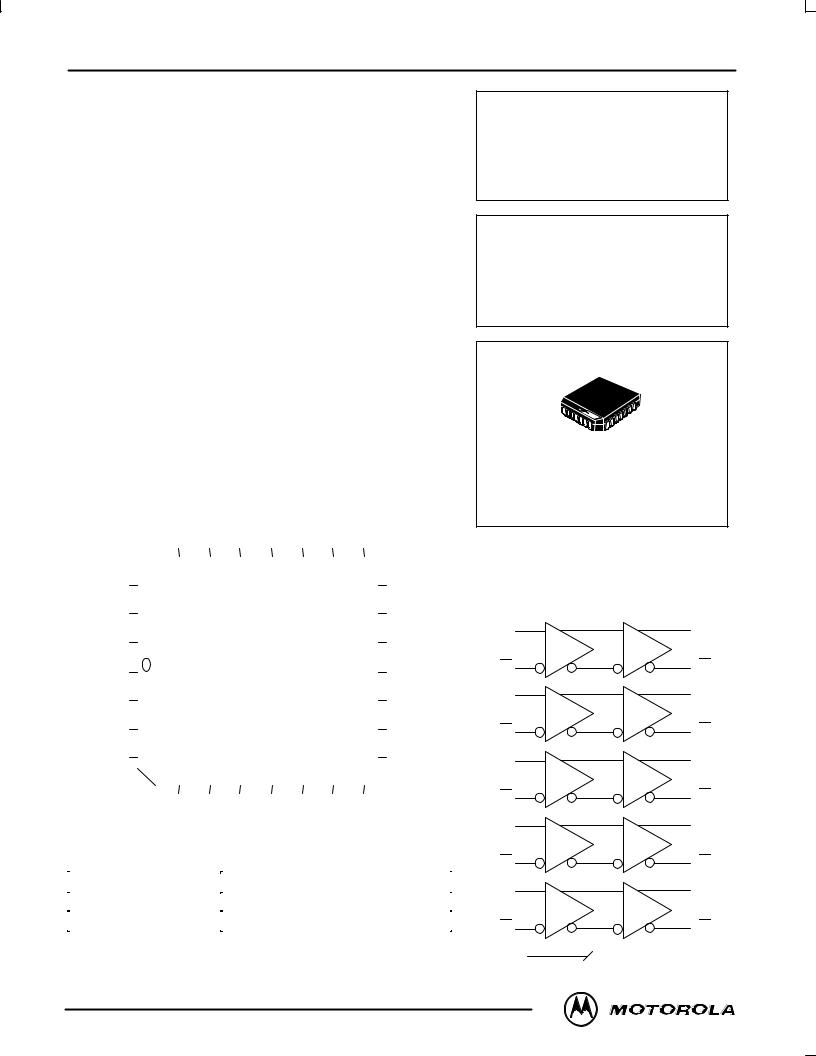

Pinout: 28-Lead PLCC (Top View)

MC10E416

MC100E416

QUINT DIFFERENTIAL

LINE RECEIVER

FN SUFFIX

PLASTIC PACKAGE

CASE 776-02

|

|

|

|

|

|

D3 |

|

|

D4 |

|

D4 |

VCCO |

Q4 |

|

Q4 |

VCCO |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

24 |

23 |

|

22 |

|

21 |

20 |

|

19 |

|

|

|

|

|

||||||||

|

|

|

|

||||||||||||||||||||||||

|

D3 |

|

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|

|

Q3 |

|||

|

D2 |

|

|

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|

|

Q3 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

|

|

|

||

|

D2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

|

|

|

||

VEE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

VBB |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

|

|

Q2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

D0 |

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

|

VCCO |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

|

|

|

||

|

D0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q1 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

5 |

6 |

7 |

|

8 |

|

9 |

10 |

|

11 |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D1 |

|

D1 |

VCCO |

|

Q0 |

Q0 |

VCCO |

|

Q1 |

|

|

||||||||||

|

|

|

|

* All VCC and VCCO pins are tied together on the die. |

|

|

|||||||||||||||||||||

PIN NAMES

Pin |

Function |

||

|

|

|

|

D[0:4], D[0:4] |

Differential Data Inputs |

||

|

|

|

|

Q[0:4], Q[0:4] |

Differential Data Outputs |

||

|

|

|

|

|

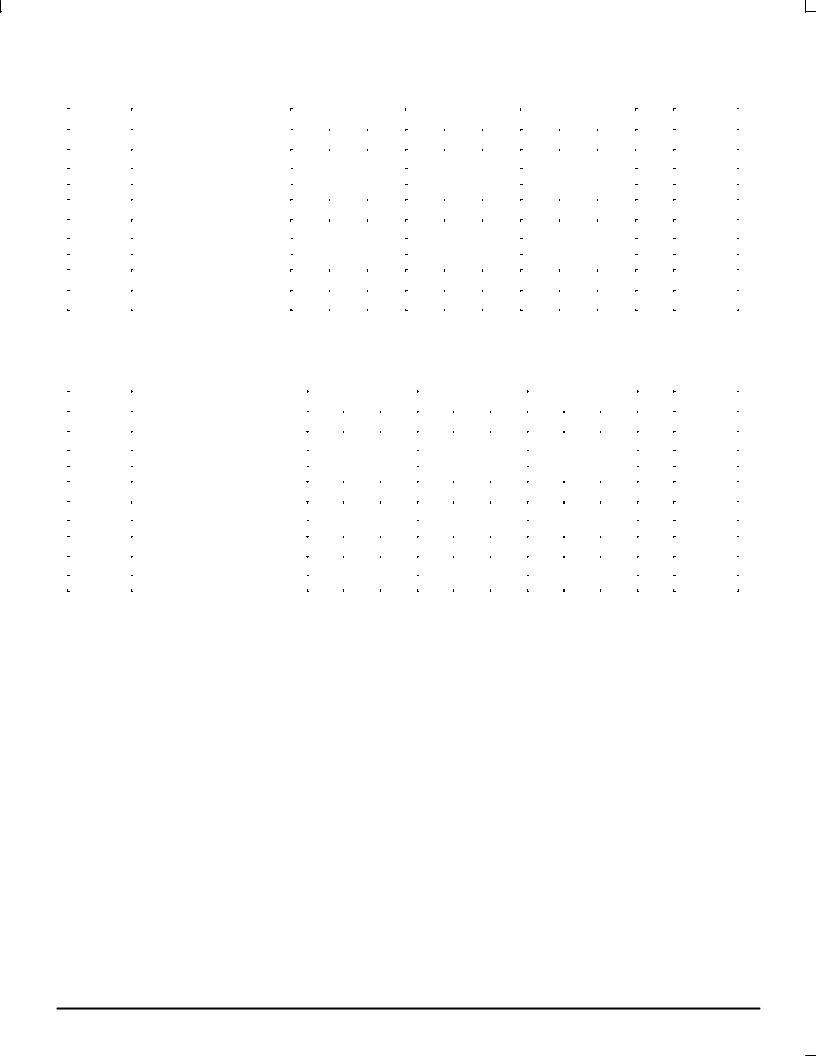

LOGIC DIAGRAM |

D0 |

Q0 |

D0 |

Q0 |

D1 |

Q1 |

D1 |

Q1 |

D2 |

Q2 |

D2 |

Q2 |

D3 |

Q3 |

D3 |

Q3 |

D4 |

Q4 |

D4 |

Q4 |

VBB

12/93

Motorola, Inc. 1996 |

REV 2 |

MC10E416 MC100E416

DC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

min typ |

max |

min |

typ |

max |

min |

typ |

max |

Unit |

Condition |

|

|

|

|

|

|

|

|

|

|

|

|

VBB |

Output Reference Voltage |

|

|

|

|

|

|

|

|

V |

|

|

10E |

±1.38 |

±1.27 |

±1.35 |

|

±1.25 |

±1.31 |

|

±1.19 |

|

|

|

100E |

±1.38 |

±1.26 |

±1.38 |

|

±1.26 |

±1.38 |

|

±1.26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IIH |

Input HIGH Current |

|

150 |

|

|

150 |

|

|

150 |

μA |

|

IEE |

Power Supply Current |

|

|

|

|

|

|

|

|

mA |

|

|

10E |

135 |

162 |

|

135 |

162 |

|

135 |

162 |

|

|

|

100E |

135 |

162 |

|

135 |

162 |

|

155 |

186 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VPP(DC) |

Input Sensitivity |

50 |

|

50 |

|

|

50 |

|

|

mV |

1 |

VCMR |

Common Mode Range |

±1.5 |

0 |

±1.5 |

|

0 |

±1.5 |

|

0 |

V |

2 |

1.Differential input voltage required to obtain a full ECL swing on the outputs.

2.VCMR is referenced to the most positive side of the differential input signal. Normal operation is obtained when the input signal are within the VCMR range and the input swing is greater than VPP MIN and < 1.0V

AC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

min |

typ |

max |

min |

typ |

max |

min |

typ |

max |

Unit |

Condition |

|

|

|

|

|

|

|

|

|

|

|

|

|

tPLH |

Propagation Delay to Output |

|

|

|

|

|

|

|

|

|

ps |

|

tPHL |

d(Diff) |

250 |

350 |

500 |

250 |

350 |

500 |

250 |

350 |

500 |

|

|

|

D(SE) |

200 |

350 |

550 |

200 |

350 |

550 |

200 |

350 |

550 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tSKEW |

Within-Device Skew |

|

50 |

|

|

50 |

|

|

50 |

|

ps |

1 |

tSKEW |

Duty Cycle Skew |

|

±10 |

|

|

±10 |

|

|

±10 |

|

|

|

|

tPLH-tPHL |

|

|

|

|

|

|

ps |

2 |

|||

VPP(AC) |

Minimum Input Swing |

150 |

|

|

150 |

|

|

150 |

|

|

mV |

3 |

tr |

Rise/Fall Time |

|

|

|

|

|

|

|

|

|

|

|

tf |

20 - 80% |

100 |

200 |

350 |

100 |

200 |

350 |

100 |

200 |

350 |

ps |

|

1.Within-device skew is defined as identical transitions on similar paths through a device.

2.Duty cycle skew defined only for differential operation when the delays are measured from the cross point of the inputs to the cross point of the outputs.

3.Minimum input swing for which AC parameters are guaranteed.

MOTOROLA |

2±2 |

Loading...

Loading...