Motorola MC10E016FN, MC100E016FNR2, MC10E016FNR2, MC100E016FN Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

8 Bit Synchronous Binary |

MC10E016 |

|

Up Counter |

||

MC100E016 |

||

|

||

The MC10E/100E016 is a high-speed synchronous, presettable, |

|

|

cascadable 8-bit binary counter. Architecture and operation are the same |

|

|

as the MC10H016 in the MECL 10H family, extended to 8-bits, as shown |

|

|

in the logic symbol. |

|

|

The counter features internal feedback of TC, gated by the TCLD |

8-BIT SYNCHRONOUS |

|

(terminal count load) pin. When TCLD is LOW (or left open, in which case |

||

BINARY UP COUNTER |

||

it is pulled LOW by the internal pull-downs), the TC feedback is disabled, |

||

and counting proceeds continuously, with TC going LOW to indicate an |

|

|

all-one state. When TCLD is HIGH, the TC feedback causes the counter |

|

|

to automatically reload upon TC = LOW, thus functioning as a |

|

|

programmable counter. The Qn outputs do not need to be terminated for |

|

|

the count function to operate properly. To minimize noise and power, |

|

|

unused Q outputs should be left unterminated. |

|

|

• 700MHz Min. Count Frequency |

|

|

• 1000ps CLK to Q, TC |

|

|

• Internal TC Feedback (Gated) |

|

|

• 8-Bit |

FN SUFFIX |

|

• Fully Synchronous Counting and TC Generation |

PLASTIC PACKAGE |

|

CASE 776-02 |

||

|

•Asynchronous Master Reset

•Extended 100E VEE Range of ± 4.2V to ± 5.46V

•75kΩ Input Pulldown Resistors

FUNCTION TABLE

Pinout: 28-Lead PLCC (Top View)

|

|

|

|

|

PE |

|

CE |

|

P7 |

|

P6 |

P5 |

VCCO |

TC |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

24 |

23 |

22 |

|

21 |

20 |

|

19 |

|

|

|

|||||

MR |

|

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|

Q7 |

|

CLK |

|

|

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|

Q6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

TCLD |

|

|

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

VCC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

VEE |

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

|

Q5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

NC |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

|

VCCO |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

P0 |

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

Q4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

P1 |

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

Q3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

5 |

6 |

7 |

8 |

|

9 |

10 |

|

11 |

|

|

|

|||||

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P2 |

|

P3 |

|

P4 |

VCCO |

Q0 |

|

Q1 |

Q2 |

|

|

||||

* All VCC and VCCO pins are tied together on the die.

CE |

PE |

TCLD |

MR |

CLK |

Function |

||

|

|

|

|

|

|

|

|

X |

L |

X |

L |

Z |

Load Parallel (Pn to Qn) |

||

L |

H |

L |

L |

Z |

Continuous Count |

|

|

L |

H |

H |

L |

Z |

Count; Load Parallel on TC = LOW |

||

H |

H |

X |

L |

Z |

Hold |

||

X |

X |

X |

L |

ZZ |

Masters Respond, Slaves Hold |

||

X |

X |

X |

H |

X |

Reset (Qn : = LOW, TC : = HIGH) |

||

Z = clock pulse (low to high);

ZZ = clock pulse (high to low)

PIN NAMES

Pin |

Function |

|

|

P0 ± P7 |

Parallel Data (Preset) Inputs |

Q0 ± Q7 |

Data Outputs |

CE |

Count Enable Control Input |

PE |

Parallel Load Enable Control Input |

MR |

Master Reset |

CLK |

Clock |

TC |

Terminal Count Output |

TCLD |

TC-Load Control Input |

|

|

12/93

Motorola, Inc. 1996 |

REV 2 |

MC10E016 MC100E016

PE |

TCLD |

CE |

PO |

MR |

CLK |

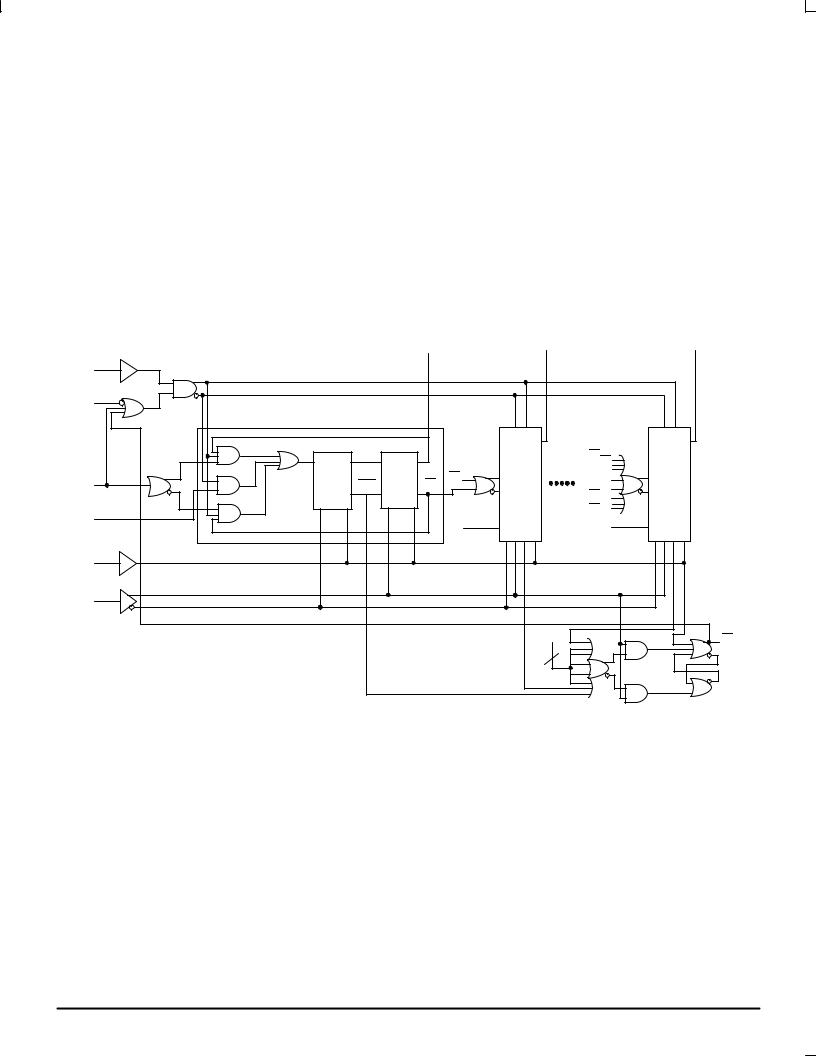

8-BIT BINARY COUNTER LOGIC DIAGRAM

Q0 |

Q1 |

Q7 |

Q0M |

|

|

|

CEQ |

|

|

|

|

|

|

|

|

|

|

|

0 |

|

MASTER |

SLAVE |

CE |

|

Q1Q |

|

BIT 1 |

2 |

BIT 7 |

|||

Q0M |

Q0 |

|

Q |

||

|

|

|

|

3 |

|

BIT 0 |

|

|

|

Q4 Q |

|

|

|

|

|

5 |

|

|

|

|

|

Q6 |

|

|

|

P1 |

|

P7 |

|

|

|

|

|

BITS 2±6 |

TC |

|

|

|

|

|

|

|

|

|

|

5 |

|

Note that this diagram is provided for understanding of logic operation only.

It should not be used for propagation delays as many gate functions are achieved internally without incurring a full gate delay.

MOTOROLA |

2±2 |

MC10E016 MC100E016

DC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

min typ |

max |

min |

typ |

max |

min |

typ |

max |

Unit |

Condition |

|

|

|

|

|

|

|

|

|

|

|

|

IIH |

Input HIGH Current |

|

150 |

|

|

150 |

|

|

150 |

μA |

|

IEE |

Power Supply Current |

|

|

|

|

|

|

|

|

mA |

|

|

10E |

151 |

181 |

|

151 |

181 |

|

151 |

181 |

|

|

|

100E |

151 |

181 |

|

151 |

181 |

|

174 |

208 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

|

|

|

|

|

|

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

|

|

|

Characteristic |

min |

typ |

max |

min |

typ |

max |

min |

typ |

max |

Unit |

Condition |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

fCOUNT |

Max. Count Frequency |

700 |

900 |

|

700 |

900 |

|

700 |

900 |

|

MHz |

|

|||||||

tPLH |

Propagation Delay to Output |

|

|

|

|

|

|

|

|

|

ps |

|

|||||||

tPHL |

|

CLK to Q |

600 |

725 |

1000 |

600 |

725 |

1000 |

600 |

725 |

1000 |

|

|

||||||

|

|

MR to Q |

600 |

775 |

1000 |

600 |

775 |

1000 |

600 |

775 |

1000 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLK to TC |

550 |

775 |

900 |

550 |

775 |

900 |

550 |

775 |

1050 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

MR to TC |

625 |

775 |

1000 |

625 |

775 |

1000 |

625 |

775 |

1000 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

ts |

Setup Time |

|

|

|

|

|

|

|

|

|

ps |

|

|||||||

|

|

Pn |

|

150 |

± 30 |

|

150 |

± 30 |

|

150 |

± 30 |

|

|

|

|||||

|

|

CE |

600 |

400 |

|

600 |

400 |

|

600 |

400 |

|

|

|

||||||

|

|

PE |

|

600 |

400 |

|

600 |

400 |

|

600 |

400 |

|

|

|

|||||

|

|

TCLD |

500 |

300 |

|

500 |

300 |

|

500 |

300 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

th |

Hold Time |

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

Pn |

|

350 |

100 |

|

350 |

100 |

|

350 |

100 |

|

|

|

|||||

|

|

CE |

0 |

± 400 |

|

0 |

± 400 |

|

0 |

± 400 |

|

|

|

||||||

|

|

PE |

|

0 |

± 400 |

|

0 |

± 400 |

|

0 |

± 400 |

|

|

|

|||||

|

|

TCLD |

100 |

± 300 |

|

100 |

± 300 |

|

100 |

± 300 |

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

tRR |

Reset Recovery Time |

900 |

700 |

|

900 |

700 |

|

900 |

700 |

|

ps |

|

|||||||

tPW |

Minimum Pulse Width |

|

|

|

|

|

|

|

|

|

ps |

|

|||||||

|

|

CLK, MR |

400 |

|

|

400 |

|

|

400 |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

tr |

Rise/Fall Times |

|

|

|

|

|

|

|

|

|

ps |

|

|||||||

tf |

20 - 80% |

|

|

300 |

510 |

800 |

300 |

510 |

800 |

300 |

510 |

|

|

|

|||||

2±3 |

MOTOROLA |

Loading...

Loading...