Motorola MC100LVEL92, MC100LVEL92DW, MC100LVEL92DWR2 Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Triple PECL to LVPECL Translator

The MC100LVEL92 is a triple PECL to LVPECL translator. The device receives standard PECL signals and translates them to differential LVPECL output signals.

•500ps Propagation Delays

•Fully Differential Design

•20±Lead SOIC Package

•5V and 3.3V Supplies Required

•>1500V ESD

A PECL VBB output is provided for interfacing single ended PECL signals at the inputs. If a single ended PECL input is to be used the PECL VBB output should be connected to the D input and the active signal will drive the D input. When used the PECL VBB should be bypassed to ground via a 0.01μf capacitor. The PECL VBB is designed to act as a switching reference for the MC100LVEL92 under single ended input conditions, as a result the pin can only source/sink 0.5mA of current.

To accomplish the PECL to LVPECL level translation, the MC100LVEL92 requires three power rails. The VCC supply is to be connected to the standard PECL supply, the LVCC supply is to be connected to the LVPECL supply, and Ground is connected to the system ground plane. Both the VCC and LVCC should be bypassed to ground with a 0.01μf capacitor.

Under open input conditions, the D input will be biased at a VCC/2 voltage level and the D input will be pulled to ground. This condition will force the ªQº output low, ensuring stability.

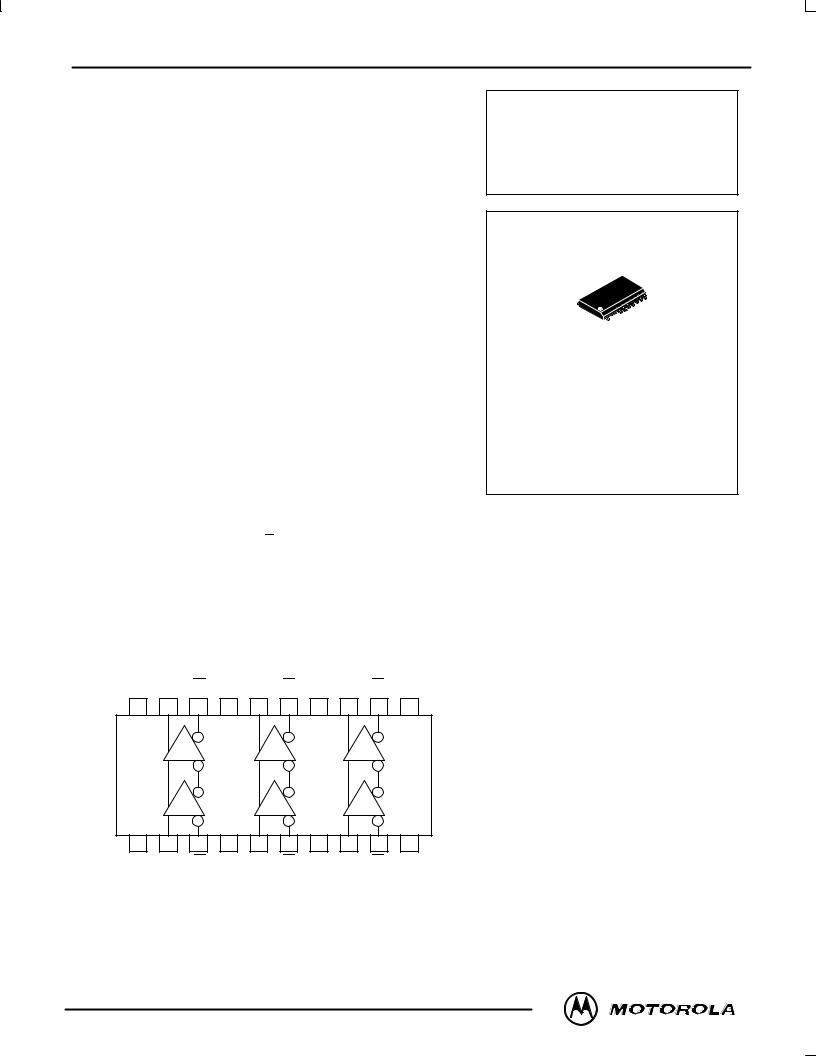

Logic Diagram and Pinout: 20-Lead SOIC (Top View)

VCC |

Q0 |

Q0 |

LVCC |

Q1 |

Q1 |

LVCC |

Q2 |

Q2 |

VCC |

20 |

19 |

18 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

LVPECL |

|

|

LVPECL |

|

|

LVPECL |

|

|

|

PECL |

|

|

PECL |

|

|

PECL |

|

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

VCC |

D0 |

D0 |

PECL |

D1 |

D1 |

PECL |

D2 |

D2 |

GND |

|

|

|

VBB |

|

|

VBB |

|

|

|

MC100LVEL92

20

1

DW SUFFIX

PLASTIC SOIC PACKAGE

CASE 751D-04

PIN NAMES

Pins |

Function |

|

|

Dn |

PECL Inputs |

Qn |

LVPECL Outputs |

VBB |

PECL Reference Voltage Output |

LVCC |

VCC for LVPECL Output |

VCC |

VCC for PECL Inputs |

GND |

Common Ground Rail |

|

|

7/97

Motorola, Inc. 1997 |

4±1 |

REV 2 |

Loading...

Loading...