Motorola MC10ELT20D, MC10ELT20DR2, MC100ELT20DR2, MC100ELT20D Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

TTL to Differential PECL |

MC10ELT20 |

|

|

Translator |

MC100ELT20 |

|

|

|

|

The MC10ELT/100ELT20 is a TTL to differential PECL translator. Because PECL (Positive ECL) levels are used only +5V and ground are required. The small outline 8-lead SOIC package and the single gate of the ELT20 makes it ideal for those applications where space, performance and low power are at a premium. Because the mature MOSAIC 1.5 process is used, low cost can be added to the list of features.

The ELT20 is available in both ECL standards: the 10ELT is compatible with positive MECL 10H logic levels while the 100ELT is compatible with positive ECL 100K logic levels.

•1.5ns Typical Propagation Delay

•Differential PECL Outputs

•Small Outline SOIC Package

•PNP TTL Inputs for Minimal Loading

•Flow Through Pinouts

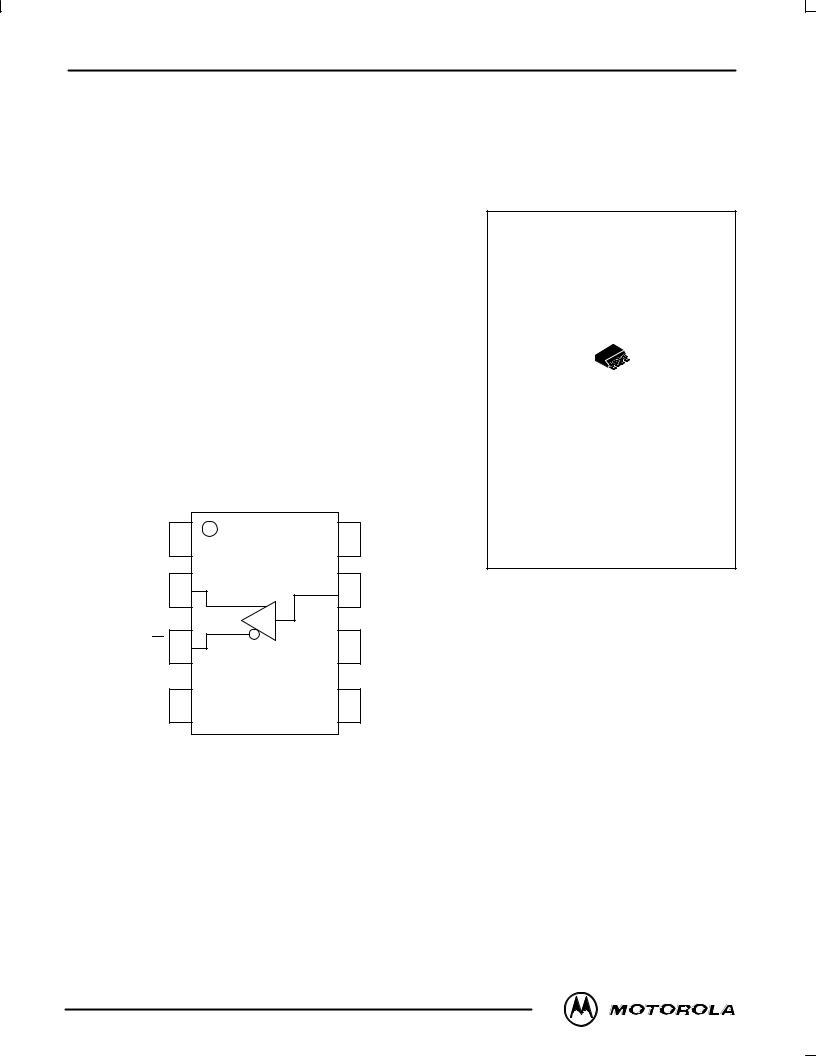

LOGIC DIAGRAM AND PINOUT ASSIGNMENT

NC |

1 |

|

8 |

VCC |

Q |

2 |

TTL |

7 |

D0 |

|

||||

|

|

PECL |

|

|

Q |

3 |

|

6 |

NC |

NC |

4 |

|

5 |

GND |

8

1

D SUFFIX

PLASTIC SOIC PACKAGE

CASE 751-05

|

|

PIN DESCRIPTION |

|

|

|

|

|

|

|

|

PIN |

|

FUNCTION |

|

|

|

|

|

|

|

Q |

|

Diff PECL Outputs |

|

|

D |

|

TTL Input |

|

|

VCC |

|

+5.0V Supply |

|

|

GND |

|

Ground |

|

|

|

|

|

|

|

|

|

|

|

1/95

Motorola, Inc. 1996 |

REV 2 |

Loading...

Loading...