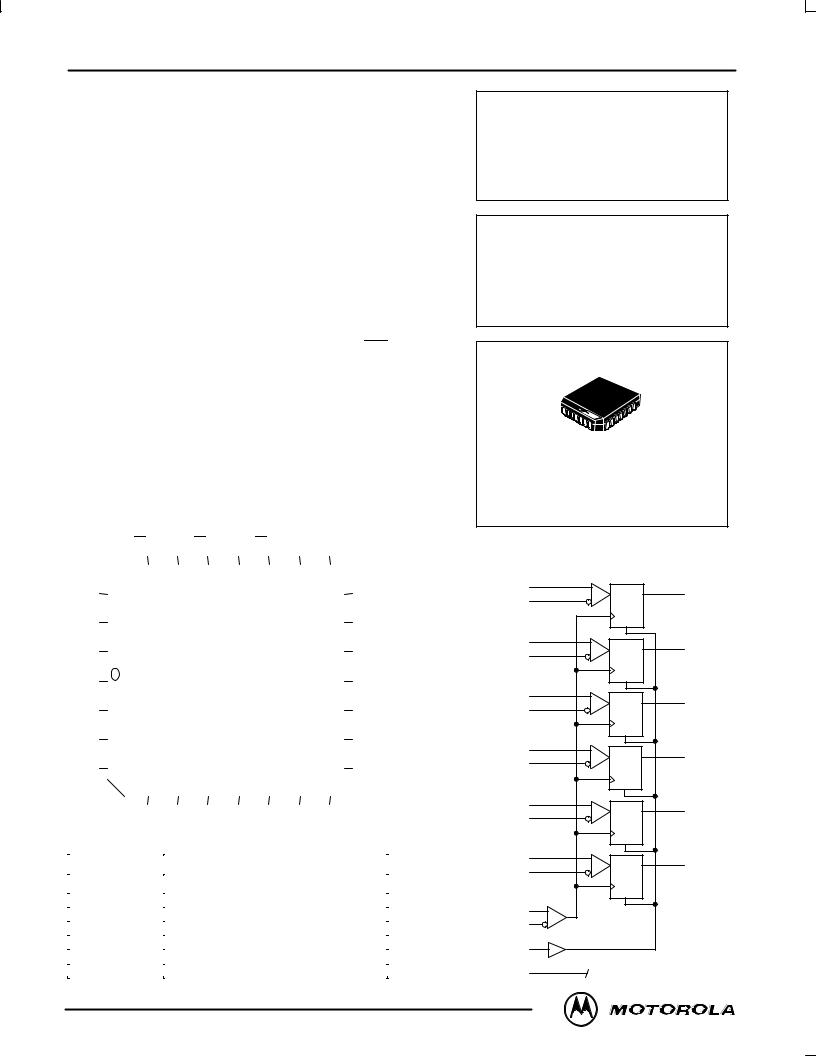

Motorola MC10E451FN, MC10E451FNR2, MC100E451FN, MC100E451FNR2 Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

6 Bit D Register Differential

Data and Clock

The MC10E/100E451 contains six D-type flip-flops with single-ended outputs and differential data inputs. The common clock input is also differential. The registers are triggered by a positive transition of the positive clock (CLK) input.

A HIGH on the Master Reset (MR) input resets all Q outputs to LOW. The VBB output is intended for use as a reference voltage for single-ended reception of ECL signals to that device only. When using for this purpose, it is recommended that VBB is decoupled to VCC via a 0.01μF capacitor.

The differential input structures are clamped so that the inputs of unused registers can be left open without upsetting the bias network of the device. The clamping action will assert the D and the CLK sides of the inputs. Because of the edge triggered flip-flop nature of the device simultaneously opening both the clock and data inputs will result in an output which reaches an unidentified but valid state. Note that the input clamps only operate when both inputs fall to 2.5V below VCC.

•Differential Inputs: Data and Clock

•VBB Output

•1100MHz Min. Toggle Frequency

•Asynchronous Master Reset

•Extended 100E VEE Range of ± 4.2V to ± 5.46V

•75kΩ Input Pulldown Resistors

|

|

|

|

|

|

D5 |

|

D5 |

|

D4 |

D4 |

|

D3 |

|

D3 |

VCCO |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

|

24 |

23 |

|

|

22 |

21 |

|

20 |

|

19 |

|

|

|

||||||

CLK |

|

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|

Q5 |

|||

VBB |

|

|

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|

Q4 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16 |

|

|

||

CLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCC |

|||||

VEE |

|

|

1 |

|

|

|

|

Pinout: 28-Lead PLCC |

15 |

|

|||||||||||||||

|

|

|

|

|

|

|

Q3 |

||||||||||||||||||

|

|

|

|

|

|

|

|||||||||||||||||||

MR |

|

|

2 |

|

|

|

|

|

|

(Top View) |

|

|

|

14 |

|

VCCO |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

NC |

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q2 |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

D0 |

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

|

Q1 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

5 |

|

6 |

7 |

|

|

8 |

9 |

|

10 |

|

11 |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

|

D1 |

|

D1 |

D2 |

|

D2 |

VCCO |

|

Q0 |

|

|

|||||||

* All VCC and VCCO pins are tied together on the die.

PIN NAMES

Pin |

Function |

|

|

D0 ± D5 |

+Data Input |

D0 ± D5 |

± Data Input |

CLK |

+Clock Input |

CLK |

± Clock Input |

MR |

Master Reset Input |

VBB |

VBB Output |

Q0 ± Q5 |

Data Outputs |

MC10E451

MC100E451

6-BIT D REGISTER DIFFERENTIAL DATA AND CLOCK

FN SUFFIX

PLASTIC PACKAGE

CASE 776-02

LOGIC DIAGRAM

D0 |

D |

Q0 |

|

D0 |

|||

|

|

||

|

|

R |

|

D1 |

D |

Q1 |

|

D1 |

|||

|

R |

||

|

|

||

D2 |

D |

Q2 |

|

D2 |

|

R |

|

|

|

||

D3 |

D |

Q3 |

|

D3 |

|

R |

|

|

|

||

D4 |

D |

Q4 |

|

D4 |

|||

|

|

||

|

|

R |

|

D5 |

D |

Q5 |

|

D5 |

|

R |

|

|

|

||

CLK |

|

|

|

CLK |

|

|

|

MR |

|

|

|

V |

|

|

12/93

Motorola, Inc. 1996 |

REV 2 |

MC10E451 MC100E451

DC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

min typ |

max |

min |

typ |

max |

min |

typ |

max |

Unit |

Condition |

|

|

|

|

|

|

|

|

|

|

|

|

VBB |

Output Reference Voltage |

|

|

|

|

|

|

|

|

V |

|

|

10E |

±1.3 |

±1.2 |

±1.3 |

|

±1.2 |

±1.3 |

|

±1.1 |

|

|

|

|

8 |

7 |

5 |

|

5 |

1 |

|

9 |

|

|

|

100E |

±1.3 |

±1.2 |

±1.3 |

|

±1.2 |

±1.3 |

|

±1.2 |

|

|

|

|

8 |

6 |

8 |

|

6 |

8 |

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IIH |

Input HIGH Current |

|

150 |

|

|

150 |

|

|

150 |

μA |

|

IEE |

Power Supply Current |

|

|

|

|

|

|

|

|

mA |

|

|

10E |

84 |

101 |

|

84 |

101 |

|

84 |

101 |

|

|

|

100E |

84 |

101 |

|

84 |

101 |

|

97 |

116 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VCMR |

Common Mode Range |

± 2.0 |

± 0.4 |

± 2.0 |

|

± 0.4 |

± 2.0 |

|

± 0.4 |

V |

2 |

1.VCMR is referenced to the most positive side of the differential input signal. Normal operation is obtained when the ªHIGHº input is within the VCMR range and the input swing is greater than VPP MIN and < 1.0V.

AC CHARACTERISTICS (VEE = VEE(min) to VEE(max); VCC = VCCO = GND)

|

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

min |

typ |

max |

min |

typ |

max |

min |

typ |

max |

Unit |

Condition |

|

|

|

|

|

|

|

|

|

|

|

|

|

fMAX |

Max, Toggle Frequency |

1100 |

1400 |

|

1100 |

1400 |

|

1100 |

1400 |

|

MHz |

|

tPLH |

Propagation Delay to Output |

|

|

|

|

|

|

|

|

|

ps |

|

tPHL |

CLK (Diff) |

475 |

650 |

800 |

475 |

650 |

800 |

475 |

650 |

800 |

|

|

|

CLK (SE) |

425 |

650 |

850 |

425 |

650 |

850 |

425 |

650 |

850 |

|

|

|

MR |

425 |

600 |

850 |

425 |

600 |

850 |

425 |

600 |

850 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ts |

Setup Time |

|

|

|

|

|

|

|

|

|

ps |

|

|

D |

150 |

±100 |

|

150 |

±100 |

|

150 |

±100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

th |

Hold Time |

|

|

|

|

|

|

|

|

|

ps |

|

|

D |

250 |

100 |

|

250 |

100 |

|

250 |

100 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VPP(AC) |

Minimum Input Swing |

150 |

|

|

150 |

|

|

159 |

|

|

mV |

1 |

tRR |

Reset Recovery Time |

750 |

600 |

|

750 |

600 |

|

750 |

600 |

|

ps |

|

tPW |

Minimum Pulse Width |

|

|

|

|

|

|

|

|

|

ps |

|

|

CLK, MR |

400 |

|

|

400 |

|

|

400 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tSKEW |

Within-Device Skew |

|

100 |

|

|

100 |

|

|

100 |

|

ps |

2 |

tr |

Rise/Fall Times |

|

|

|

|

|

|

|

|

|

ps |

|

tf |

20 - 80% |

275 |

450 |

800 |

275 |

450 |

800 |

275 |

450 |

800 |

|

|

1.Minimum input voltage for which AC parameters are guaranteed.

2.Within-device skew is defined as identical transitions on similar paths through a device.

MOTOROLA |

2±2 |

Loading...

Loading...