Motorola MC10162FN, MC10162L, MC10162P Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Binary to 1-8 Decoder (High)

The MC10162 is designed to convert three lines of input data to a one±of±eight output. The selected output will be high while all other outputs are low. The enable inputs, when either or both are high, force all outputs low.

The MC10162 is a true parallel decoder. No series gating is used internally, eliminating unequal delay times found in other decoders.

This device is ideally suited for demultiplexer applications. One of the two enable inputs is used as the data input, while the other is used as a data enable input.

A complete mux/demux operation on 16 bits for data distribution is illustrated in Figure 1 of the MC10161 data sheet.

PD = 315 ns typ/pkg (No Load) tpd = 4.0 ns typ

tr, tf = 2.0 ns typ (20%±80%)

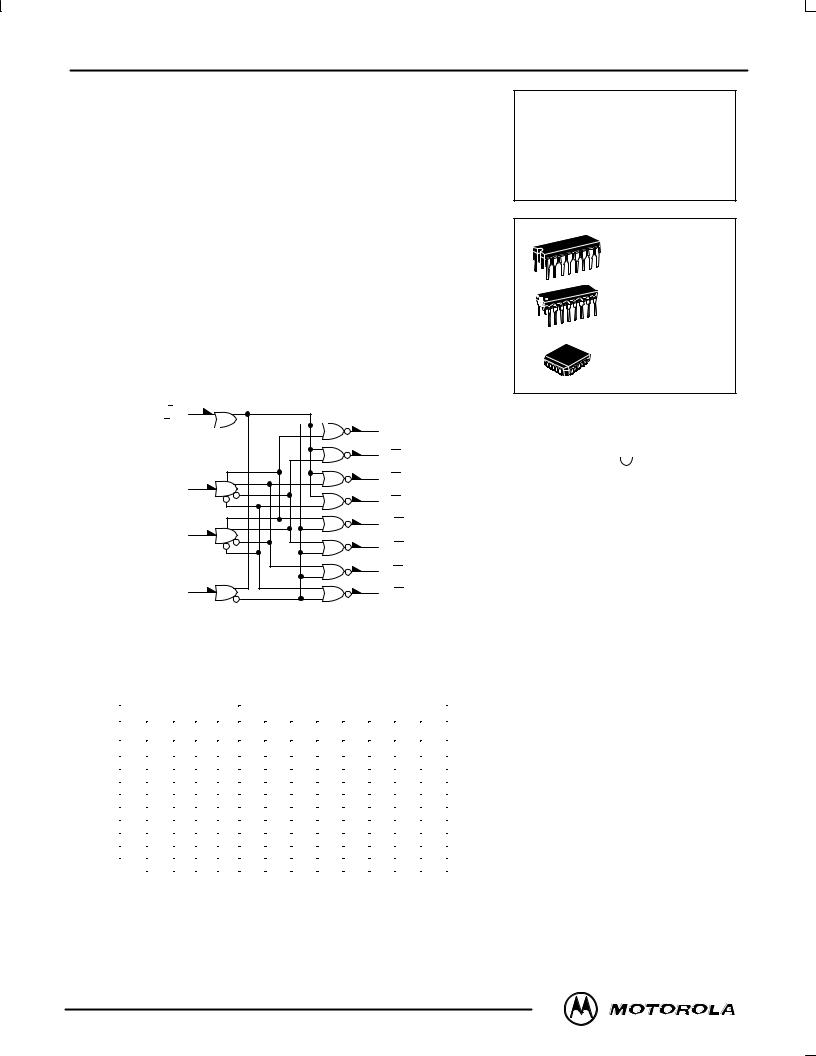

LOGIC DIAGRAM

E0 2

E1 15

6 Q0

6 Q0

5 Q1

4 Q2

A 7

3 Q3

13 Q4

B 9

12 Q5

11 Q6

C 14 |

10 Q7 |

VCC1 = PIN 1

VCC2 = PIN 16

VEE = PIN 8

TRUTH TABLE

|

|

|

|

|

INPUTS |

|

|

|

|

|

|

|

|

|

|

|

OUTPUTS |

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

E0 |

|

E1 |

C |

B |

A |

Q0 |

|

Q1 |

Q2 |

Q3 |

Q4 |

|

Q5 |

|

Q6 |

|

Q7 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

L |

|

L |

L |

L |

L |

|

H |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

||||||||||

|

L |

|

L |

L |

L |

H |

|

L |

|

H |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

||||||||||

|

L |

|

L |

L |

H |

L |

|

L |

|

L |

|

H |

|

L |

|

L |

|

L |

|

L |

|

L |

||||||||||

|

L |

|

L |

L |

H |

H |

|

L |

|

L |

|

L |

|

H |

|

L |

|

L |

|

L |

|

L |

||||||||||

|

L |

|

L |

H |

L |

L |

|

L |

|

L |

|

L |

|

L |

|

H |

|

L |

|

L |

|

L |

||||||||||

|

L |

|

L |

H |

L |

H |

|

L |

|

L |

|

L |

|

L |

|

L |

|

H |

|

L |

|

L |

||||||||||

|

L |

|

L |

H |

H |

L |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

|

H |

|

L |

||||||||||

|

L |

|

L |

H |

H |

H |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

|

H |

||||||||||

|

H |

|

X |

X |

X |

X |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

||||||||||

|

X |

|

H |

X |

X |

X |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

|

L |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MC10162

L SUFFIX

CERAMIC PACKAGE

CASE 620±10

P SUFFIX

PLASTIC PACKAGE

CASE 648±08

FN SUFFIX

PLCC

CASE 775±02

DIP

PIN ASSIGNMENT

VCC1 |

|

1 |

|

16 |

|

VCC2 |

||||

|

|

|

||||||||

|

|

|

|

2 |

|

15 |

|

|

|

|

|

E0 |

|

|

|

E1 |

|||||

|

|

|

|

|||||||

|

|

|

|

3 |

|

14 |

|

C |

||

|

Q3 |

|

|

|

||||||

|

|

|

|

|||||||

|

|

|

|

4 |

|

13 |

|

|

|

|

|

Q2 |

|

|

|

Q4 |

|||||

|

|

|

|

|||||||

|

|

|

|

5 |

|

12 |

|

|

|

|

|

Q1 |

|

|

|

Q5 |

|||||

|

|

|

|

|||||||

|

|

|

|

6 |

|

11 |

|

|

|

|

|

Q0 |

|

|

|

Q6 |

|||||

|

|

|

|

|||||||

|

|

|

|

7 |

|

10 |

|

|

|

|

|

A |

|

|

|

Q7 |

|||||

|

|

|

|

|||||||

VEE |

|

8 |

|

9 |

|

B |

||||

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

Pin assignment is for Dual±in±Line Package. For PLCC pin assignment, see the Pin Conversion Tables on page 6±11 of the Motorola MECL Data Book (DL122/D).

3/93

Motorola, Inc. 1996 |

3±78 |

REV 5 |

MC10162

ELECTRICAL CHARACTERISTICS

|

|

|

|

|

|

|

Test Limits |

|

|

|

|

||

|

|

|

Pin |

|

|

|

|

|

|

|

|

|

|

|

|

|

±30°C |

|

|

+25°C |

|

+85°C |

|

||||

|

|

|

Under |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Characteristic |

Symbol |

Test |

Min |

Max |

Min |

|

Typ |

|

Max |

Min |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply Drain Current |

IE |

8 |

|

84 |

|

|

61 |

|

76 |

|

84 |

mAdc |

|

Input Current |

|

IinH |

14 |

|

350 |

|

|

|

|

220 |

|

220 |

μAdc |

|

|

IinL |

14 |

0.5 |

|

0.5 |

|

|

|

|

0.3 |

|

μAdc |

Output Voltage |

Logic 1 |

VOH |

13 |

±1.060 |

±0.890 |

±0.960 |

|

|

|

±0.810 |

±0.890 |

±0.700 |

Vdc |

Output Voltage |

Logic 0 |

VOL |

13 |

±1.890 |

±1.675 |

±1.850 |

|

|

|

±1.650 |

±1.825 |

±1.615 |

Vdc |

|

|

|

13 |

±1.890 |

±1.675 |

±1.850 |

|

|

|

±1.650 |

±1.825 |

±1.615 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Threshold Voltage |

Logic 1 |

VOHA |

13 |

±1.080 |

|

±0.980 |

|

|

|

|

±0.910 |

|

Vdc |

Threshold Voltage |

Logic 0 |

VOLA |

13 |

|

±1.655 |

|

|

|

|

±1.630 |

|

±1.595 |

Vdc |

|

|

|

13 |

|

±1.655 |

|

|

|

|

±1.630 |

|

±1.595 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Switching Times |

(50Ω Load) |

|

|

|

|

|

|

|

|

|

|

|

ns |

Propagation Delay |

t14+13± |

13 |

1.5 |

6.2 |

1.5 |

|

4.0 |

|

6.0 |

1.5 |

6.4 |

|

|

|

|

t14±13+ |

13 |

1.5 |

6.2 |

1.5 |

|

4.0 |

|

6.0 |

1.5 |

6.4 |

|

Rise Time |

(20 to 80%) |

t13+ |

13 |

1.0 |

3.3 |

1.1 |

|

2.0 |

|

3.3 |

1.1 |

3.5 |

|

Fall Time |

(20 to 80%) |

t13± |

13 |

1.0 |

3.3 |

1.1 |

|

2.0 |

|

3.3 |

1.1 |

3.5 |

|

ELECTRICAL CHARACTERISTICS (continued)

|

|

|

|

|

TEST VOLTAGE VALUES (Volts) |

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

@ Test Temperature |

VIHmax |

VILmin |

VIHAmin |

VILAmax |

VEE |

|

|

|

|

|

±30°C |

±0.890 |

±1.890 |

±1.205 |

±1.500 |

±5.2 |

|

|

|

|

+25°C |

|

|

|

|

|

|

|

|

|

±0.810 |

±1.850 |

±1.105 |

±1.475 |

±5.2 |

|

|

|

|

|

+85°C |

|

|

|

|

|

|

|

|

|

±0.700 |

±1.825 |

±1.035 |

±1.440 |

±5.2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin |

TEST VOLTAGE APPLIED TO PINS LISTED BELOW |

|

||||

|

|

|

Under |

|

|

|

|

|

(VCC) |

|

|

|

|

|

|

|

|

||

Characteristic |

Symbol |

Test |

VIHmax |

VILmin |

VIHAmin |

VILAmax |

VEE |

Gnd |

|

Power Supply Drain Current |

IE |

8 |

|

|

|

|

8 |

1,16 |

|

Input Current |

|

IinH |

14 |

14 |

|

|

|

8 |

1,16 |

|

|

IinL |

14 |

|

14 |

|

|

8 |

1,16 |

Output Voltage |

Logic 1 |

VOH |

13 |

14 |

|

|

|

8 |

1,16 |

Output Voltage |

Logic 0 |

VOL |

13 |

2 |

|

|

|

8 |

1,16 |

|

|

|

13 |

15 |

|

|

|

8 |

1,16 |

|

|

|

|

|

|

|

|

|

|

Threshold Voltage |

Logic 1 |

VOHA |

13 |

|

|

14 |

|

8 |

1,16 |

Threshold Voltage |

Logic 0 |

VOLA |

13 |

|

|

2 |

|

8 |

1,16 |

|

|

|

13 |

|

|

15 |

|

8 |

1,16 |

|

|

|

|

|

|

|

|

|

|

Switching Times |

(50Ω Load) |

|

|

|

|

Pulse In |

Pulse Out |

±3.2 V |

+2.0 V |

|

|

|

|

|

|

|

|

|

|

Propagation Delay |

|

t14+13+ |

13 |

|

|

14 |

13 |

8 |

1,16 |

|

|

t14±13± |

13 |

|

|

14 |

13 |

8 |

1,16 |

Rise Time |

(20 to 80%) |

t+ |

13 |

|

|

14 |

13 |

8 |

1,16 |

Fall Time |

(20 to 80%) |

t± |

13 |

|

|

14 |

13 |

8 |

1,16 |

|

|

|

|

|

|

|

|

|

|

Each MECL 10,000 series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 linear fpm is maintained. Outputs are terminated through a 50±ohm resistor to ±2.0 volts. Test procedures are shown for only one gate. The other gates are tested in the same manner.

MECL Data |

3±79 |

MOTOROLA |

DL122 Ð Rev 6 |

|

|

Loading...

Loading...