Motorola MC100LVEL29, MC100LVEL29DW, MC100LVEL29DWR2, MC100EL29, MC100EL29DW Datasheet

...

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Dual Differential Data and Clock |

|

MC100LVEL29 |

D Flip-Flop With Set and Reset |

|

MC100EL29 |

|

|

|

|

|

|

The MC100LVEL29 is a dual master±slave flip flop. The device features fully differential Data and Clock inputs as well as outputs. The MC100EL29 is pin and functionally equivalent to the MC100LVEL29 but is specified for operation at the standard 100E ECL voltage supply. A VBB output is provided for AC coupling, refer to the interfacing section of the ECLinPS Data Book (DL140) for more information on AC coupling ECL signals. Data enters the master latch when the clock is LOW and transfers to the slave upon a positive transition on the clock input.

The differential inputs have special circuitry which ensures device stability under open input conditions. When both differential inputs are left open the D input will pull down to VEE and the D input will bias around VCC/2. The outputs will go to a defined state, however the state will be random based on how the flip flop powers up.

Both flip flops feature asynchronous, overriding Set and Reset inputs. Note that the Set and Reset inputs cannot both be HIGH simultaneously.

•1100MHz Flip±Flop Toggle Frequency

•20±lead SOIC Package

•580ps Propagation Delays

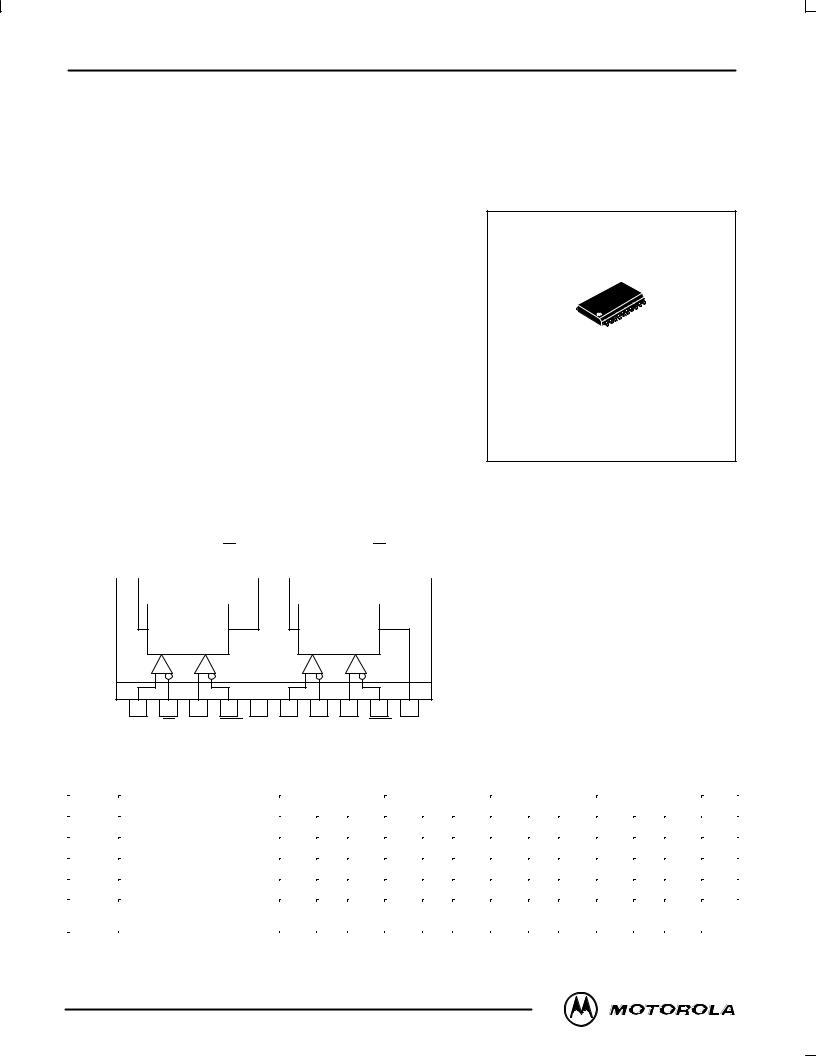

Logic Diagram and Pinout: 20-Lead SOIC (Top View)

|

R0 |

|

VCC |

Q0 |

|

Q0 |

S0 |

S1 |

VCC |

Q1 |

Q1 |

VEE |

||||||||||||

|

20 |

|

19 |

|

18 |

|

17 |

|

16 |

|

15 |

|

14 |

|

13 |

|

12 |

|

11 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q |

Q |

|

|

|

Q |

Q |

|

|

|

R |

|

S |

|

|

S |

|

R |

|

|

D |

CLK |

|

|

|

D |

CLK |

|

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

D0 |

D0 |

CLK0 |

CLK0 |

VBB |

D1 |

D1 |

CLK1 |

CLK1 |

R1 |

MC100LVEL29

DC CHARACTERISTICS (VEE = ±3.0V to ±3.8V; VCC = GND)

20

1

DW SUFFIX

PLASTIC SOIC PACKAGE

CASE 751D±04

TRUTH TABLE

|

|

S |

|

D |

|

CLK |

|

Q |

|

|

|

R |

|

|

|

|

|

Q |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

L |

|

L |

|

L |

|

Z |

|

L |

|

H |

|

L |

|

L |

|

H |

|

Z |

|

H |

|

L |

|

H |

|

L |

|

X |

|

X |

|

L |

|

H |

|

L |

|

H |

|

X |

|

X |

|

H |

|

L |

|

H |

|

H |

|

X |

|

X |

|

Undef |

Undef |

||

|

|

|

|

|

|

|

|

|

|

||

Z = LOW to HIGH Transition |

|

|

|

|

|||||||

PIN NAMES |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|||

Pins |

|

|

|

Function |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|||

D0±D1 |

|

|

|

Data Inputs |

|

|

|

|

|||

R0±R1 |

|

|

|

Reset Inputs |

|

|

|

|

|||

CLK0±CLK1 |

|

|

Clock Inputs |

|

|

|

|

||||

S0±S1 |

|

|

|

Set Inputs |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

±40°C |

|

|

0°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

Min |

Typ |

Max |

Min |

Typ |

Max |

Min |

Typ |

Max |

Min |

Typ |

Max |

Unit |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IEE |

Power Supply Current |

|

35 |

50 |

|

35 |

50 |

|

35 |

50 |

|

35 |

50 |

mA |

||

VBB |

Output Reference Voltage |

±1.38 |

|

±1.26 |

±1.38 |

|

±1.26 |

±1.38 |

|

±1.26 |

±1.38 |

|

±1.26 |

V |

||

IIH |

Input HIGH Current |

|

|

150 |

|

|

150 |

|

|

150 |

|

|

150 |

μA |

||

IIL |

Input LOW Current |

Dn |

Inputs |

0.5 |

|

|

0.5 |

|

|

0.5 |

|

|

0.5 |

|

|

μA |

|

|

|

|

|

|

|

|

|

||||||||

|

|

Dn Inputs |

±300 |

|

|

±300 |

|

|

±300 |

|

|

±300 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

7/95

Motorola, Inc. 1996 |

REV 1 |

Loading...

Loading...