Motorola MC10EL33D, MC10EL33DR2, MC100EL33D, MC100EL33DR2 Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

4 Divider

The MC10EL/100EL33 is an integrated 4 divider. The differential clock inputs and the VBB allow a differential, single-ended or AC coupled interface to the device. If used, the VBB output should be bypassed to ground with a 0.01μF capacitor. Also note that the VBB is designed to be used as an input bias on the EL33 only, the VBB output has limited current sink and source capability.

The reset pin is asynchronous and is asserted on the rising edge. Upon power-up, the internal flip-flops will attain a random state; the reset allows for the synchronization of multiple EL33's in a system.

•650ps Propagation Delay

•4.0GHz Toggle Frequency

•High Bandwidth Output Transitions

•75kΩ Internal Input Pulldown Resistors

•>1000V ESD Protection

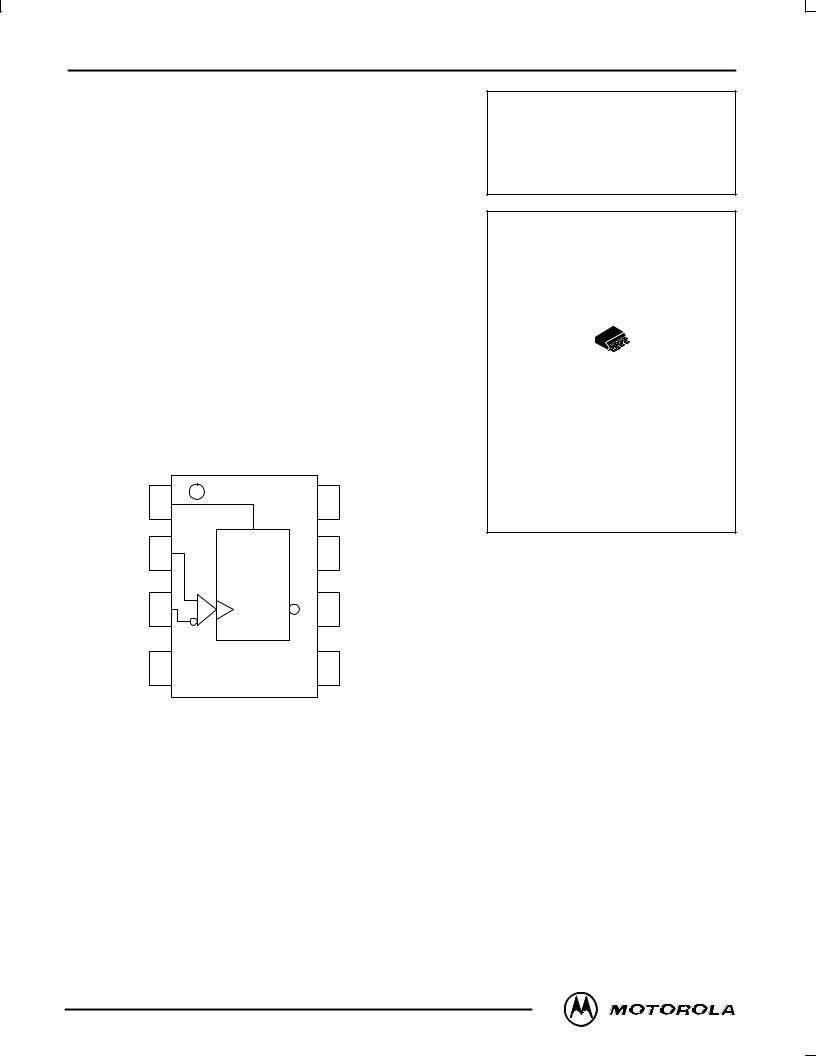

LOGIC DIAGRAM AND PINOUT ASSIGNMENT

Reset |

1 |

8 |

VCC |

||||||

|

|

|

|

R |

|

|

|||

CLK |

2 |

|

|

7 |

Q |

||||

|

|||||||||

|

|

|

|

4 |

|

|

|||

|

|

|

3 |

|

|

|

6 |

|

|

CLK |

|

|

|

Q |

|||||

|

|||||||||

VBB |

4 |

5 |

VEE |

||||||

MC10EL33

MC100EL33

8

1

D SUFFIX

PLASTIC SOIC PACKAGE

CASE 751-05

|

|

PIN DESCRIPTION |

||

|

|

|

|

|

|

PIN |

|

FUNCTION |

|

|

|

|

|

|

|

CLK |

|

Clock Inputs |

|

|

Reset |

|

Asynch Reset |

|

|

VBB |

|

Ref Voltage Output |

|

|

Q |

|

Data Ouputs |

|

|

|

|

|

|

|

|

|

|

|

5/95

Motorola, Inc. 1996 |

REV 3 |

Loading...

Loading...