Motorola MC10E136FNR2, MC10E136FN, MC100E136FNR2, MC100E136FN Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

6 Bit Universal Up/Down Counter |

MC10E136 |

|

The MC10E/100E136 is a 6-bit synchronous, presettable, cascadable |

MC100E136 |

|

universal counter. The device generates a look-ahead-carry output and |

|

|

accepts a look-ahead-carry input. These two features allow for the |

|

|

cacading of multiple E136's for wider bit width counters that operate at |

|

|

very nearly the same frequency as the stand alone counter. |

|

|

• 550 MHz Count Frequency |

6-BIT UNIVERSAL |

|

• Fully Synchronous Up and Down Counting |

UP/DOWN COUNTER |

|

• Internal 75 kΩ Input Pulldown Resistors |

||

|

||

• Look-Ahead-Carry Input and Output |

|

|

• Asynchronous Master Reset |

|

|

• Extended 100E VEE Range of ±4.2 V to ±5.46 V |

|

|

The CLOUT output will pulse LOW for one clock cycle one count |

|

|

before the E136 reaches terminal count. The COUT output will pulse |

|

|

LOW for one clock cycle when the counter reaches terminal count. For |

|

|

more information on utilizing the look-ahead-carry features of the device |

|

|

please refer to the applications section of this data sheet. The differential |

FN SUFFIX |

|

COUT output facilitates the E136's use in programmable divider and |

PLASTIC PACKAGE |

|

self-stopping counter applications. |

CASE 776-02 |

Unlike the H136 and other similar universal counter designs the E136 carry out and look-ahead-carry out signals are registered on chip. This

design alleviates the glitch problem seen on many counters where the carry out signals are merely gated. Because of this architecture there are some minor functional differences between the E136 and H136 counters. The user, regardless of familiarity with the H136, should read this data sheet carefully. Note specifically (see logic diagram) the operation of the carry out outputs and the look-ahead-carry in input when utilizing the master reset.

When left open all of the input pins will be pulled LOW via an input pulldown resistor. The master reset is an asynchronous signal which when asserted will force the Q outputs LOW.

The Q outputs need not be terminated for the E136 to function properly, in fact if these outputs will not be used in a system it is recommended to save power and minimize noise that they be left open. This practice will minimize switching noise which can reduce the maximum count frequency of the device or significantly reduce margins against other noise in the system.

PIN NAMES

|

|

Pin |

Function |

|

|

|

|

|

|

|

D0 ± D5 |

Preset Data Inputs |

||

|

Q0 ± Q5 |

Data Inputs |

||

|

S1, S2 |

Mode Control Pins |

||

|

MR |

Master Reset |

||

|

CLK |

|

Clock Input |

|

|

COUT, COUT |

Carry-Out Output (Active LOW) |

||

|

CLOUT |

Look-Ahead-Carry Out (Active LOW) |

||

|

CIN |

|

Carry-In Input (Active LOW) |

|

|

CLIN |

Look-Ahead-Carry In Input (Active LOW) |

||

FUNCTION TABLE (Expanded truth table on page 2±4)

S1 |

S2 |

CIN |

MR |

CLK |

Function |

|

|

|

|

|

|

L |

L |

X |

L |

Z |

Preset Parallel Data |

L |

H |

L |

L |

Z |

Increment (Count Up) |

L |

H |

H |

L |

Z |

Hold Count |

H |

L |

L |

L |

Z |

Decrement (Count Down) |

H |

L |

H |

L |

Z |

Hold Count |

H |

H |

X |

L |

Z |

Hold Count |

X |

X |

X |

H |

X |

Reset (Qn = LOW) |

|

|

|

|

|

|

|

|

|

|

|

|

D3 |

|

D4 |

|

D5 |

VCCO |

Q5 |

|

Q4 |

VCCO |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

24 |

23 |

22 |

|

21 |

20 |

19 |

|

||||||

|

D2 |

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

18 |

|||

|

S2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

|||

|

|

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

S1 |

|

|

|

|

|

Pinout: 28-lead PLCC |

16 |

|||||||||||

|

|

28 |

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||||||

VEE |

|

1 |

|

|

|

|

|

(Top View) |

|

|

15 |

||||||||

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

CLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

14 |

||||

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

CIN |

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

13 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 |

||

CLIN |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

5 |

6 |

7 |

8 |

|

9 |

10 |

11 |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MR |

|

D1 |

|

D0 |

VCCO |

Q0 |

|

Q1 |

VCCO |

||||

* All VCC and VCCO pins are tied together on the die.

5/95

Motorola, Inc. 1996 |

REV 2 |

Q3

Q2

VCC

VCCO

COUT

COUT

CLOUT

MOTOROLA

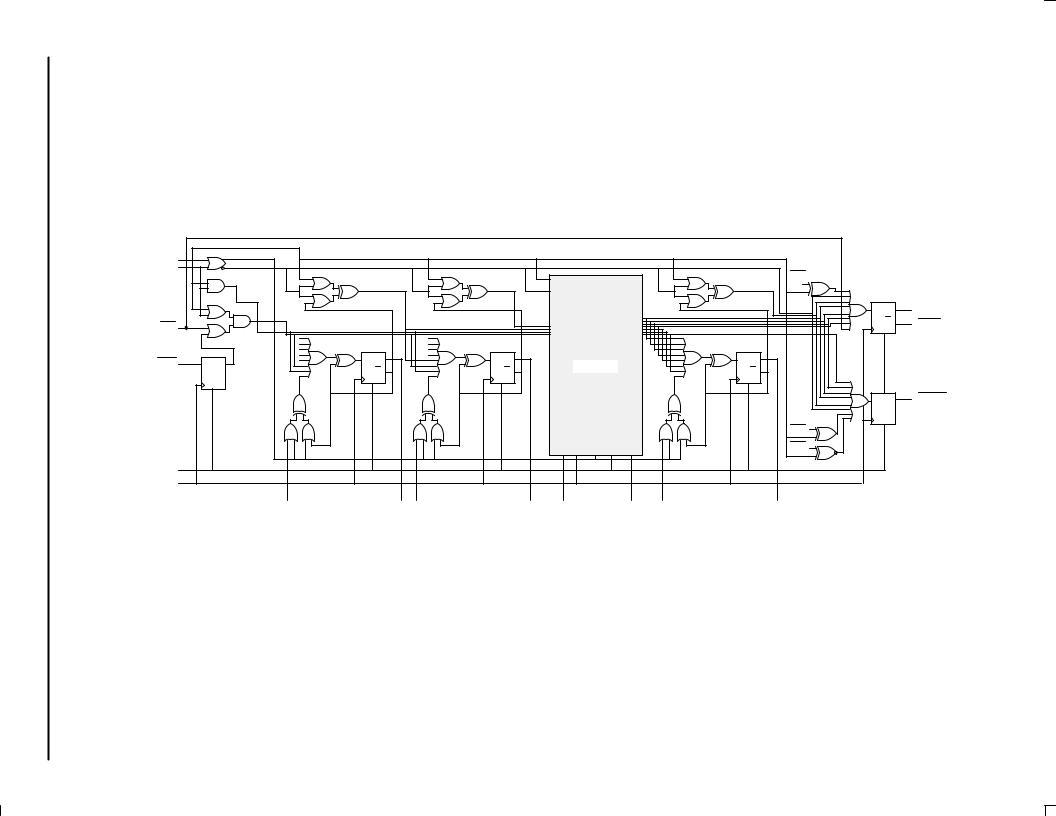

2±2 |

Counter Up/Down Universal E136 |

|

Diagram Logic |

MC100E136 MC10E136

S1 |

|

|

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

QM0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D Q |

COUT |

CIN |

|

|

|

|

|

|

S Q |

COUT |

CLIN |

D Q |

D Q |

D Q |

Bits 2 ± 4 |

|

|

D Q |

|

R Q |

R Q |

|

|

R Q |

|

|||

|

S |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D Q |

CLOUT |

|

|

|

|

|

|

|

S |

|

|

|

|

|

|

|

|

QM1 |

|

|

|

|

|

|

|

|

QM0 |

|

MR |

|

|

|

|

|

|

|

|

CLK |

|

|

|

|

|

|

|

|

|

D0 |

Q0 D1 |

Q1 |

D2 ± D4 |

Q2 ± Q4 |

D5 |

Q5 |

|

Note that this diagram is provided for understanding of logic operation only. It should not be used for propagation delays as many gate functions are achieved internally without incurring a full gate delay.

MC10E136 MC100E136

DC CHARACTERISTICS |

(VEE = VEE(min) to VEE(max); VCC = VCCO = GND) |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

0°C |

|

|

25°C |

|

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Characteristic |

Symbol |

Min |

Typ |

Max |

Min |

Typ |

Max |

|

Min |

Typ |

Max |

Unit |

Condition |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input HIGH Current |

IIH |

Ð |

Ð |

150 |

Ð |

Ð |

150 |

|

Ð |

Ð |

150 |

μA |

|

|||||

Power Supply Current |

IEE |

Ð |

125 |

150 |

Ð |

125 |

150 |

|

Ð |

125 |

150 |

mA |

|

|||||

|

10E |

|

|

|

|

|||||||||||||

|

100E |

|

Ð |

125 |

150 |

Ð |

125 |

150 |

|

Ð |

140 |

170 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AC CHARACTERISTICS |

(VEE = VEE(min) to VEE(max); VCC = VCCO = GND) |

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0°C |

|

|

25°C |

|

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Characteristic |

Symbol |

Min |

Typ |

Max |

Min |

Typ |

Max |

|

Min |

Typ |

Max |

Unit |

Condition |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Maximum Count Frequency |

fCOUNT |

550 |

650 |

Ð |

550 |

650 |

Ð |

|

550 |

650 |

Ð |

MHz |

|

|||||

Propagation Delay to Output |

tPLH |

|

|

|

|

|

|

|

|

|

|

ps |

|

|||||

|

CLK to Q |

tPHL |

850 |

1150 |

1450 |

850 |

1150 |

1450 |

|

850 |

1150 |

1450 |

|

|

||||

|

MR to Q |

|

850 |

1150 |

1450 |

850 |

1150 |

1450 |

|

850 |

1150 |

1450 |

|

|

||||

|

|

|

|

|

|

|

800 |

1150 |

1300 |

800 |

1150 |

1300 |

|

800 |

1150 |

1300 |

|

|

|

CLK to COUT |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CLK to CLOUT |

|

825 |

1150 |

1400 |

825 |

1150 |

1400 |

|

825 |

1150 |

1400 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Setup Time |

ts |

1000 |

650 |

Ð |

1000 |

650 |

Ð |

|

1000 |

650 |

Ð |

ps |

|

|||||

|

S1, S2 |

|

|

|

|

|||||||||||||

|

D |

|

|

800 |

400 |

Ð |

800 |

400 |

Ð |

|

800 |

400 |

Ð |

|

|

|||

|

CLIN |

|

150 |

0 |

Ð |

150 |

0 |

Ð |

|

150 |

0 |

Ð |

|

|

||||

|

CIN |

|

800 |

400 |

Ð |

800 |

400 |

Ð |

|

800 |

400 |

Ð |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Hold Time |

th |

150 |

±200 |

Ð |

150 |

±200 |

Ð |

|

150 |

±200 |

Ð |

ps |

|

|||||

|

S1, S2 |

|

|

|

|

|||||||||||||

|

D |

|

|

150 |

±250 |

Ð |

150 |

±250 |

Ð |

|

150 |

±250 |

Ð |

|

|

|||

|

CLIN |

|

300 |

0 |

Ð |

300 |

0 |

Ð |

|

300 |

0 |

Ð |

|

|

||||

|

CIN |

|

150 |

±250 |

Ð |

150 |

±250 |

Ð |

|

150 |

±250 |

Ð |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Reset Recovery Time |

tRR |

1000 |

700 |

Ð |

1000 |

700 |

Ð |

|

1000 |

700 |

Ð |

ps |

|

|||||

Minimum Pulse Width |

tPW |

700 |

400 |

Ð |

700 |

400 |

Ð |

|

700 |

400 |

Ð |

ps |

|

|||||

|

CLK, MR |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Rise/Fall Times |

tr |

|

|

|

|

|

|

|

|

|

|

ps |

|

|||||

|

COUT |

tf |

275 |

Ð |

600 |

275 |

Ð |

600 |

|

275 |

Ð |

600 |

|

20% - 80% |

||||

|

Other |

|

300 |

Ð |

700 |

300 |

Ð |

700 |

|

300 |

Ð |

700 |

|

|

||||

2±3 |

MOTOROLA |

Loading...

Loading...