Motorola MC10EL35D, MC10EL35DR2, MC100EL35DR2, MC100EL35D Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

JK Flip Flop

The MC10EL/100EL35 is a high speed JK flip-flop. The J/K data enters the master portion of the flip-flop when the clock is LOW and is transferred to the slave, and thus the outputs, upon a positive transition of the clock. The reset pin is asynchronous and is activated with a logic HIGH.

•525ps Propagation Delay

•2.2GHz Toggle Frequency

•High Bandwidth Output Transitions

•75kΩ Internal Input Pulldown Resistors

•>1000V ESD Protection

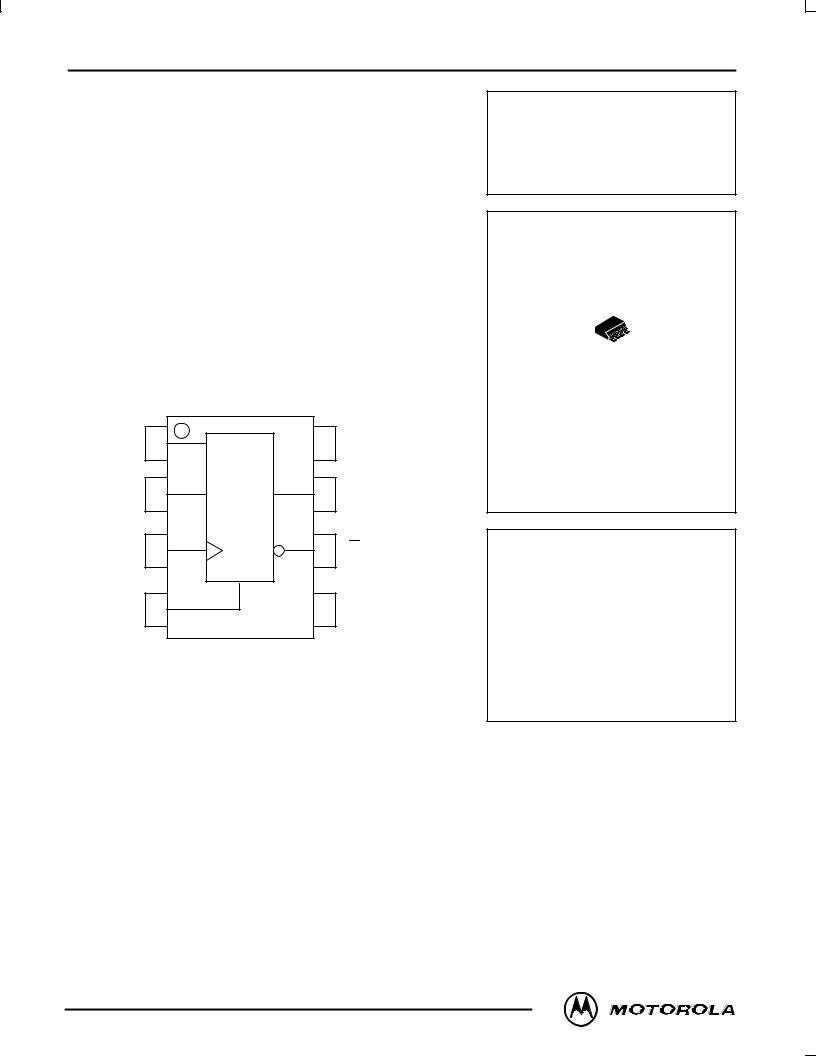

LOGIC DIAGRAM AND PINOUT ASSIGNMENT

J |

1 |

J |

8 |

VCC |

K |

2 |

K |

7 |

Q |

CLK |

3 |

|

6 |

Q |

|

|

|

R |

|

R |

4 |

|

5 |

VEE |

MC10EL35

MC100EL35

8

1

D SUFFIX

PLASTIC SOIC PACKAGE

CASE 751-05

TRUTH TABLE

J |

K |

R |

CLK |

Qn+1 |

||

|

|

|

|

|

|

|

L |

L |

L |

Z |

|

Qn |

|

L |

H |

L |

Z |

|

L |

|

H |

L |

L |

Z |

|

H |

|

H |

H |

L |

Z |

|

Qn |

|

X |

X |

H |

X |

|

L |

|

|

|

|

|

|

|

|

Z = LOW to HIGH Transition

12/93

Motorola, Inc. 1996 |

REV 2 |

Loading...

Loading...