Motorola MC10E446FN, MC100E446FN, MC100E446FNR2, MC10E446FNR2 Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

4 Bit Parallel/Serial Converter |

|

MC10E446 |

The MC10E/100E446 is an integrated 4-bit parallel to serial data |

|

MC100E446 |

converter. The device is designed to operate for NRZ data rates of up to |

|

|

1.3Gb/s. The chip generates a divide by 4 and a divide by 8 clock for both |

|

|

4-bit conversion and a two chip 8-bit conversion function. The conversion |

|

|

|

|

|

sequence was chosen to convert the parallel data into a serial stream |

|

|

|

|

|

from bit D0 to D3. A serial input is provided to cascade two E446 devices |

|

|

for 8 bit conversion applications. Note that the serial output data clocks off |

4-BIT PARALLEL/ |

|

of the negative input clock transition. |

||

SERIAL CONVERTER

•On Chip Clock 4 and 8

•1.5 Gb/s Typical Data Rate Capability

•Differential Clock and Serial Inputs

•VBB Output for Single-ended Input Applications

•Asynchronous Data Synchronization

•Mode Select to Expand to 8 Bits

• Internal 75kΩ Input Pulldown Resistors

• Extended 100E VEE Range of -4.2V to -5.46V

The SYNC input will asynchronously reset the internal clock circuitry. |

FN SUFFIX |

|

This pin allows the user to reset the internal clock conversion unit and |

||

PLASTIC PACKAGE |

||

thus select the start of the conversion process. |

||

CASE 776-02 |

The MODE input is used to select the conversion mode of the device. With the MODE input LOW, or open, the device will function as a 4-bit converter. When the mode input is driven HIGH the internal load clock will

change on every eighth clock cycle thus allowing for an 8-bit conversion scheme using two E446's. When cascaded in an 8-bit conversion scheme the devices will not operate at the 1.3Gb/s data rate of a single device. Refer to the applications section of this data sheet for more information on cascading the E446.

For lower data rate applications a VBB reference voltage is supplied for single-ended inputs. When operating at clock rates above 500MHz differential input signals are recommended. For single-ended inputs the VBB pin is tied to the inverting differential input and bypassed via a 0.01μF capacitor. The VBB provides the switching reference for the input differential amplifier. The VBB can also be used to AC couple an input signal, for more information on AC coupling refer to the interfacing section of the design guide in the ECLinPS data book.

PIN NAMES |

|

|

|

|

|

|

|

|

|

Pinout: 28-Lead PLCC (Top View) |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 |

D1 |

D2 |

D3 |

MODE |

NC |

NC |

|

|

|

Pin |

|

|

|

Function |

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

24 |

|

23 |

22 |

21 |

20 |

19 |

|

|

||

SIN |

|

Differential Serial Data Input |

CLK |

26 |

25 |

|

NC |

|||||||||||||||

D0 ± D3 |

|

Parallel Data Inputs |

|

|

|

|

|

|

|

18 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SOUT, SOUT |

|

Differential Serial Data Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

CLK |

27 |

|

|

|

|

|

|

|

17 |

NC |

||||||||||||

CLK, CLK |

|

Differential Clock Inputs |

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

CL/4, CL/4 |

|

Differential 4 Clock Output |

VBB |

28 |

|

|

|

|

|

|

|

16 |

VCC |

|||||||||

CL/8, CL/8 |

|

Differential |

|

|

|

|

|

|

|

|

||||||||||||

|

8 Clock Output |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

MODE |

|

Conversion Mode 4-Bit/8-Bit |

VEE |

1 |

|

|

|

|

|

|

|

15 |

SOUT |

|||||||||

SYNC |

|

Conversion Synchronizing Input |

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FUNCTION TABLES |

|

|

|

|

SIN |

2 |

|

|

|

|

|

|

|

14 |

SOUT |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

SIN |

3 |

|

|

|

|

|

|

|

13 |

VCCO |

|||||

|

|

Mode |

|

Conversion |

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

L |

|

|

4-Bit |

SYNC |

4 |

|

|

|

|

|

|

|

12 |

NC |

|||||

|

|

|

H |

|

8-Bit |

|

|

|

|

|

|

5 |

6 |

|

7 |

8 |

9 |

10 |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

VCCO CL/8 |

CL/8 VCCO CL/4 |

CL/4 VCCO |

|

|

|||||

7/96

Motorola, Inc. 1996 |

REV 2 |

MC10E446 MC100E446

|

|

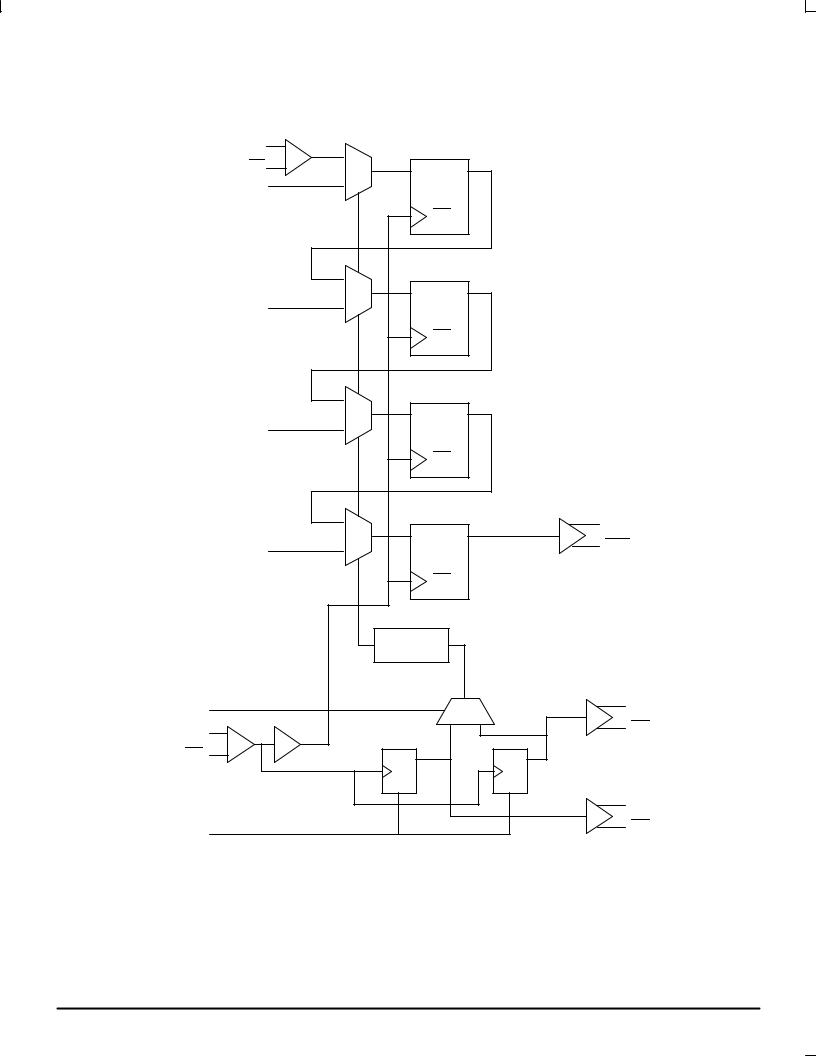

LOGIC DIAGRAM |

|

SIN |

|

0 |

|

SIN |

|

|

|

|

D |

Q |

|

D3 |

|

1 |

|

|

|

CLK |

|

|

|

0 |

|

|

|

D |

Q |

D2 |

|

1 |

|

|

|

CLK |

|

|

|

0 |

|

|

|

D |

Q |

D1 |

|

1 |

|

|

|

CLK |

|

|

|

0 |

SOUT |

|

|

D |

Q |

D0 |

|

1 |

SOUT |

|

|

||

|

|

CLK |

|

|

|

LOAD PULSE |

|

|

|

GENERATOR |

|

Mode |

|

0 |

CL/8 |

|

|

1 |

|

CLK |

|

|

CL/8 |

|

|

|

|

CLK |

Delay |

4 |

8 |

|

|

|

|

|

|

R |

R |

|

|

|

CL/4 |

SYNC |

|

|

CL/4 |

|

|

|

MOTOROLA |

2±2 |

Loading...

Loading...