Motorola MC100LVEL51DR2, MC100LVEL51, MC100LVEL51D Datasheet

SEMICONDUCTOR TECHNICAL DATA

4–1

REV 1

Motorola, Inc. 1996

8/96

The MC100LVEL51 is a differential clock D flip-flop with reset. The

device is functionally equivalent to the EL51 device, but operates from a

low voltage supply. With propagation delays and output transition times

essentially equal to the EL51, the LVEL51 is ideally suited for those

applications which require the ultimate in AC performance at 3.3V V

CC

.

The reset input is an asynchronous, level triggered signal. Data enters

the master portion of the flip-flop when the clock is LOW and is

transferred to the slave, and thus the outputs, upon a positive transition of

the clock. The differential clock inputs of the LVEL51 allow the device to

be used as a negative edge triggered flip-flop.

The differential input employs clamp circuitry to maintain stability under

open input conditions. When left open, the CLK input will be pulled down

to V

EE

and the CLK

input will be biased at V

CC

/2.

• 475ps Propagation Delay

• 2.8GHz Toggle Frequency

• Operates from –3.3V (or 3.3V) Supply

• 75kΩ Internal Input Pulldown Resistors

• >2000V ESD Protection

1

2

3

4 5

6

7

8

Q

V

EE

V

CC

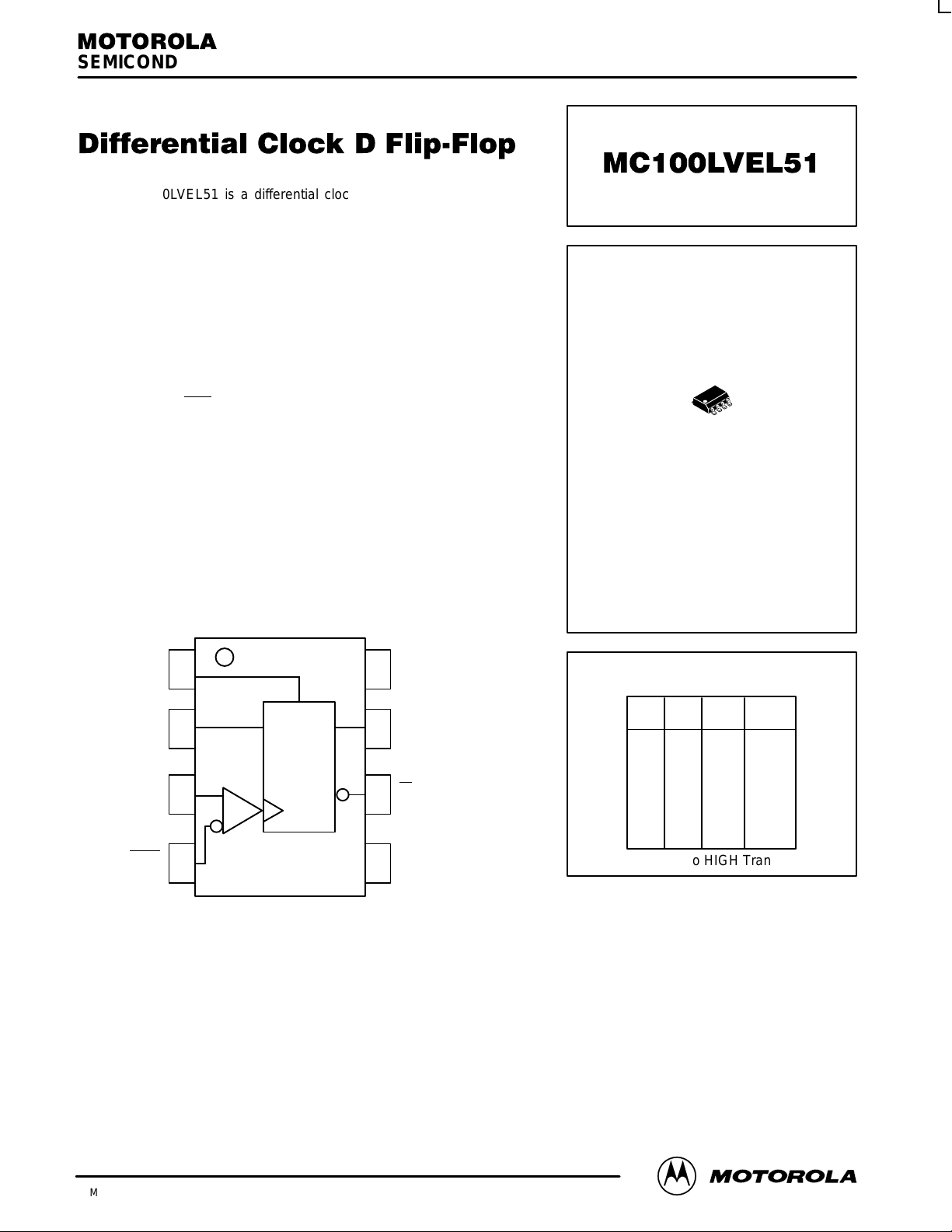

LOGIC DIAGRAM AND PINOUT ASSIGNMENT

D

QCLK

CLK

R

D

R

Flip-Flop

TRUTH TABLE

D

L

H

X

R

L

L

H

CLK

Z

Z

X

Q

L

H

L

Z = LOW to HIGH Transition

1

8

D SUFFIX

PLASTIC SOIC PACKAGE

CASE 751-05

Loading...

Loading...