MOTOROLA MC10176FN, MC10176P, MC10176FNR2 Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Hex D Master/Slave Flip-Flop

The MC10176 contains six high-speed, master slave type ªDº flip-flops. Clocking is common to all six flip-flops. Data is entered into the master when the clock is low. Master to slave data transfer takes place on the positive-going Clock transition. Thus, outputs may change only on a positive-going Clock transition. A change in the information present at the data (D) input will not affect the output information any other time due to the master-slave construction of this device.

PD = 460 mW typ/pkg (No Load)

ftoggle= 150 MHz (typ)

tr, tf = 2.0 ns typ (20%±80%)

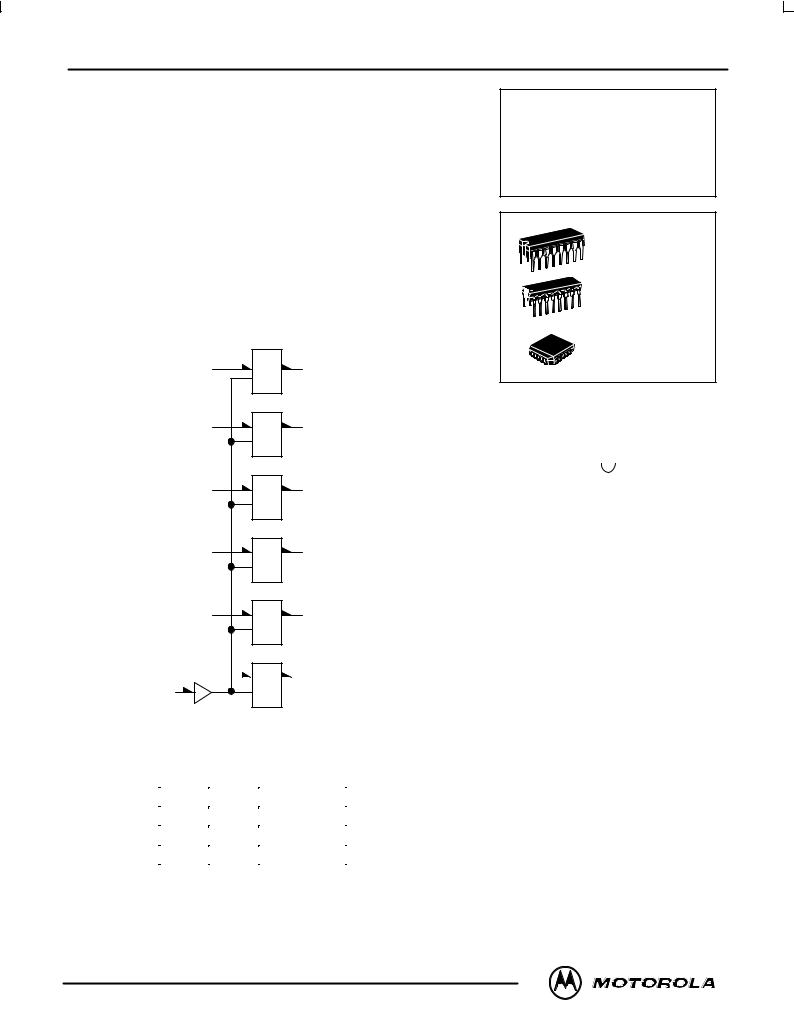

LOGIC DIAGRAM

D0 |

5 |

2 |

Q0 |

D1 |

6 |

3 |

Q1 |

D2 |

7 |

4 |

Q2 |

D3 |

10 |

13 |

Q3 |

D4 |

11 |

14 |

Q4 |

D5 |

12 |

|

|

|

15 |

Q5 |

|

|

CLOCK 9

VCC1 = PIN 1

VCC2 = PIN 16

VEE = PIN 8

CLOCKED TRUTH TABLE

C |

D |

Qn+1 |

L |

X |

Qn |

H* |

L |

L |

|

|

|

H* |

H |

H |

|

|

|

*A clock H is a clock transition from a low to a high state.

MC10176

L SUFFIX

CERAMIC PACKAGE

CASE 620±10

P SUFFIX

PLASTIC PACKAGE

CASE 648±08

FN SUFFIX

PLCC

CASE 775±02

DIP

PIN ASSIGNMENT

VCC1 |

|

1 |

|

16 |

|

VCC2 |

|

|

|

||||

Q0 |

|

2 |

|

15 |

|

Q5 |

|

|

|

||||

Q1 |

|

3 |

|

14 |

|

Q4 |

|

|

|

||||

Q2 |

|

4 |

|

13 |

|

Q3 |

|

|

|

||||

D0 |

|

5 |

|

12 |

|

D5 |

|

|

|

||||

D1 |

|

6 |

|

11 |

|

D4 |

|

|

|

||||

D2 |

|

7 |

|

10 |

|

D3 |

|

|

|

||||

VEE |

|

8 |

|

9 |

|

CLOCK |

|

|

|

||||

|

|

|

|

|

|

|

Pin assignment is for Dual±in±Line Package. For PLCC pin assignment, see the Pin Conversion Tables on page 6±11 of the Motorola MECL Data Book (DL122/D).

3/93

Motorola, Inc. 1996 |

3±131 |

REV 5 |

MC10176

ELECTRICAL CHARACTERISTICS

|

|

|

|

|

|

|

Test Limits |

|

|

|

|

||

|

|

|

Pin |

|

|

|

|

|

|

|

|

|

|

|

|

|

±30°C |

|

|

+25°C |

|

+85°C |

|

||||

|

|

|

Under |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Characteristic |

Symbol |

Test |

Min |

Max |

Min |

|

Typ |

|

Max |

Min |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply Drain Current |

IE |

8 |

|

121 |

|

|

88 |

|

110 |

|

121 |

mAdc |

|

Input Current |

|

IinH |

5 |

|

350 |

|

|

|

|

220 |

|

220 |

μAdc |

|

|

|

9 |

|

495 |

|

|

|

|

310 |

|

310 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IinL |

5 |

0.5 |

|

0.5 |

|

|

|

|

0.3 |

|

μAdc |

|

|

|

9 |

0.5 |

|

0.5 |

|

|

|

|

0.3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Voltage |

Logic 1 |

VOH |

2[ |

±1.060 |

±0.890 |

±0.960 |

|

|

|

±0.810 |

±0.890 |

±0.700 |

Vdc |

|

|

|

15[ |

±1.060 |

±0.890 |

±0.960 |

|

|

|

±0.810 |

±0.890 |

±0.700 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Output Voltage |

Logic 0 |

VOL |

2[ |

±1.890 |

±1.675 |

±1.850 |

|

|

|

±1.650 |

±1.825 |

±1.615 |

Vdc |

|

|

|

15[ |

±1.890 |

±1.675 |

±1.850 |

|

|

|

±1.650 |

±1.825 |

±1.615 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Threshold Voltage |

Logic 1 |

VOHA |

2[ |

±1.080 |

|

±0.980 |

|

|

|

|

±0.910 |

|

Vdc |

|

|

|

15[ |

±1.080 |

|

±0.980 |

|

|

|

|

±0.910 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Threshold Voltage |

Logic 0 |

VOLA |

2[ |

|

±1.655 |

|

|

|

|

±1.630 |

|

±1.595 |

Vdc |

|

|

|

15[ |

|

±1.655 |

|

|

|

|

±1.630 |

|

±1.595 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Switching Times |

(50Ω Load) |

|

|

|

|

|

|

|

|

|

|

|

ns |

Clock Input |

|

|

|

|

|

|

|

|

|

|

|

|

|

Propagation Delay |

t9+2+ |

2 |

1.6 |

4.6 |

1.6 |

|

|

|

4.5 |

1.6 |

5.0 |

|

|

|

|

t9+2± |

2 |

1.6 |

4.6 |

1.6 |

|

|

|

4.5 |

1.6 |

5.0 |

|

Rise Time |

(20 to 80%) |

t2+ |

2 |

1.0 |

4.1 |

1.1 |

|

|

|

4.0 |

1.1 |

4.4 |

|

Fall Time |

(20 to 80%) |

t2± |

2 |

1.0 |

4.1 |

1.1 |

|

|

|

4.0 |

1.1 |

4.4 |

|

Setup Time |

|

tsetup |

2 |

2.5 |

|

2.5 |

|

|

|

|

2.5 |

|

ns |

Hold Time |

|

thold |

2 |

1.5 |

|

1.5 |

|

|

|

|

1.5 |

|

ns |

Toggle Frequency (Max) |

ftog |

2 |

125 |

|

125 |

|

150 |

|

|

125 |

|

MHz |

|

[ Output level to be measured after a clock pulse has been applied to the C Input (Pin 9)

VIHmax VILmin

VIHmax VILmin

MOTOROLA |

3±132 |

MECL Data |

|

|

DL122 Ð Rev 6 |

Loading...

Loading...