Motorola MC10ELT22D, MC10ELT22DR2, MC100ELT22DR2, MC100ELT22D Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

Dual |

TTL to Differential |

MC10ELT22 |

|

|

|

PECL |

Translator |

MC100ELT22 |

|

|

|

|

|

|

The MC10ELT/100ELT22 is a dual TTL to differential PECL translator. Because PECL (Positive ECL) levels are used only +5V and ground are required. The small outline 8-lead SOIC package and the low skew, dual gate design of the ELT22 makes it ideal for applications which require the translation of a clock and a data signal. Because the mature MOSAIC 1.5 process is used, low cost can be added to the list of features.

The ELT22 is available in both ECL standards: the 10ELT is compatible with positive MECL 10H logic levels while the 100ELT is compatible with positive ECL 100K logic levels.

•1.5ns Typical Propagation Delay

•<300ps Typical Output to Output Skew

•Differential PECL Outputs

•Small Outline SOIC Package

•PNP TTL Inputs for Minimal Loading

•Flow Through Pinouts

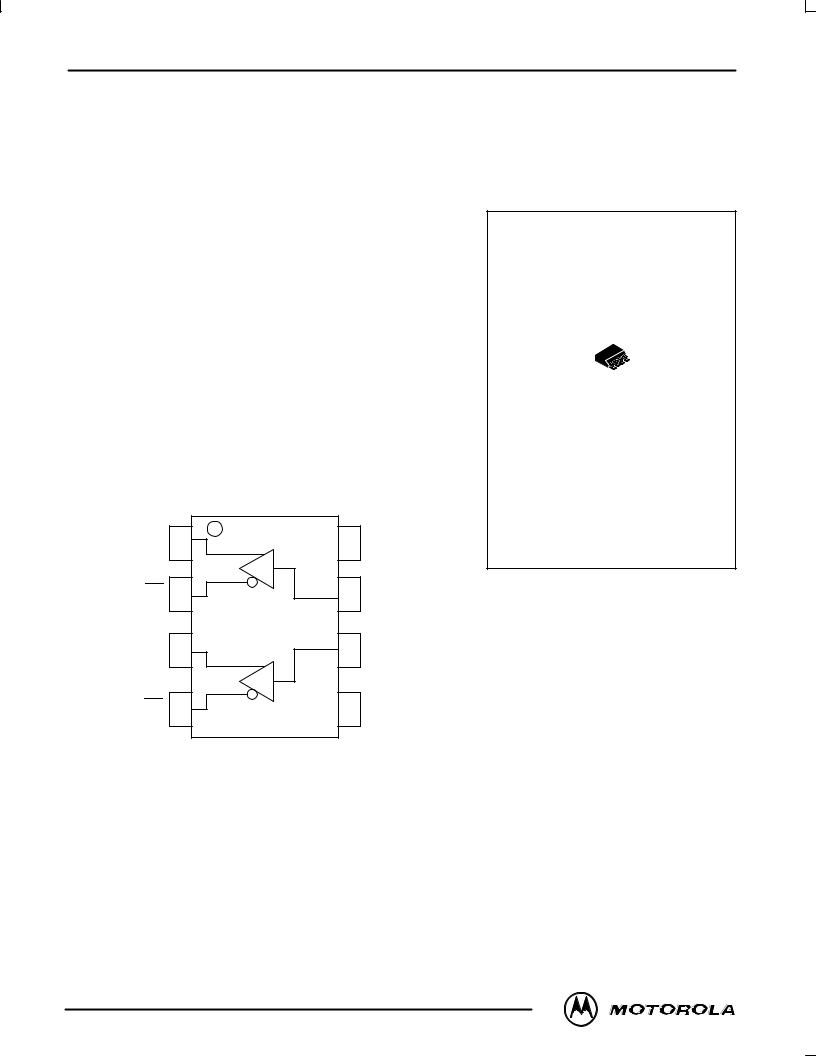

LOGIC DIAGRAM AND PINOUT ASSIGNMENT

Q0 |

1 |

8 |

VCC |

Q0 |

2 |

7 |

D0 |

|

PECL |

TTL |

|

Q1 |

3 |

6 |

D1 |

Q1 |

4 |

5 |

GND |

8

1

D SUFFIX

PLASTIC SOIC PACKAGE

CASE 751-05

|

|

PIN DESCRIPTION |

|

|

|

|

|

|

|

|

PIN |

|

FUNCTION |

|

|

|

|

|

|

|

Qn |

|

Diff PECL Outputs |

|

|

Dn |

|

TTL Inputs |

|

|

VCC |

|

+5.0V Supply |

|

|

GND |

|

Ground |

|

|

|

|

|

|

|

|

|

|

|

7/96

Motorola, Inc. 1996 |

REV 3 |

Loading...

Loading...