Motorola MC10H016FN, MC10H016FNR2, MC10H016L, MC10H016P Datasheet

MOTOROLA

SEMICONDUCTOR TECHNICAL DATA

4-Bit Binary Counter

The MC10H016 is a high±speed synchronous, presettable, cascadable 4±bit binary counter. It is useful for a large number of conversion, counting and digital integration applications.

•Counting Frequency, 200 MHz Minimum

•Improved Noise Margin 150 mV (Over Operating Voltage and Temperature Range)

•Voltage Compensated

•MECL 10K±Compatible

•Positive Edge Triggered

MAXIMUM RATINGS

|

|

|

Characteristic |

|

|

|

|

Symbol |

|

|

Rating |

|

|

Unit |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Power Supply (VCC = 0) |

|

|

|

|

|

VEE |

|

|

±8.0 to 0 |

|

|

Vdc |

|||||||

Input Voltage (VCC = 0) |

|

|

|

|

|

VI |

|

|

0 to VEE |

|

|

Vdc |

|||||||

Output Current Ð Continuous |

|

|

|

|

|

Iout |

|

|

50 |

|

|

|

mA |

||||||

|

|

Ð Surge |

|

|

|

|

|

|

|

|

100 |

|

|

|

|

|

|||

Operating Temperature Range |

|

|

|

|

TA |

|

|

0 to +75 |

|

|

|

°C |

|||||||

Storage Temperature Range Ð Plastic |

|

|

|

|

Tstg |

|

±55 to +150 |

|

|

|

°C |

||||||||

|

|

|

|

|

|

Ð Ceramic |

|

|

|

|

|

|

±55 to +165 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

ELECTRICAL CHARACTERISTICS (VEE = ±5.2 V ±5%) (See Note) |

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

0° |

|

25° |

|

75° |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Characteristic |

|

Symbol |

Min |

|

Max |

Min |

Max |

Min |

|

Max |

|

Unit |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Power Supply Current |

|

IE |

Ð |

|

126 |

Ð |

115 |

Ð |

|

126 |

|

mA |

|||||||

Input Current High |

|

IinH |

|

|

|

|

|

|

|

|

|

|

|

|

μA |

||||

All Except MR |

|

|

Ð |

|

450 |

Ð |

265 |

Ð |

|

265 |

|

|

|||||||

Pin 12 MR |

|

|

Ð |

|

1190 |

Ð |

700 |

Ð |

|

700 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Input Current Low |

|

IinL |

0.5 |

|

Ð |

|

0.5 |

Ð |

0.3 |

|

Ð |

|

|

μA |

|||||

High Output Voltage |

|

VOH |

±1.02 |

|

±0.84 |

±0.98 |

±0.81 |

±0.92 |

|

±0.735 |

|

Vdc |

|||||||

Low Output Voltage |

|

VOL |

±1.95 |

|

±1.63 |

±1.95 |

±1.63 |

±1.95 |

|

±1.60 |

|

Vdc |

|||||||

High Input Voltage |

|

VIH |

±1.17 |

|

±0.84 |

±1.13 |

±0.81 |

±1.07 |

|

±0.735 |

|

Vdc |

|||||||

Low Input Voltage |

|

VIL |

±1.95 |

|

±1.48 |

±1.95 |

±1.48 |

±1.95 |

|

±1.45 |

|

Vdc |

|||||||

AC PARAMETERS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Propagation Delay |

|

tpd |

|

|

|

|

|

|

|

|

|

|

|

|

ns |

||||

Clock to Q |

|

|

1.0 |

|

2.4 |

1.0 |

2.5 |

1.0 |

|

2.7 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

Clock to TC |

|

|

0.7 |

|

2.4 |

0.7 |

2.5 |

0.7 |

|

2.6 |

|

|

|||||||

MR to Q |

|

|

0.7 |

|

2.4 |

0.7 |

2.5 |

0.7 |

|

2.6 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Set±up Time |

|

tset |

|

|

|

|

|

|

|

|

|

|

|

|

ns |

||||

Pn to Clock |

|

|

2.0 |

|

Ð |

|

2.0 |

Ð |

2.0 |

|

Ð |

|

|

|

|||||

CE or PE to Clock |

|

|

2.5 |

|

Ð |

|

2.5 |

Ð |

2.5 |

|

Ð |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

Hold Time |

|

thold |

|

|

|

|

|

|

|

|

|

|

|

|

ns |

||||

Clock to Pn |

|

|

|

|

1.0 |

|

Ð |

|

1.0 |

Ð |

1.0 |

|

Ð |

|

|

|

|||

Clock to CE or PE |

|

|

0.5 |

|

Ð |

|

0.5 |

Ð |

0.5 |

|

Ð |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

Counting Frequency |

|

fcount |

200 |

|

Ð |

|

200 |

Ð |

200 |

|

Ð |

|

|

MHz |

|||||

Rise Time |

|

tr |

0.5 |

|

2.0 |

0.5 |

2.1 |

0.5 |

|

2.2 |

|

ns |

|||||||

Fall Time |

|

tf |

0.5 |

|

2.0 |

0.5 |

2.1 |

0.5 |

|

2.2 |

|

ns |

|||||||

NOTE:

Each MECL 10H series circuit has been designed to meet the dc specifications shown in the test table, after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse air flow greater than 500 Ifpm is maintained. Outputs are terminated through a 50±ohm resistor to ±2.0 volts.

MC10H016

L SUFFIX

CERAMIC PACKAGE

CASE 620±10

P SUFFIX

PLASTIC PACKAGE

CASE 648±08

FN SUFFIX

PLCC

CASE 775±02

DIP

PIN ASSIGNMENT

VCC1 |

|

1 |

|

16 |

|

VCC2 |

||

|

|

|

||||||

|

Q1 |

|

2 |

|

15 |

|

Q2 |

|

|

|

|

|

|||||

|

Q0 |

|

3 |

|

14 |

|

Q3 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

CP |

|

TC |

|

4 |

|

13 |

|

||

|

|

|

|

|||||

|

|

|

|

|

|

|

|

MR |

|

PE |

|

5 |

|

12 |

|

||

|

|

|

|

|||||

|

|

|

|

|

|

|

|

P3 |

CE |

|

6 |

|

11 |

|

|||

|

|

|

||||||

PO |

|

7 |

|

10 |

|

P2 |

||

|

|

|

||||||

VEE |

|

8 |

|

9 |

|

P1 |

||

|

|

|

||||||

|

|

|

|

|

|

|

|

|

Pin assignment is for Dual±in±Line Package. For PLCC pin assignment, see the Pin Conversion Tables on page 6±11 of the Motorola MECL Data Book (DL122/D).

TRUTH TABLE

CE |

PE |

MR |

CP |

Function |

|

|

|

|

|

L |

L |

L |

Z |

Load Parallel (Pn to Qn) |

H |

L |

L |

Z |

Load Parallel (Pn to Qn) |

L |

H |

L |

Z |

Count |

H |

H |

L |

Z |

Hold |

X |

X |

L |

ZZ |

Masters Respond; |

|

|

|

|

Slaves Hold |

X |

X |

H |

X |

Reset (Qn = LOW, |

|

|

|

|

TC = HIGH) |

Z = Clock Pulse (Low to High); ZZ = Clock Pulse (High to Low)

Features include assertion inputs and outputs on each of the four master/slave counting flip±flops. Terminal count is generated internally in a manner that allows synchronous loading at nearly the speed of the basic counter.

9/96

Motorola, Inc. 1996 |

2±1 |

REV 6 |

MOTOROLA

2±2

Data MECL

6 Rev Ð DL122

|

|

|

|

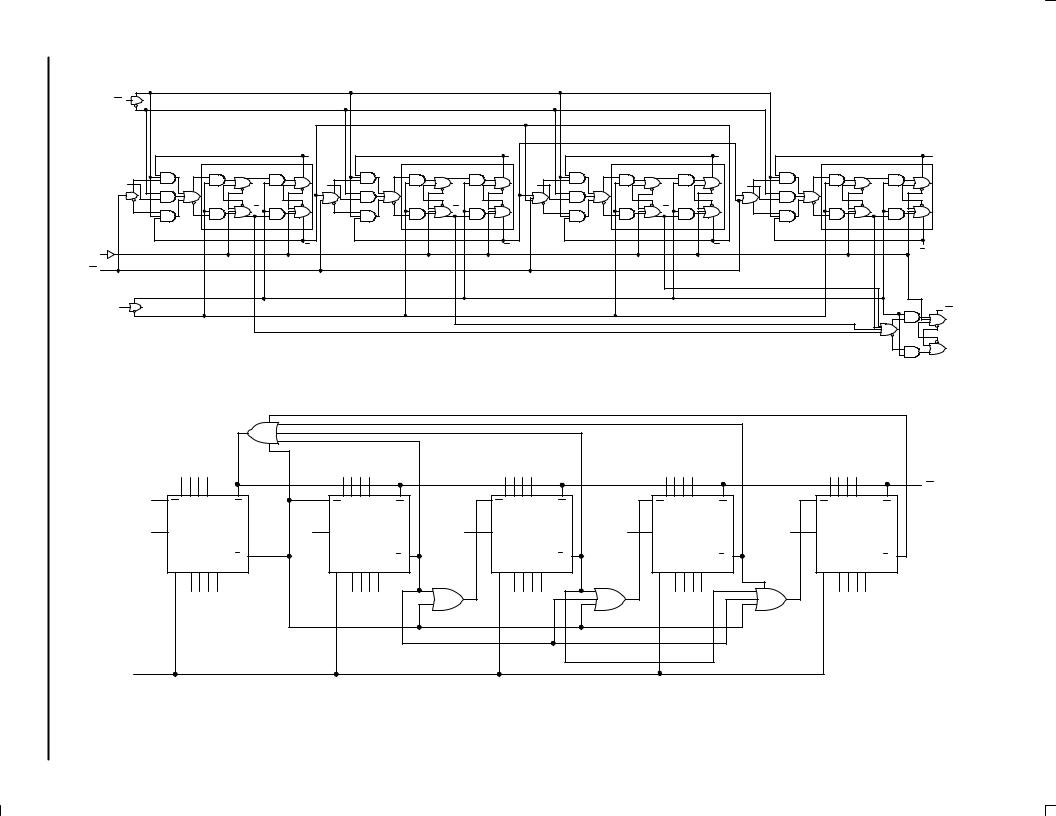

4±Bit Binary Counter Logic Diagram |

|

|

|

||||

PE |

|

|

|

|

|

|

|

|

|

|

|

|

|

Q0 |

|

|

|

Q1 |

|

|

|

Q2 |

Q3 |

MASTER |

Q |

SLAVE |

P1 |

MASTER |

Q |

SLAVE |

P2 |

MASTER |

Q |

SLAVE |

P3 |

P0 |

|

|

|

|

|

|

|

|

|

|

|

|

Q |

|

|

|

Q |

|

|

|

Q |

|

|

MR |

|

Q |

|

|

|

Q |

|

|

|

Q |

Q |

|

|

|

|

|

|

|

|

|

|

||

CE |

|

|

|

|

|

|

|

|

|

|

|

CP |

|

|

|

|

|

|

|

|

|

|

TC |

|

|

|

|

|

|

|

|

|

|

|

|

Note that this diagram is provided for understanding of logic operation only. It should not be used for evaluation of propagation delays as many gate functions are achieved internally without incurring a full gate delay.

|

1/2 10H109 |

|

|

|

|

|

|

|

|

|

Q0±Q3 |

Q0±Q3 |

|

Q0±Q3 |

|

Q0±Q3 |

|

Q0±Q3 |

|

|

|

|

|

|

|

|

|

|

FO |

CE |

PE |

CE |

PE |

CE |

PE |

CE |

PE |

CE |

PE |

|

LSB |

|

|

|

|

|

|

MSB |

|

MR |

MR |

|

MR |

|

MR |

|

MR |

|

|

C |

Tc |

C |

Tc |

C |

Tc |

C |

Tc |

C |

Tc |

|

|

|

|

|

|||||

|

P0±P3 |

P0±P3 |

|

P0±P3 |

|

P0±P3 |

|

P0±P3 |

|

|

|

|

|

1/2 10H109 |

|

1/2 10H109 |

|

1/2 10H109 |

|

CLOCK

N Counter 1 to 16 5

MC10H016 Cascaded for 5 Stage Presettable Counter

Max freq. is only OR gate delay below max when counting alone.

MC10H016

Loading...

Loading...