MOTOROLA MC100EPT25D, MC100EPT25DT, MC100EPT25DTR2 Datasheet

MC100EPT25

Differential LVECL/ECL to LVTTL Translator

The MC100EPT25 is a Differential LVECL/ECL to LVTTL translator. This device requires +3.3V, ±3.3V to ±5.2V, and ground. The small outline 8±lead SOIC package and the single gate of the EPT25 make it ideal for applications which require the translation of a clock or data signal.

The VBB output allows the EPT25 to also be used in a single±ended input mode. In this mode the VBB output is tied to the D input for a non±inverting buffer or the D input for an inverting buffer. If used, the VBB pin should be bypassed to ground via a 0.01mF capacitator.

•1.1ns Typical Propagation Delay

•275MHz Fmax (Clock bit stream, not pseudo±random)

•Differential LVECL/ECL inputs

•Small Outline SOIC Package

•24mA TTL outputs

•Flow Through Pinouts

•Internal Input Resistors: Pulldown on D, Pulldown and Pullup on D

•Q Output will default LOW with inputs open or at GND

•ESD Protection: >4000V HBM, >200V MM

•VBB Output

•New Differential Input Common Mode Range

•Moisture Sensitivity Level 1, Indefinite Time Out of Drypack. For Additional Information, See Application Note AND8003/D

•Flammability Rating: UL±94 code V±0 @ 1/8º, Oxygen Index 28 to 34

•Transistor Count = 111 devices

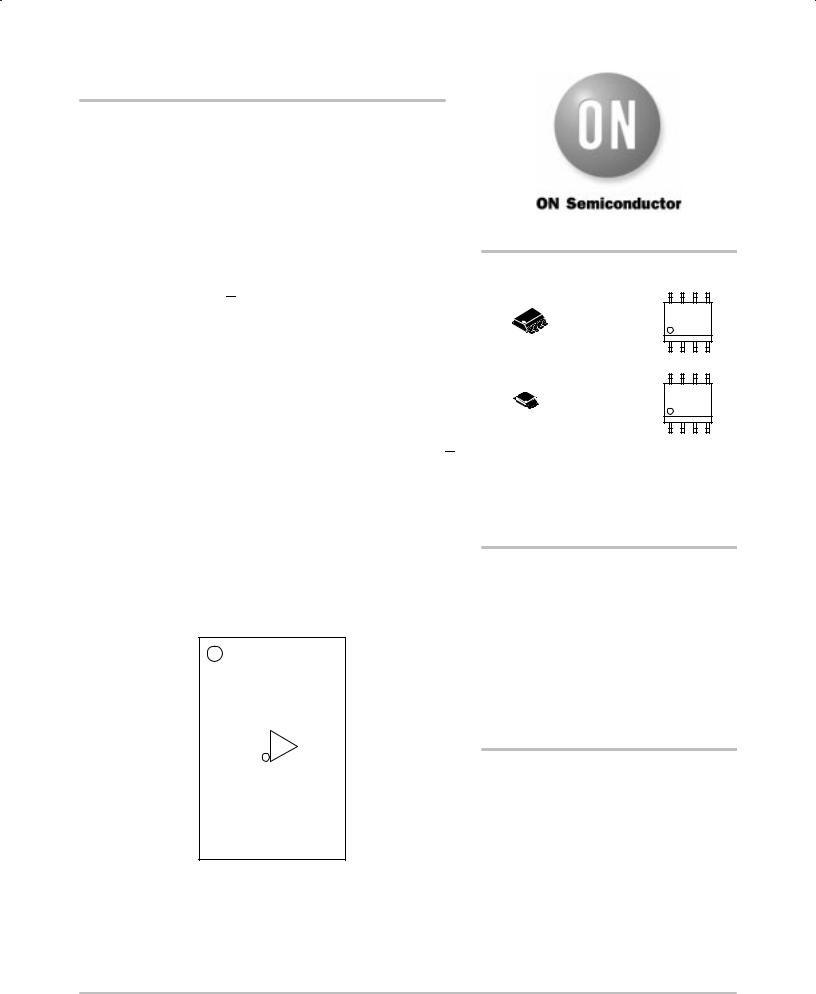

VEE |

1 |

|

|

|

|

|

8 |

VCC |

|

|

|

|

LVTTL |

|

|

||

D |

2 |

|

|

7 |

Q |

|||

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

http://onsemi.com

|

|

MARKING |

|

|

|

DIAGRAMS* |

|

|

|

8 |

|

|

SO±8 |

HPT25 |

|

8 |

D SUFFIX |

ALYW |

|

1 |

CASE 751 |

|

|

|

1 |

||

|

|

||

|

|

8 |

|

8 |

TSSOP±8 |

HR25 |

|

DT SUFFIX |

|||

ALYW |

|||

1 |

CASE 948R |

|

|

|

|

1 |

|

A |

= Assembly Location |

||

L |

= Wafer Lot |

|

|

Y |

= Year |

|

|

W = Work Week

*For additional information, see Application Note AND8002/D

|

|

|

PIN DESCRIPTION |

|

|

|

|

PIN |

FUNCTION |

||

|

|

|

|

Q |

LVTTL Output |

||

|

|

|

|

D, |

|

|

Differential LVECL Input Pair |

D |

|||

|

|

||

VCC |

Positive Supply |

||

VBB |

Output Reference Voltage |

||

GND |

Ground |

||

|

|

||

VEE |

Negative Supply |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D |

3 |

|

|

|

|

6 |

NC |

ORDERING INFORMATION |

|||

LVECL |

|

|

||||||||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Device |

Package |

Shipping |

|

|

|

|

|

|

|

|

|

|

MC100EPT25D |

SO±8 |

98 Units / Rail |

VBB |

4 |

|

|

|

|

5 |

GND |

|||||

|

|

|

|

|

|

|

||||||

|

|

|

|

MC100EPT25DR2 |

SO±8 |

2500 / Reel |

||||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MC100EPT25DT |

TSSOP±8 |

98 Units / Rail |

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 1. 8±Lead Pinout |

(Top View) and Logic Diagram |

MC100EPT25DTR2 |

TSSOP±8 |

2500 / Reel |

||||||||

|

|

|

||||||||||

|

|

|

||||||||||

Semiconductor Components Industries, LLC, 2000 |

1 |

Publication Order Number: |

May, 2000 ± Rev. 1 |

|

MC100EPT25/D |

MC100EPT25

MAXIMUM RATINGS*

Symbol |

Parameter |

|

Value |

Unit |

|

|

|

|

|

VCC |

Power Supply (Referenced to GND, VEE = ±3.3V) |

|

0 to 3.8 |

VDC |

VEE |

Power Supply (Referenced to GND, VCC = +3.3V) |

|

±6.0 to 0 |

VDC |

VI |

Input Voltage (VI not more positive than GND) |

|

0 to 3.8 |

VDC |

Iout |

Output Current |

Continuous |

50 |

mA |

|

|

Surge |

100 |

|

|

|

|

|

|

IBB |

VBB Sink/Source Current{ |

|

± 0.5 |

mA |

TA |

Operating Temperature Range |

|

±40 to +85 |

°C |

Tstg |

Storage Temperature |

|

±65 to +150 |

°C |

θJA |

Thermal Resistance (Junction±to±Ambient) |

Still Air |

190 |

°C/W |

|

|

500lfpm |

130 |

|

|

|

|

|

|

θJC |

Thermal Resistance (Junction±to±Case) |

|

41 to 44 ± 5% |

°C/W |

Tsol |

Solder Temperature (<2 to 3 Seconds: 245°C desired) |

265 |

°C |

|

* Maximum Ratings are those values beyond which damage to the device may occur.

{ Use for inputs of same package only.

DC CHARACTERISTICS, ECL/LVECL (VCC = +3.3V; VEE = ±5.5V to ±3.0V, GND = 0V)

|

|

|

|

|

±40°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

|

|

Min |

Typ |

Max |

Min |

Typ |

Max |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IEE |

Power Supply Current |

|

|

8.0 |

16 |

25 |

8.0 |

16 |

25 |

8.0 |

16 |

25 |

mA |

|

(Note 1.) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIH |

Input HIGH Voltage Single Ended |

±1165 |

|

±880 |

±1165 |

|

±880 |

±1165 |

|

±880 |

mV |

||

|

(Note 4.) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIL |

Input LOW Voltage Single Ended |

±1810 |

|

±1625 |

±1810 |

|

±1625 |

±1810 |

|

±1625 |

mV |

||

|

(Note 4.) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VBB |

Output Voltage Reference |

|

|

±1550 |

±1450 |

±1350 |

±1550 |

±1450 |

±1350 |

±1550 |

±1450 |

±1350 |

mV |

VIHCMR |

Input HIGH Voltage Common Mode |

VEE+2.0 |

0.0 |

VEE+2.0 |

0.0 |

VEE+2.0 |

0.0 |

V |

|||||

|

Range (Note 3.) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IIH |

Input HIGH Current |

|

|

|

|

150 |

|

|

150 |

|

|

150 |

μA |

IIL |

Input LOW Current |

D |

0.5 |

|

|

0.5 |

|

|

0.5 |

|

|

μA |

|

|

|

D |

|

±150 |

|

|

±150 |

|

|

±150 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTE: 100EP circuits are designed to meet the DC specifications shown in the above table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500lfpm is maintained.

1.(VCC = +3.3V, GND = 0V, VEE = ±3.3V), all other pins floating.

2.All loading with 500 ohms to GND, CL = 20pF.

3.VIHCMR min varies 1:1 with VEE, max varies 1:1 with VCC.

4.Input and output parameters vary 1:1 with VCC.

http://onsemi.com

2

MC100EPT25

TTL OUTPUT DC CHARACTERISTICS (VCC = 3.3V ± 0.3V; GND = 0V; VEE = ±3.3V ± 0.3V; TA = ±40°C to 85°C)

Symbol |

Characteristic |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

ICCH |

Power Supply Current (Outputs set to HIGH) |

6.0 |

10 |

14 |

mA |

ICCL |

Power Supply Current (Outputs set to LOW) |

7.0 |

12 |

17 |

mA |

VOH |

Output HIGH Voltage (IOH = ±3.0mA) (Note 5.) |

2.2 |

|

|

V |

VOL |

Output LOW Voltage (IOL = 24mA) (Note 5.) |

|

|

0.5 |

V |

IOS |

Output Short Circuit Current |

±130 |

|

±60 |

mA |

NOTE: 100EP circuits are designed to meet the DC specifications shown in the above table after thermal equilibrium has been established. The circuit is in a test socket or mounted on a printed circuit board and transverse airflow greater than 500lfpm is maintained.

5. All loading with 500 ohms to GND, CL = 20pF.

AC CHARACTERISTICS (VCC = 3.3V ± 0.3V; GND = 0V)

|

|

|

|

|

|

±40°C |

|

|

25°C |

|

|

85°C |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Symbol |

Characteristic |

|

|

|

Min |

Typ |

Max |

Min |

Typ |

Max |

Min |

Typ |

Max |

Unit |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

fmax |

Maximum Toggle Frequency |

|

|

|

275 |

|

|

275 |

|

|

275 |

|

|

MHz |

tPLH, |

Propagation Delay to |

|

|

|

800 |

1200 |

1800 |

800 |

1100 |

1600 |

800 |

1100 |

1600 |

ns |

tPHL |

Output Differential |

|

|

|

|

|

|

|

|

|

|

|

|

|

tSK+ + |

Output±to±Output Skew++ |

|

|

|

|

60 |

|

|

60 |

|

|

60 |

|

ps |

tSK± ± |

Output±to±Output Skew± ± |

|

|

|

|

25 |

|

|

25 |

|

|

25 |

|

|

tSKPP |

Part±to±Part Skew (Note 6.) |

|

|

|

|

500 |

|

|

500 |

|

|

500 |

|

|

tJITTER |

Cycle±to±Cycle Jitter |

|

|

|

|

TBD |

|

|

TBD |

|

|

TBD |

|

ps |

VPP |

Input Voltage Swing |

|

|

|

100 |

800 |

1200 |

100 |

800 |

1200 |

100 |

800 |

1200 |

mV |

|

(Differential) (Note 7.) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tr |

Output Rise/Fall Times |

Q, |

|

|

450 |

600 |

750 |

450 |

600 |

750 |

450 |

600 |

750 |

ps |

Q |

||||||||||||||

tf |

(0.8V ± 2.0V) |

|

|

|

900 |

1160 |

1400 |

900 |

1100 |

1400 |

900 |

1100 |

1400 |

|

6.Skews are measured between outputs under identical conditions.

7.200mV input guarantees full logic swing at the output.

http://onsemi.com

3

Loading...

Loading...