Texas Instruments TPS2101DR, TPS2101DBVT, TPS2101DBVR, TPS2100DR, TPS2101D Datasheet

...

TPS2100, TPS2101

VAUX POWER-DISTRIBUTION SWITCHES

SLVS197C ± JUNE 1999 ± REVISED APRIL 2000

features

DDual-Input, Single-Output MOSFET Switch With No Reverse Current Flow (No Parasitic Diodes)

DIN1 . . . 250-mΩ, 500-mA N-Channel; 16-µA Max Supply Current

DIN2 . . . 1.3-Ω, 10-mA P-Channel;

1.5-µA Max Supply Current (VAUX Mode)

DAdvanced Switch Control Logic

DCMOSand TTL-Compatible Enable Input

DControlled Rise, Fall, and Transition Times

D2.7-V to 4 V Operating Range

DSOT-23-5 and SOIC-8 Package

D±40°C to 70°C Ambient Temperature Range

D2-kV Human-Body-Model, 750-V CDM, 200-V Machine-Model ElectrostaticDischarge Protection

typical applications

DNotebook and Desktop PCs

DPalmtops and PDAs

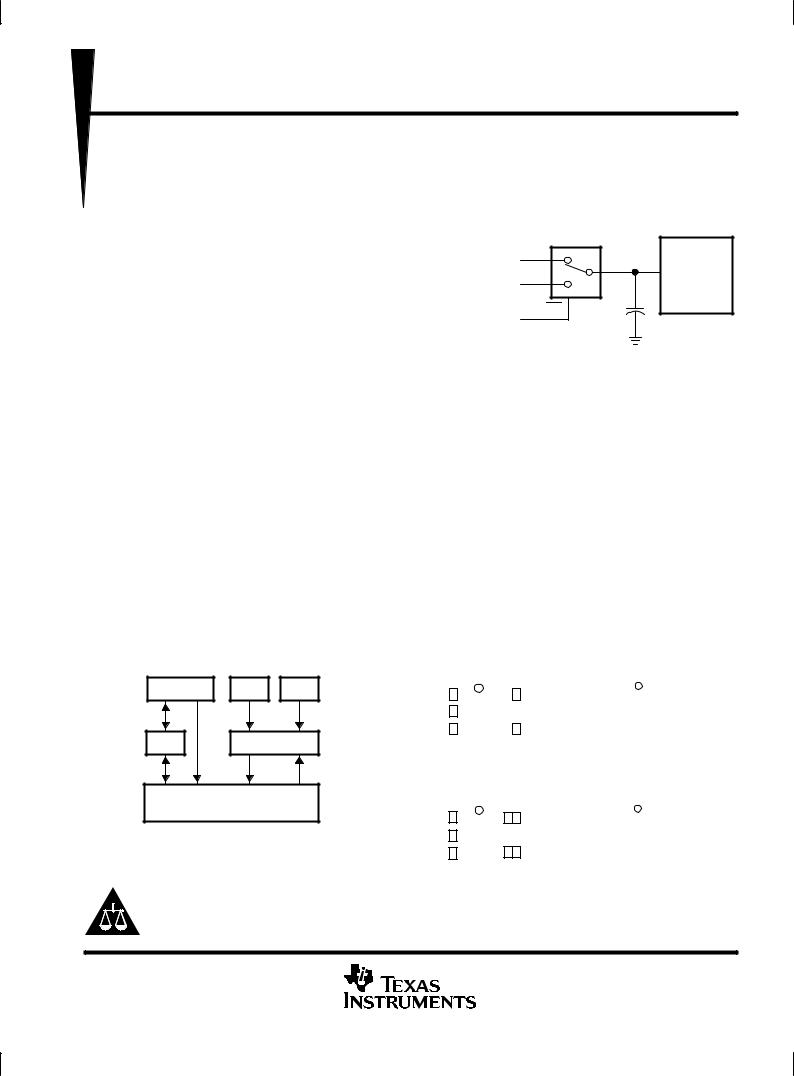

3.3V VCC

3.3V VAUX

D3 or PME Status Control Signal

TPS2100 |

Controller |

IN1 |

|

3.3 V |

(CardBus, |

IN2 |

1394, |

|

PCI, |

EN |

et al.) |

|

|

Hold-Up |

|

Capacitor |

|

Figure 1. Typical Dual-Input Single-Output

Application

description

The TPS2100 and TPS2101 are dual-input, single-output power switches designed to provide uninterrupted output voltage when transitioning between two independent power supplies. Both devices combine one n-channel (250 mΩ) and one p-channel (1.3 Ω) MOSFET with a single output. The p-channel MOSFET (IN2) is used with auxiliary power supplies that deliver lower current for standby modes. The n-channel MOSFET (IN1) is used with a main power supply that delivers higher current required for normal operation. Low on-resistance makes the n-channel the ideal path for higher main supply current when power-supply regulation and system voltage drops are critical. When using the p-channel MOSFET, quiescent current is reduced to 0.75 µA to decrease the demand on the standby power supply. The MOSFETs in the TPS2100 and TPS2101 do not have the parasitic diodes, found in discrete MOSFETs, which allow the devices to prevent back-flow current when the switch is off.

|

TPS2100 |

|

DBV PACKAGE |

D PACKAGE |

|

(TOP VIEW) |

||

(TOP VIEW) |

||

|

PCI Bus |

VAUX |

3.3 V |

|

VGA |

|

TPS210x |

|

|

VCC |

D3-STAT |

|

|

|

||

PCI12xx / PCI14xx |

|

||

CardBus Controller |

|

||

Figure 2. VAUX CardBus Implementation

|

|

|

|

|

|

|

|

|

IN1 |

IN2 |

|

|

1 |

8 |

|

|

OUT |

|||

|

EN |

|

|

|

1 |

5 |

|

|

|

|

|

|

||||||||

|

|

|

|

GND |

|

|

2 |

7 |

|

|

OUT |

|||||||||

GND |

|

|

2 |

|

|

|

|

|

|

|

|

|||||||||

IN2 |

|

|

3 |

4 |

|

|

OUT |

|

EN |

|

|

|

|

3 |

6 |

|

|

NC |

||

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

NC |

|

|

4 |

5 |

|

|

IN1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

TPS2101 |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

DBV PACKAGE |

|

|

|

|

|

|

D PACKAGE |

|

|||||||||

|

|

|

|

(TOP VIEW) |

|

|

|

|

|

|

|

(TOP VIEW) |

|

|||||||

|

|

|

|

|

|

|

|

|

|

IN2 |

|

|

|

|

|

|

|

OUT |

||

EN |

|

|

1 |

5 |

|

|

IN1 |

|

|

|

1 |

8 |

|

|

||||||

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|||||||||||||||||

|

|

|

|

GND |

|

|

|

2 |

7 |

|

|

OUT |

||||||||

GND |

|

|

2 |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

EN |

|

|

|

3 |

6 |

|

|

NC |

||||||

IN2 |

|

|

3 |

4 |

|

|

OUT |

|

|

|

|

|

||||||||

|

|

|

|

NC |

|

|

|

4 |

5 |

|

|

IN1 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

NC ± No internal connection |

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 2000, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

TPS2100, TPS2101

VAUX POWER-DISTRIBUTION SWITCHES

SLVS197C ± JUNE 1999 ± REVISED APRIL 2000

AVAILABLE OPTIONS

|

|

|

|

|

PACKAGED DEVICES |

||

TJ |

DEVICE |

ENABLE |

|

|

|||

SOT-23-5 |

SOIC-8 |

||||||

|

|

|

|

|

(DBV)² |

(D) |

|

|

TPS2100 |

|

|

|

TSP2100DBV² |

TPS2100D |

|

±40°C to 85°C |

|

EN |

|

||||

TPS2101 |

EN |

TPS2101DBV² |

TPS2101D |

||||

|

|||||||

Both packages are available left-end taped and reeled. Add an R suffix to the D device type (e.g., TPS2101DR).

²Add T (e.g., TPS2100DBVT) to indicate tape and reel at order quantity of 250 parts. Add R (e.g., TPS2100DBVR) to indicate tape and reel at order quantity of 3000 parts.

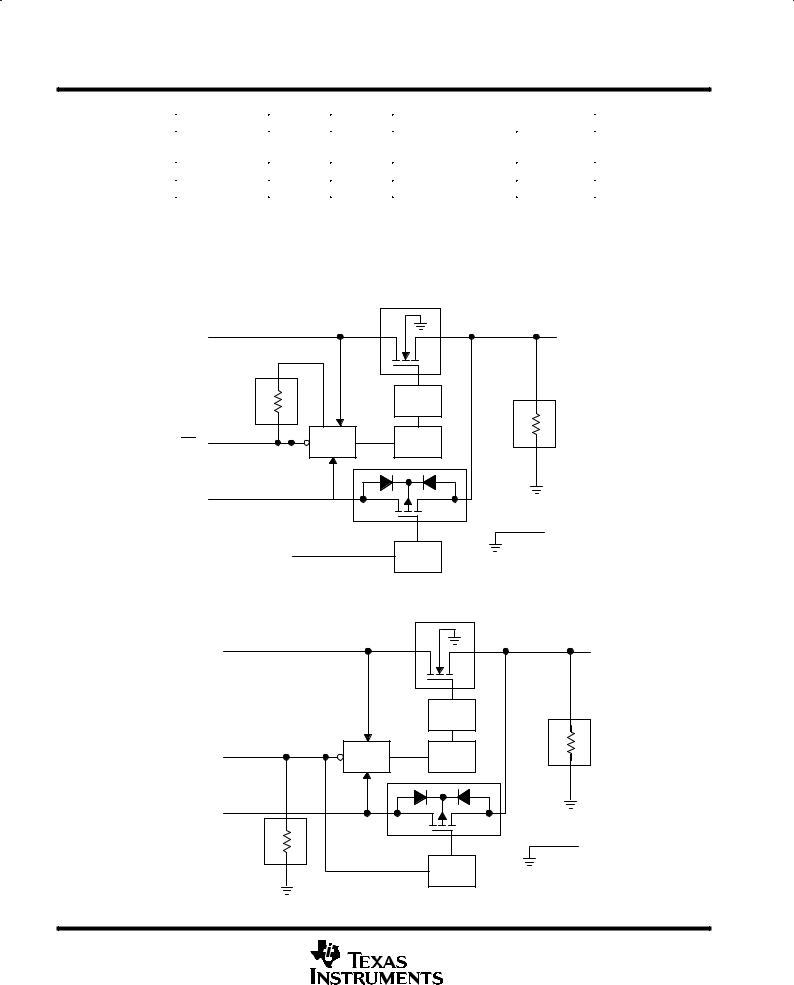

TPS2100 functional block diagram

|

|

SW1 |

|

IN1 |

|

250 mΩ |

|

|

OUT |

||

Pullup |

|

Charge |

|

|

Pump |

||

Circuit |

|

||

|

Discharge |

||

|

VCC |

Circuit |

|

EN |

Driver |

||

Select |

|||

|

|

IN2  SW2

SW2

1.3 Ω

GND

Driver

TPS2101 functional block diagram

|

|

SW1 |

IN1 |

|

250 mΩ |

|

OUT |

|

|

|

Charge |

|

|

Pump |

|

|

Discharge |

EN |

VCC |

Circuit |

Select |

Driver |

|

|

|

IN2

SW2

1.3 Ω

Pulldown

GND

Circuit

Driver

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TPS2100, TPS2101

VAUX POWER-DISTRIBUTION SWITCHES

SLVS197C ± JUNE 1999 ± REVISED APRIL 2000

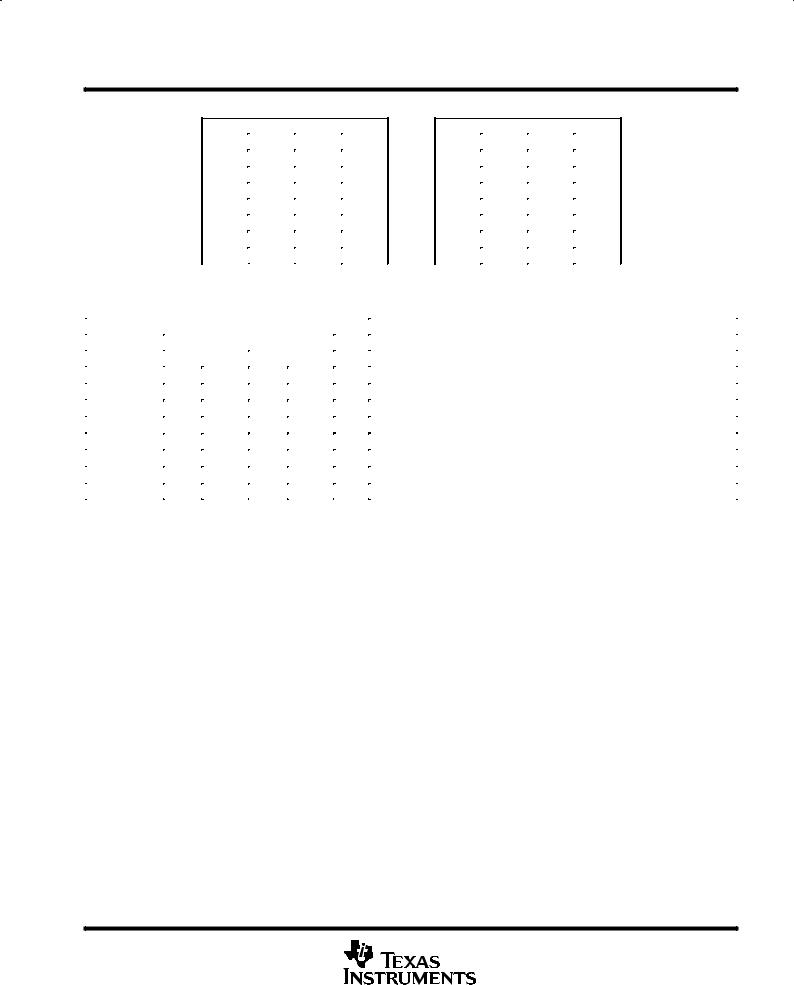

Function Tables

TPS2100

VIN1 |

VIN2 |

EN |

OUT |

0 V |

0 V |

XX |

GND |

|

|

|

|

0 V |

3.3 V |

L |

GND |

|

|

|

|

3.3 V |

3.3 V |

L |

VIN1 |

3.3 V |

0 V |

L |

VIN1 |

|

|

|

|

0 V |

3.3 V |

H |

VIN2 |

|

|

|

|

3.3 V |

0 V |

H |

VIN2 |

|

|

|

|

3.3 V |

3.3 V |

H |

VIN2 |

|

|

|

|

XX = don't care

TPS2101

VIN1 |

VIN2 |

EN |

OUT |

|

|

|

|

0 V |

0 V |

XX |

GND |

|

|

|

|

0 V |

3.3 V |

H |

GND |

|

|

|

|

3.3 V |

3.3 V |

H |

VIN1 |

3.3 V |

0 V |

H |

VIN1 |

|

|

|

|

0 V |

3.3 V |

L |

VIN2 |

|

|

|

|

3.3 V |

0 V |

L |

VIN2 |

|

|

|

|

3.3 V |

3.3 V |

L |

VIN2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Terminal Functions |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TERMINAL |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NO. |

|

|

DESCRIPTION |

|

NAME |

|

|

|

|

|

|

I/O |

|||

TPS2100 |

|

TPS2101 |

||||||||

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DBV |

|

D |

|

DBV |

D |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|

|

|

|

1 |

3 |

|

Active-high enable for IN1-OUT switch |

|

|

|

|

|

|

|

|

|

|

|

|

|

EN |

|

1 |

|

3 |

|

|

|

I |

Active-low enable for IN1-OUT switch |

GND |

2 |

|

2 |

|

2 |

2 |

I |

Ground |

||

|

|

|

|

|

|

|

|

|

||

IN1 |

5 |

|

5 |

|

5 |

5 |

I |

Main Input voltage, NMOS drain (250 mΩ) |

||

|

|

|

|

|

|

|

|

|

||

IN2 |

3 |

|

1 |

|

3 |

1 |

I |

Auxilliary input voltage, PMOS drain (1.3 Ω) |

||

OUT |

4 |

|

7, 8 |

|

4 |

7, 8 |

O |

Power switch output |

||

|

|

|

|

|

|

|

|

|

||

NC |

|

|

4, 6 |

|

|

4, 6 |

|

No connection |

||

detailed description

power switches n-channel MOSFET

The IN1-OUT n-channel MOSFET power switch has a typical on-resistance of 250 mΩ at 3.3-V input voltage, and is configured as a high-side switch.

p-channel MOSFET

The IN2-OUT p-channel MOSFET power switch with typical on-resistance of 1.3 Ω at 3.3-V input voltage and is configured as a high-side switch. When operating, the p-channel MOSFET quiescent current is reduced to less than 1.5 µA.

charge pump

An internal charge pump supplies power to the driver circuit and provides the necessary voltage to pull the gate of the MOSFET above the source. The charge pump operates from input voltages as low as 2.7 V and requires very little supply current.

driver

The driver controls the gate voltage of the IN1-OUT and IN2-OUT power switches. To limit large current surges and reduce the associated electromagnetic interference (EMI) produced, the drivers incorporate circuitry that controls the rise times and fall times of the output voltage.

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

TPS2100, TPS2101

VAUX POWER-DISTRIBUTION SWITCHES

SLVS197C ± JUNE 1999 ± REVISED APRIL 2000

detailed description (continued)

enable

The logic enable will turn on the IN2-OUT power switch when a logic high is present on EN (TPS2100) or logic low is present on EN (TPS2101). A logic low input on EN (TPS2100) or logic high on EN (TPS2101) restores bias to the drive and control circuits and turns on the IN1-OUT power switch. The enable input is compatible with both TTL and CMOS logic levels.

the VAUX application for CardBus controllers

The PC Card specification requires the support of VAUX to the CardBus controller as well as to the PC Card sockets. Both are 3.3-V requirements; however the CardBus controller's current demand from the VAUX supply is limited to 10 A, whereas the PC Card may consume as much as 200 mA. In either implementation, if support of a wake-up event is required, the controller and the socket will transition from the 3.3-V VCC rail to the 3.3-V VAUX rail when the equipment moves into a low power mode such as D3. The transition from VCC to VAUX needs to be seamless in order to maintain all memory and register information in the system. If VAUX is not supported, the system will lose all register information when it transitions to the D3 state.

absolute maximum ratings over operating free-air temperature (unless otherwise noted)²

Input voltage range, VI(IN1) (see Note1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . ±0.3 V to 5 V |

|

Input voltage range, VI(IN2) (see Note1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . ±0.3 V to 5 |

V |

Input voltage range, VI at EN or EN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . ±0.3 V to 5 |

V |

Output voltage range, VO (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . ±0.3 V to 5 |

V |

Continuous output current, IO(IN1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . 700 mA |

|

Continuous output current, IO(IN2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . 70 mA |

|

Continuous total power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

See dissipation rating table |

|

Operating virtual junction temperature range, TJ . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . ±40°C to 85°C |

|

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . ±65°C to 150°C |

|

Lead temperature soldering 1,6 mm (1/16 inch) from case for 10 seconds . . . . . . |

. . . . . . . . . . . . . . . . . 260°C |

|

Electrostatic discharge (ESD) protection: Human body model . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . . 2 kV |

|

Machine model . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . . . . . . 200 V |

|

Charged device model (CDM) . . . . . . . |

. . . . . . . . . . . . . . . . . . 750 |

V |

² Stresses beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltages are with respect to GND.

|

|

DISSIPATION RATING TABLE |

|

||

PACKAGE |

TA < 25°C |

|

DERATING FACTOR |

TA = 70°C |

TA = 85°C |

POWER RATING |

|

ABOVE TA = 25°C |

POWER RATING |

POWER RATING |

|

|

|

||||

DBV |

309 mW |

|

3.1 mW/°C |

170 mW |

123 mW |

|

|

|

|

|

|

D |

568 mW |

|

5.7 mW/°C |

313 mW |

227 mW |

recommended operating conditions

|

|

|

MIN |

MAX |

UNIT |

|

|

|

|

|

|

Input voltage, VI(INx) |

2.7 |

4 |

V |

||

Input voltage, VI at |

|

and EN |

0 |

4 |

V |

EN |

|||||

Continuous output current, IO(IN1) |

|

500 |

mA |

||

Continuous output current, IO(IN2) |

|

100³ |

mA |

||

Operating virtual junction temperature, TJ |

± 40 |

85 |

°C |

||

³The device can deliver up to 220 mA at IO(IN2). However, operation at the higher current levels will result in greater voltage drop across the device, and greater voltage droop when switching between IN1 and IN2.

4 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TPS2100, TPS2101

VAUX POWER-DISTRIBUTION SWITCHES

SLVS197C ± JUNE 1999 ± REVISED APRIL 2000

electrical characteristics over recommended operating junction temperature range, VI(IN1) = V(IN2) = 3.3 V, IO = rated current (unless otherwise noted)

power switch

|

PARAMETER |

|

TEST |

MIN TYP |

MAX |

UNIT |

|

|

|

CONDITIONS² |

|||||

|

|

|

|

|

|

||

|

|

IN1-OUT |

TJ = 25°C |

250 |

|

mΩ |

|

rDS(on) |

On-state resistance |

TJ = 85°C |

300 |

375 |

|||

|

|

||||||

IN2-OUT |

TJ = 25°C |

1.3 |

|

Ω |

|||

|

|

|

|||||

|

|

TJ = 85°C |

1.5 |

2.1 |

|||

|

|

|

|

² Pulse-testing techniques maintain junction temperature close to ambient termperature; thermal effects must be taken into account separately.

enable input (EN and EN)

|

PARAMETER |

TEST CONDITIONS |

MIN |

TYP MAX |

UNIT |

||||||

|

|

|

|

|

|

|

|

|

|

|

|

VIH |

High-level input voltage |

2.7 V ≤ VI(INx) ≤ 4 V |

2 |

|

V |

||||||

VIL |

Low-level input voltage |

2.7 V ≤ VI(INx) ≤ 4 V |

|

0.8 |

V |

||||||

II |

Input current |

TPS2100 |

|

EN |

= 0 V or |

EN |

= VI(INx) |

±0.5 |

0.5 |

A |

|

TPS2101 |

EN = 0 V or EN = VI(INx) |

±0.5 |

0.5 |

A |

|||||||

|

|

||||||||||

supply current

|

PARAMETER |

|

|

|

TEST CONDITIONS |

|

|

|

MIN |

TYP MAX |

UNIT |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

= H, |

TJ = 25°C |

|

|

|

0.75 |

|

|

|

|

|

EN |

|

|

|

|

A |

||||||

|

|

TPS2100 |

IN2 selected |

±40°C ≤ TJ ≤ |

85°C |

|

|

1.5 |

|||||

|

|

|

|

|

|||||||||

|

|

|

|

= L, |

TJ = 25°C |

|

|

|

10 |

|

|

||

|

|

|

|

EN |

|

|

|

|

A |

||||

II |

Supply current |

|

IN1 selected |

±40°C ≤ TJ ≤ |

85°C |

|

|

16 |

|||||

|

|

|

|

||||||||||

|

EN = L, |

TJ = 25°C |

|

|

|

0.75 |

|

A |

|||||

|

|

|

|

|

|

|

|||||||

|

|

|

IN2 selected |

° ≤ |

TJ |

≤ |

° |

|

|

1.5 |

|||

|

|

|

|

|

|

||||||||

|

|

TPS2101 |

|

|

|

±40 C |

|

85 C |

|

|

|

||

|

|

EN = H, |

TJ = 25°C |

|

|

|

10 |

|

A |

||||

|

|

|

|

|

|

|

|||||||

|

|

|

IN1 selected |

° ≤ |

TJ |

≤ |

° |

|

|

16 |

|||

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

±40 C |

|

85 C |

|

|

|

||

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

5 |

TPS2100, TPS2101

VAUX POWER-DISTRIBUTION SWITCHES

SLVS197C ± JUNE 1999 ± REVISED APRIL 2000

switching characteristics, TJ = 25°C, VI(IN1) = VI(IN2) = 3.3 V (unless otherwise noted)²

|

PARAMETER |

TEST CONDITIONS² |

MIN TYP MAX |

UNIT |

||||

|

|

|

|

CL = 1 F, |

IL = 500 mA |

830 |

|

|

|

|

IN1-OUT |

VI(IN2) = 0 |

CL = 10 F, |

IL = 500 mA |

840 |

|

|

tr |

Output rise time |

|

|

CL = 1 F, |

IL = 10 mA |

640 |

s |

|

|

|

CL = 1 F, |

IL = 10 mA |

5.5 |

||||

|

|

|

|

|

||||

|

|

IN2-OUT |

VI(IN1) = 0 |

CL = 10 F, |

IL = 10 mA |

70 |

|

|

|

|

|

|

CL = 1 F, |

IL = 1 mA |

5.5 |

|

|

|

|

|

|

CL = 1 F, |

IL = 500 mA |

8 |

|

|

|

|

IN1-OUT |

VI(IN2) = 0 |

CL = 10 F, |

IL = 500 mA |

93 |

|

|

tf |

Output fall time |

|

|

CL = 1 F, |

IL = 10 mA |

23 |

s |

|

|

|

CL = 1 F, |

IL = 10 mA |

690 |

||||

|

|

|

|

|

||||

|

|

IN2-OUT |

VI(IN1) = 0 |

CL = 10 F, |

IL = 10 mA |

6900 |

|

|

|

|

|

|

CL = 1 F, |

IL = 1 mA |

6900 |

|

|

tPLH |

Propagation delay time, low-to-high output |

IN1-OUT |

VI(IN2) = 0 |

CL = 10 F, |

IL = 10 mA |

75 |

s |

|

IN2-OUT |

VI(IN1) = 0 |

2 |

||||||

|

|

|

|

|

||||

tPHL |

Propagation delay time, high-to-low output |

IN1-OUT |

VI(IN2) = 0 |

CL = 10 F, |

IL = 10 mA |

3 |

s |

|

IN2-OUT |

VI(IN1) = 0 |

370 |

||||||

|

|

|

|

|

||||

² All timing parameters refer to Figure 3.

6 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

Loading...

Loading...