Texas instruments TMS320F28062, TMS320F28068, TMS320F28067, TMS320F28069, TMS320F28064 ADVANCE INFORMATION

...

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com |

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

Piccolo Microcontrollers

Check for

Samples: TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066, TMS320F28065, TMS320F28064, TMS320F28063,

TMS320F28062

1 TMS320F2806x ( Piccolo™ ) MCUs

1.1Features

•High-Efficiency 32-Bit CPU (TMS320C28x™ )

–80 MHz (12.5-ns Cycle Time)

–16 x 16 and 32 x 32 MAC Operations

–16 x 16 Dual MAC

–Harvard Bus Architecture

–Atomic Operations

–Fast Interrupt Response and Processing

–Unified Memory Programming Model

–Code-Efficient (in C/C++ and Assembly)

•Floating-Point Unit

–Native Single-Precision Floating-Point Operations

•Programmable Control Law Accelerator (CLA)

–32-Bit Floating-Point Math Accelerator

–Executes Code Independently of the Main CPU

•Viterbi, Complex Math, CRC Unit (VCU)

–Extends C28x™ Instruction Set to Support Complex Multiply, Viterbi Operations, and Cyclic Redundency Check (CRC)

•Embedded Memory

–Up to 256KB Flash

–Up to 100KB RAM

–2KB OTP ROM

•6-Channel DMA

•Low Device and System Cost

–Single 3.3-V Supply

–No Power Sequencing Requirement

–Integrated Power-on Reset and Brown-out Reset

–Low-Power Operating Modes

–No Analog Support Pin

•Clocking

–Two Internal Zero-pin Oscillators

–On-Chip Crystal Oscillator/External Clock Input

–Dynamic PLL Ratio Changes Supported

–Watchdog Timer Module

–Missing Clock Detection Circuitry

•Peripheral Interrupt Expansion (PIE) Block That Supports All Peripheral Interrupts

•Three 32-Bit CPU Timers

•Advanced Control Peripherals

•Up to 8 Enhanced Pulse Width Modulator (ePWM) Modules

–16 PWM Channels Total (8 HRPWM-Capable)

–Independent 16-Bit Timer in Each Module

•3 Input Capture (eCAP) Modules

•4 High-Resolution Input Capture (HRCAP) Modules

•2 Quadrature Encoder (eQEP) Modules

•12-Bit ADC, Dual Sample-and-Hold

–Up to 3 MSPS

–Up to 16 Channels

•On-Chip Temperature Sensor

•128-Bit Security Key/Lock

–Protects Secure Memory Blocks

–Prevents Firmware Reverse Engineering

•Serial Port Peripherals

–Up to Two Serial Communications Interface (SCI) [UART] Modules

–Two Serial Peripheral Interface (SPI) Modules

–One Inter-Integrated-Circuit (I2C) Bus

–One Multi-Channel Buffered Serial Port (McBSP) Bus

–One Enhanced Controller Area Network (eCAN)

•Up to 54 Individually Programmable, Multiplexed GPIO Pins With Input Filtering

•Advanced Emulation Features

–Analysis and Breakpoint Functions

–Real-Time Debug via Hardware

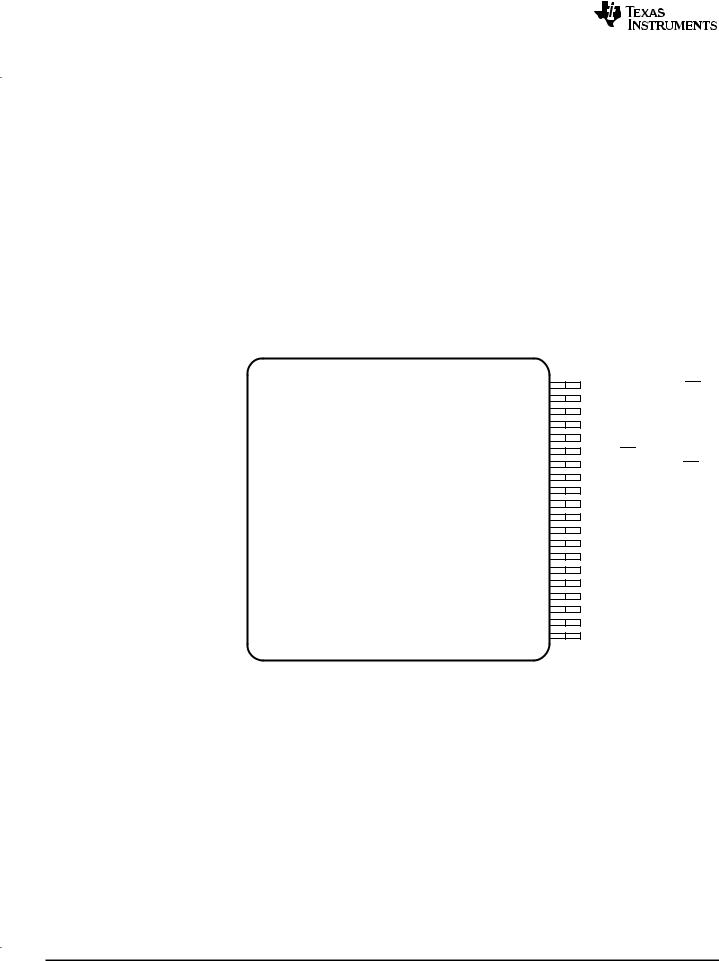

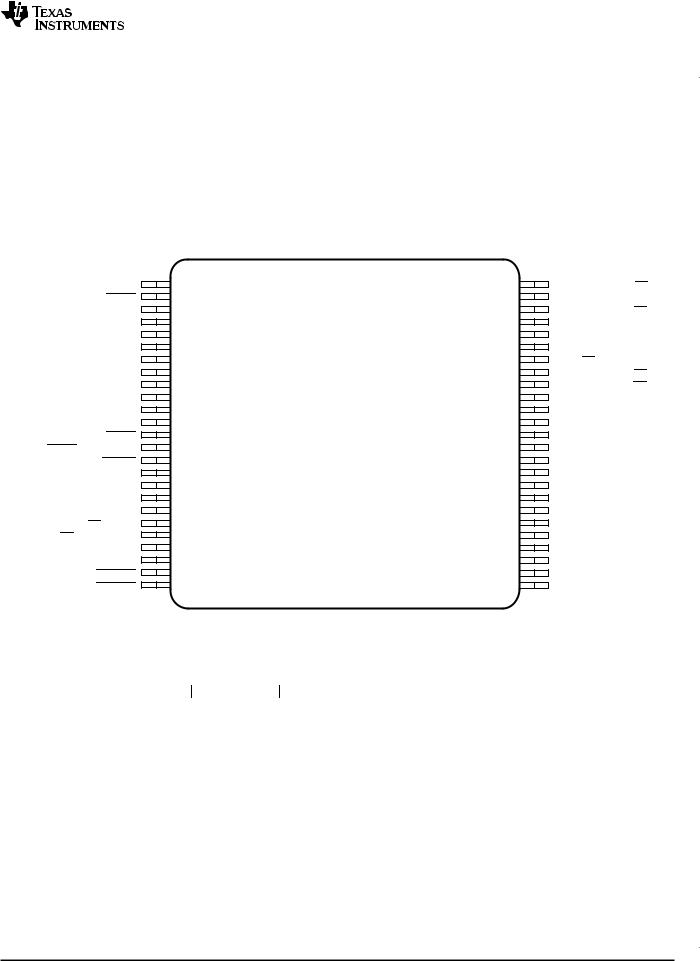

•2806x Packages

–80-Pin PFP and 100-Pin PZP PowerPAD™ Low-Profile Quad Flatpacks (LQFPs)

–80-Pin PN and 100-Pin PZ LQFPs

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Piccolo, PowerPAD, C28x, TMS320C2000, C2000, Code Composer Studio, XDS510, XDS560, TMS320C28x, TMS320C54x, TMS320C55x are trademarks of Texas Instruments.

All other trademarks are the property of their respective owners.

ADVANCE INFORMATION concerns new products in the sampling |

Copyright © 2010–2011, Texas Instruments Incorporated |

or preproduction phase of development. Characteristic data and other |

|

specifications are subject to change without notice. |

|

ADVANCEINFORMATION

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

www.ti.com |

1.2Description

The F2806x Piccolo™ family of microcontrollers provides the power of the C28x™ core and Control Law Accelerator (CLA) coupled with highly integrated control peripherals in low pin-count devices. This family is code-compatible with previous C28x-based code, as well as providing a high level of analog integration.

An internal voltage regulator allows for single-rail operation. Enhancements have been made to the HRPWM module to allow for dual-edge control (frequency modulation). Analog comparators with internal 10-bit references have been added and can be routed directly to control the PWM outputs. The ADC

converts from 0 to 3.3-V fixed full scale range and supports ratio-metric VREFHI/VREFLO references. The ADC interface has been optimized for low overhead/latency.

INFORMATIONADVANCE

2 |

TMS320F2806x ( Piccolo™ ) MCUs |

Copyright © 2010–2011, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com |

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

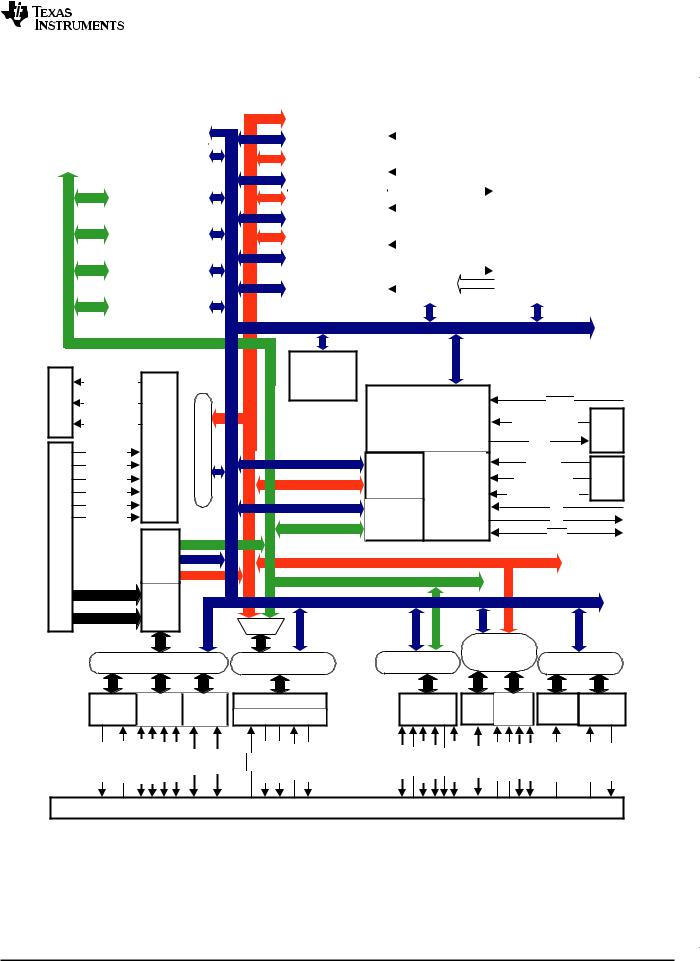

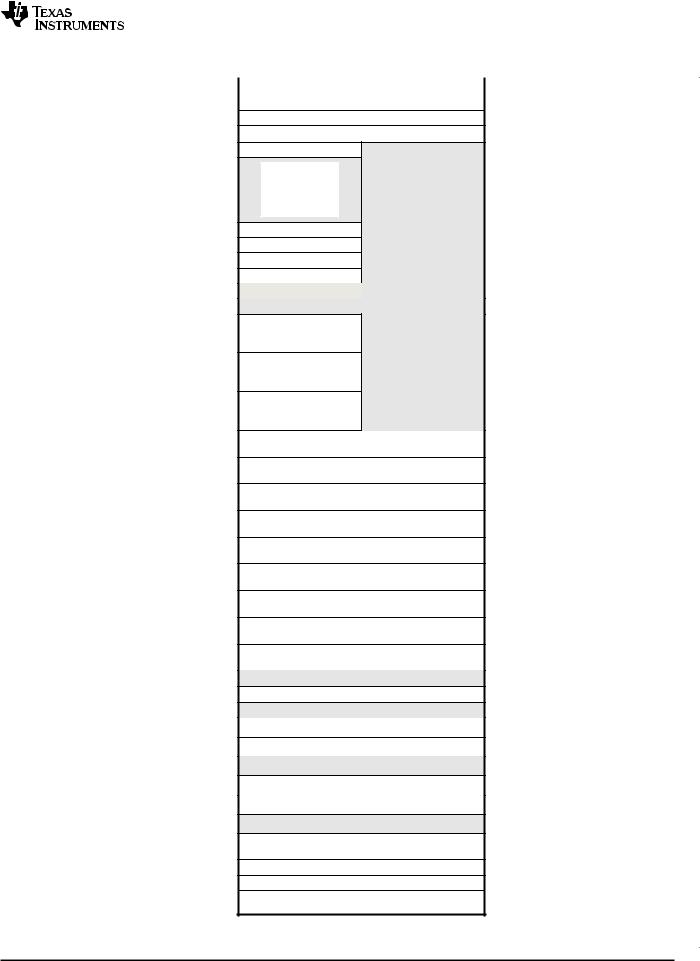

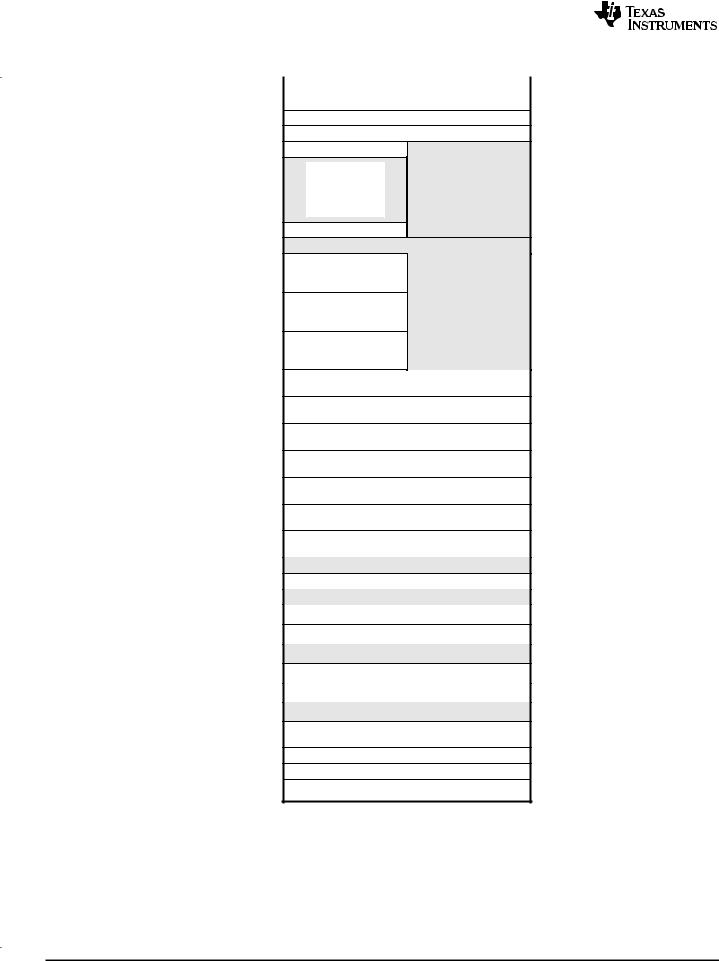

1.3Functional Block Diagram

|

|

M0 SARAM (1Kx16) |

|

|

(0-wait, Non-Secure) |

|

|

|

|

|

M1 SARAM (1Kx16) |

|

|

(0-wait, Non-Secure) |

|

|

|

|

|

|

|

|

L5 DPSARAM (8Kx16) |

|

|

(0-wait, Non-Secure) |

|

|

DMA RAM0 |

|

|

|

|

|

L6 DPSARAM (8Kx16) |

Bus |

|

(0-wait, Non-Secure) |

|

DMA RAM1 |

|

|

|

|

DMA |

|

L7 DPSARAM (8Kx16) |

|

(0-wait, Non-Secure) |

|

|

|

DMA RAM2 |

|

|

L8 DPSARAM (8Kx16) |

|

|

(0-wait, Non-Secure) |

|

|

DMA RAM3 |

|

|

|

|

DMA Bus |

|

Mux |

COMP1OUT |

|

|

GPIO |

COMP2OUT |

COMP3OUT |

|

COMP1A |

|

COMP1B |

|

COMP2A |

|

COMP2B |

|

COMP3A |

AIOMux |

COMP3B |

|

COMP  BusPeripheral

BusPeripheral

+

DAC bit-32

ADC 0-wait Result Regs

A7:0

ADC

B7:0

16-bit Peripheral Bus

L0 DPSARAM (2Kx16) |

|

|

|

|

|

|

|

|

|

|

|

OTP 1Kx16 |

|

(0-wait, Secure) |

|

|

|

|

|

|

|

|

|

|

|

Secure |

|

CLA Data RAM2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

L1 DPSARAM (1Kx16) |

|

|

|

|

|

|

(0-wait, Secure) |

|

|

|

|

|

FLASH |

|

|

|

|

|

||

CLA Data RAM0 |

|

|

|

|

|

|

|

|

|

|

|

64K/128Kx16 |

|

|

|

|

|

|

|

|

L2 DPSARAM (1Kx16) |

|

|

Code |

|

|

8 equal sectors |

(0-wait, Secure) |

|

|

Security |

|

|

Secure |

|

|

|

|

|||

CLA Data RAM1 |

|

|

Module |

|

|

|

L3 DPSARAM (4Kx16) |

|

|

(CSM) |

|

|

|

|

|

|

|

|

|

|

(0-wait, Secure) |

|

|

|

|

|

PUMP |

|

|

|

|

|

||

CLA Program RAM |

|

|

|

|

|

|

|

|

|

|

|

|

OTP/Flash |

|

|

|

|

|

|

|

L4 SARAM (8Kx16) |

|

|

|

PSWD |

Wrapper |

|

(0-wait, Secure) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Memory Bus |

|

|

|

Bus |

|

|

|

|

|

|

Memory |

BusCLA |

BusDMA |

Boot-ROM |

|

|

GPIO Mux |

(32Kx16) |

|

|

||||

|

|

|

|

|

|

|

|

|

|

(0-wait, |

|

|

|

|

|

|

Non-Secure) |

|

|

|

|

|

|

C28x 32-bit CPU |

TRST |

|

|

|

|

|

|

|

||

|

|

|

|

FPU |

TCK, TDI, TMS |

|

|

|

|

VCU |

|

||

|

|

|

|

|

||

|

|

|

|

|

TDO |

|

|

|

|

CLA + |

|

XCLKIN |

GPIO Mux |

|

|

|

Message |

OSC1, OSC2, |

LPM Wakeup |

|

|

|

|

RAMs |

Ext, PLLs, |

3 Ext. Interrupts |

|

|

|

|

|

LPM, WD, |

|

|

|

|

|

DMA |

CPU Timers |

X1 |

|

|

|

|

0/1/2. PIE |

X2 |

|

|

|

|

|

6-ch |

|

||

|

|

|

|

|

||

|

|

|

|

XRS |

|

|

|

|

|

|

|

|

|

CLA Bus

DMA Bus

Memory Bus

|

|

32-bit |

32-bit Peripheral Bus |

32-bit Peripheral |

Peripheral Bus |

(CLA accessible) 32-bit Peripheral |

||

(CLA accessible) |

Bus |

Bus |

SCI-A/B |

SPI-A/B |

I2C-A |

ePWM1 to ePWM8 |

McBSP-A |

|

eCAP- |

eQEP- |

HRCAP- |

eCAN-A |

|||

(4L FIFO) |

(4L FIFO) (4L FIFO) |

HRPWM (8ch) |

|

1/2/3 |

1/2 |

1/2/3/4 |

(32-mbox) |

|||||

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

SCITXDx |

SCIRXDx |

SPISIMOx SPISOMIx SPICLKx SPISTEx |

SDAx |

SCLx |

TZx EPWMxA EPWMxB ESYNCI ESYNCO |

MFSRA MDRA MCLKRA MFSXA MDXA |

MCLKXA |

ECAPx |

EQEPxA EQEPxB EQEPxI EQEPxS |

HRCAPx |

CANRXx |

CANTXx |

GPIO Mux

A.Not all peripheral pins are available at the same time due to multiplexing.

Figure 1-1. Functional Block Diagram

ADVANCEINFORMATION

Copyright © 2010–2011, Texas Instruments Incorporated |

TMS320F2806x ( Piccolo™ ) MCUs |

3 |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

INFORMATIONADVANCE

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

www.ti.com |

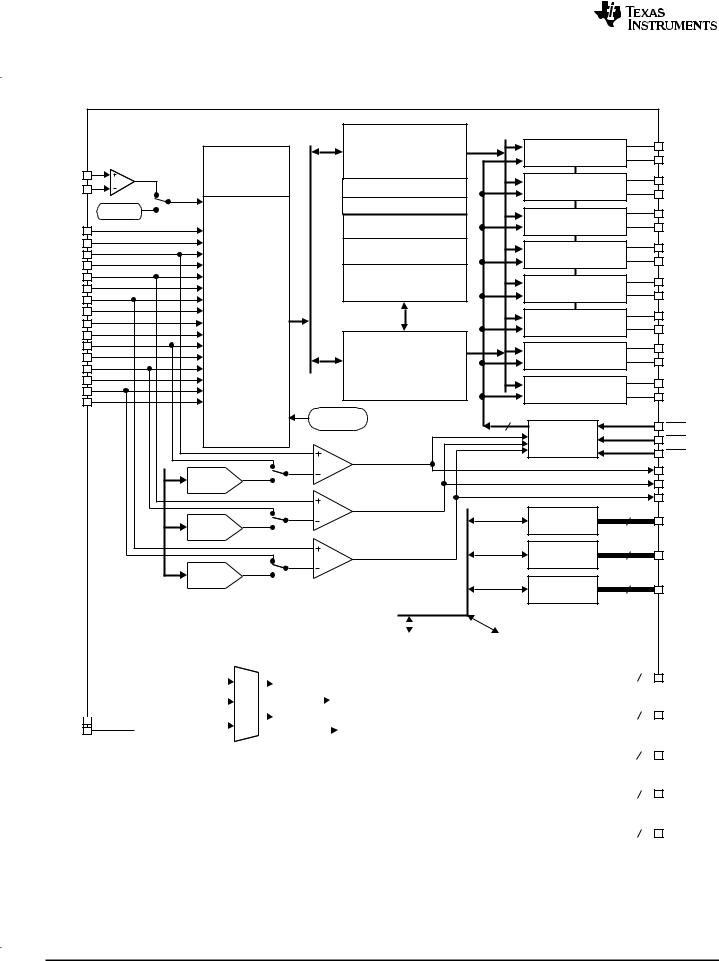

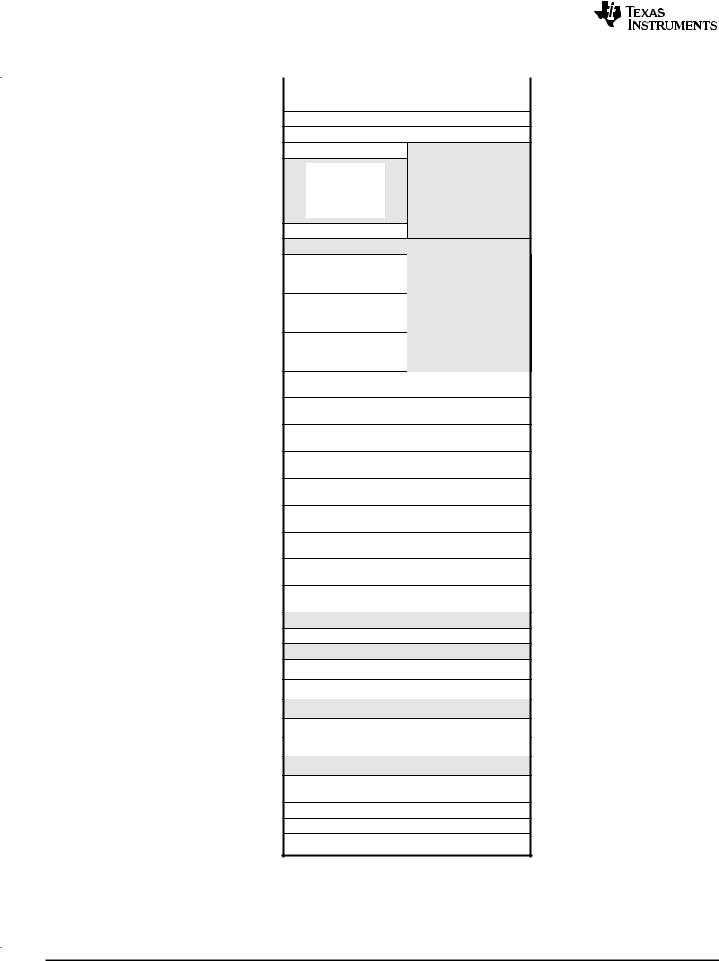

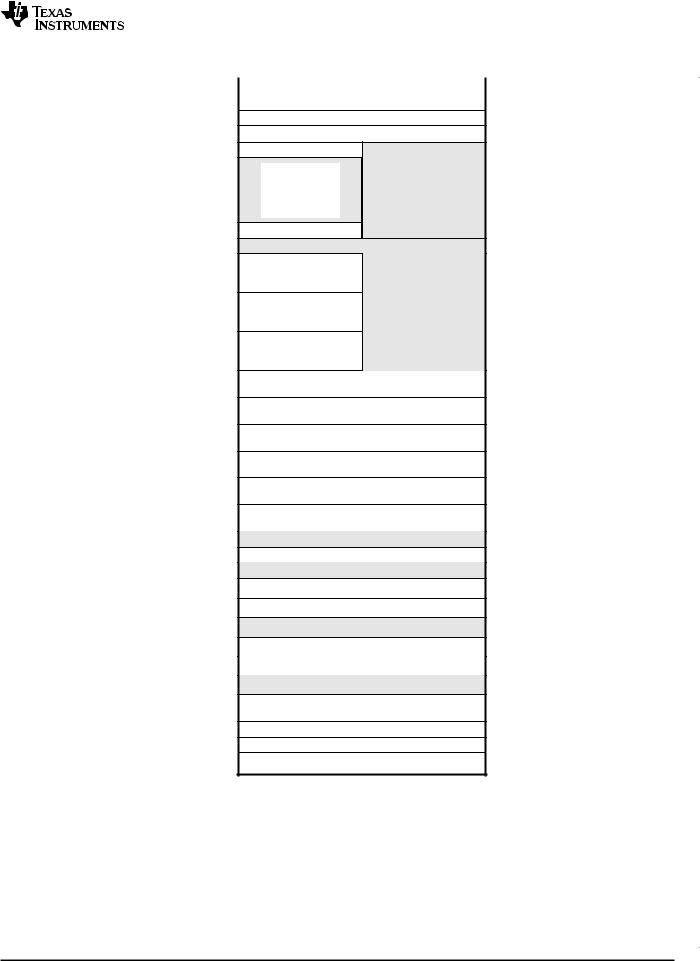

1.4System Device Diagram

|

|

|

C28x |

PWM1 |

|

PWM-1A |

|

|

|

Core |

|

||

|

|

ADC |

(DMA-accessible) |

|

PWM-1B |

|

|

|

(80-MHz) |

|

|||

VREFLO |

|

(DMA- |

|

|

|

|

|

|

PWM2 |

|

PWM-2A |

||

VREFHI |

accessible) |

FPU |

|

|||

|

|

(DMA-accessible) |

|

PWM-2B |

||

|

|

|

|

|

||

|

VREF |

|

VCU |

|

|

PWM-3A |

|

|

|

PWM3 |

|

||

A0 |

|

|

Flash Memory |

(DMA-accessible) |

|

PWM-3B |

|

|

|

|

|

|

|

A1 |

|

|

RAM |

PWM4 |

|

PWM-4A |

A2 |

|

|

|

|||

|

|

|

(DMA-accessible) |

|

PWM-4B |

|

A3 |

|

|

|

|

||

|

|

|

|

|

|

|

A4 |

|

|

RAM |

PWM5 |

|

PWM-5A |

A5 |

|

12-bit |

(Dual-Access) |

|

||

|

(DMA-accessible) |

|

PWM-5B |

|||

A6 |

|

|

|

|||

|

3-MSPS |

|

|

|||

|

|

|

|

|

||

A7 |

|

|

|

|

|

|

|

Dual-S/H |

|

PWM6 |

|

PWM-6A |

|

B0 |

|

|

|

|||

|

|

|

(DMA-accessible) |

|

PWM-6B |

|

B1 |

|

|

|

|

||

|

SOC- |

|

|

|

|

|

B2 |

|

CLA Core |

|

|

PWM-7A |

|

|

based |

PWM7 |

|

|||

B3 |

|

|

80-MHz Floating-Point |

(DMA-accessible) |

|

PWM-7B |

B4 |

|

|

(Accelerator) |

|

||

|

|

|

|

|

||

B5 |

|

|

(DMA-accessible) |

PWM8 |

|

PWM-8A |

B6 |

|

|

|

(DMA-accessible) |

|

PWM-8B |

B7 |

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Temp |

6 |

|

|

|

|

|

Sensor |

|

TZ1 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Trip Zone |

|

TZ2 |

|

|

|

CMP1-Out |

|

|

TZ3 |

|

|

|

|

|

|

|

|

10-bit |

|

|

|

|

CMP1-out |

|

|

|

|

|

CMP2-out |

|

|

DAC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CMP2-Out |

|

|

CMP3-out |

|

|

|

|

|

|

|

|

10-bit |

|

|

eCAP x 3 |

3 |

eCAP |

|

|

|

|

|||

|

DAC |

|

|

|

|

|

|

|

|

CMP3-Out |

eQEP x 2 |

8 |

eQEP |

|

|

|

|

|||

|

|

|

|

|

||

|

10-bit |

|

|

|

|

|

|

DAC |

Analog |

|

HRCAP x 4 |

4 |

HRCAP |

|

|

|

|

|||

|

|

Comparators |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

COMMS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Timers 32-bit |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

Vreg |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Timer-0 |

|

|

|

UART x 2 |

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

Int-Osc-1 |

|

|

CLKSEL |

|

|

WD |

|

|

|

|

|

|

Timer-1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

X1 |

|

|

|

|

Int-Osc-2 |

|

|

PLL |

|

|

|

|

|

|

Timer-2 |

|

|

|

SPI x 2 |

8 |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

X2 |

|

|

|

|

On-chip Osc |

|

|

|

|

|

|

|

|

|

System |

|

GPIO |

|

|

|

|

2 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

POR/BOR |

|

|

|

|

|

|

|

|

|

|

|

|

Control |

|

|

I2C |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CAN |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

McBSP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(DMA-accessible) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Figure 1-2. Peripheral Blocks

4 |

TMS320F2806x ( Piccolo™ ) MCUs |

Copyright © 2010–2011, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com |

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

1 |

TMS320F2806x ( Piccolo™ ) MCUs .................. |

1 |

|

|

1.1 |

Features .............................................. |

1 |

|

1.2 |

Description ........................................... |

2 |

|

1.3 |

Functional Block Diagram ............................ |

3 |

|

1.4 |

System Device Diagram ............................. |

4 |

2 |

Revision History ......................................... |

6 |

|

3 |

Device Overview ........................................ |

7 |

|

|

3.1 |

Device Characteristics ............................... |

7 |

|

3.2 |

Memory Maps ...................................... |

10 |

|

3.3 |

Pin Assignments .................................... |

20 |

|

3.4 |

Signal Descriptions ................................. |

22 |

|

3.5 |

Brief Descriptions ................................... |

31 |

|

3.6 |

Register Map ....................................... |

40 |

|

3.7 |

Device Emulation Registers ........................ |

42 |

|

3.8 |

VREG/BOR/POR ................................... |

43 |

|

3.9 |

System Control ..................................... |

45 |

|

3.10 |

Low-power Modes Block ........................... |

53 |

4 Device and Documentation Support ............... |

54 |

||

|

4.1 |

Getting Started ..................................... |

54 |

|

4.2 |

Development Support .............................. |

54 |

4.3Device and Development Support Tool

|

|

Nomenclature ....................................... |

54 |

|

4.4 |

Documentation Support ............................ |

56 |

|

4.5 |

Community Resources ............................. |

57 |

5 |

Device Operating Conditions ....................... |

58 |

|

|

5.1 |

Absolute Maximum Ratings ........................ |

58 |

|

5.2 |

Recommended Operating Conditions .............. |

58 |

|

5.3 |

Electrical Characteristics ........................... |

59 |

6 |

Peripheral and Electrical Specifications .......... |

60 |

|

|

6.1 |

Parameter Information .............................. |

60 |

6.2 |

Test Load Circuit ................................... |

60 |

6.3 |

Device Clock Table ................................. |

61 |

6.4 |

Clock Requirements and Characteristics ........... |

63 |

6.5 |

Power Sequencing ................................. |

64 |

6.6 |

Current Consumption ............................... |

67 |

6.7Emulator Connection Without Signal Buffering for

|

|

the MCU ............................................ |

69 |

6.8 |

|

Interrupts ............................................ |

70 |

6.9 |

Control Law Accelerator (CLA) Overview .......... |

75 |

|

6.10 |

Analog Block ........................................ |

78 |

|

6.11 |

Detailed Descriptions ............................... |

92 |

|

6.12 |

Serial Peripheral Interface (SPI) Module ........... |

93 |

|

6.13Serial Communications Interface (SCI) Module

..................................................... 102

6.14Multichannel Buffered Serial Port (McBSP) Module

..................................................... 105

6.15Enhanced Controller Area Network (eCAN) Module

..................................................... |

115 |

6.16 Inter-Integrated Circuit (I2C) ...................... |

119 |

6.17Enhanced Pulse Width Modulator (ePWM) Modules

|

(ePWM1/2/3/4/5/6/7/8) ............................ |

122 |

6.18 |

High-Resolution PWM (HRPWM) ................. |

129 |

6.19 |

Enhanced Capture Module (eCAP1) .............. |

130 |

6.20 |

High-Resolution Capture (HRCAP) Module ....... |

132 |

6.21Enhanced Quadrature Encoder Modules (eQEP1/2)

|

..................................................... |

133 |

6.22 |

JTAG Port ......................................... |

136 |

6.23 |

General-Purpose Input/Output (GPIO) MUX ...... |

137 |

6.24 |

Flash Timing ....................................... |

149 |

7 Mechanical Packaging and Orderable |

|

|

Information ............................................ |

151 |

|

7.1 |

Thermal Data ...................................... |

151 |

7.2 |

Packaging Information ............................ |

152 |

ADVANCEINFORMATION

Copyright © 2010–2011, Texas Instruments Incorporated |

Contents |

5 |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

www.ti.com |

2 Revision History

This data sheet revision history highlights the technical changes made to the SPRS698 device-specific data sheet to make it an SPRS698A revision.

Scope: Added 80-pin PN package and 100-pin PZ package.

Added "T" temperature range (–40°C to 105°C).

|

Added new sections. |

|||

|

Information/data on the TMS320F2806x devices is now Advance Information. |

|||

|

ADVANCE INFORMATION concerns new products in the sampling or preproduction phase of |

|||

|

development. Characteristic data and other specifications are subject to change without notice. |

|||

|

|

|

|

|

|

LOCATION |

|

ADDITIONS, DELETIONS, AND MODIFICATIONS |

|

|

|

|

|

|

|

Global |

• Added 80-pin PN package |

||

|

|

|||

|

|

• Added 100-pin PZ package |

||

|

|

• Added "T" temperature range (–40°C to 105°C) |

||

|

|

|

|

|

ADVANCEINFORMATION |

Section 1 |

• Added Section 1.2, Description |

||

TMS320F2806x |

||||

• Figure 1-1, Functional Block Diagram: |

||||

(Piccolo™ ) MCUs |

||||

|

– Removed "32-bit Peripheral Bus" |

|||

|

|

|||

|

|

|

||

Section 3 |

• |

Table 3-1, Hardware Features: |

||

Device Overview |

||||

|

– 6-Channel DMA: Added "0" to TYPE column |

|||

|

|

|||

|

|

– High-resolution capture modules (HRCAP): Added "0" to TYPE column |

||

|

|

– Multi-Channel Buffered Serial Port (McBSP): Added "1" to TYPE column |

||

|

• |

– Updated "Temperature options" |

||

|

Added Section 3.8, VREG/BOR/POR |

|||

|

|

• Added Section 3.2, Memory Maps |

||

|

|

• Figure 3-8, 80-Pin PN/PFP LQFP (Top View): |

||

|

|

|

– Removed SCI-B signals and eQEP2 signals |

|

|

|

• |

Table 3-6, Terminal Functions: |

|

|

|

|

– Added "SCI-B is only available in the PZ and PZP packages" note to DESCRIPTION of PN/PFP pins# 39, |

|

|

|

|

59, 76, 70, 41, 52, 78, 1 |

|

|

|

|

– Added "eQEP2 is only available in the PZ and PZP packages" note to DESCRIPTION of PN/PFP |

|

|

|

|

pins# 77, 31, 62, 61, 33, 32 |

|

|

|

• Added Section 3.5, Brief Descriptions |

||

|

|

• Added Section 3.6, Register Map |

||

|

|

• Added Section 3.7, Device Emulation Registers |

||

|

|

• Added Section 3.9, System Control |

||

|

|

• Added Section 3.10, Low-power Modes Block |

||

|

|

|

|

|

|

Section 4 |

• Added Section 4.1, Getting Started |

||

|

Device and |

|||

|

• |

Section 4.3, Device and Development Support Tool Nomenclature: |

||

|

Documentation Support |

|||

|

|

|

– Updated PACKAGE TYPE in Figure 4-1, Device Nomenclature |

|

|

|

• Added Section 4.4, Documentation Support |

||

|

|

|

||

|

|

Added Section 6, Peripheral and Electrical Specifications |

||

|

|

|

|

|

|

Section 7 |

|

|

|

|

Mechanical Packaging |

• Added Section 7.1, Thermal Data |

||

|

and Orderable |

|||

|

|

|

||

|

Information |

|

|

|

|

|

|

|

|

6 |

Revision History |

Copyright © 2010–2011, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com |

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

3 Device Overview

3.1Device Characteristics

Table 3-1 lists the features of the TMS320F2806x devices.

ADVANCEINFORMATION

Copyright © 2010–2011, Texas Instruments Incorporated |

Device Overview |

7 |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

|

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

www.ti.com |

|||||||

|

|

|

|

|

|

|

|

|

Table 3-1. Hardware Features |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

FEATURE |

TYPE(1) |

28069 |

28068 |

28067 |

28066 |

28065 |

28064 |

28063 |

28062 |

|||||||||||||||||

|

|

|

|

(80 MHz) |

(80 MHz) |

(80 MHz) |

(80 MHz) |

(80 MHz) |

(80 MHz) |

(80 MHz) |

(80 MHz) |

||||||||||||||||

|

|

|

|

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

|

Package Type |

|

|

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

|

|

|

|

LQFP |

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

|

Instruction cycle |

|

– |

12.5 ns |

12.5 ns |

12.5 ns |

12.5 ns |

12.5 ns |

12.5 ns |

12.5 ns |

12.5 ns |

||||||||||||||||

|

Floating-Point Unit (FPU) |

|

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|||||||||

|

Viterbi, Complex Math, CRC Unit (VCU) |

|

|

Yes |

|

Yes |

|

No |

|

No |

|

Yes |

|

Yes |

|

No |

|

No |

|||||||||

|

Control Law Accelerator (CLA) |

0 |

|

Yes |

|

No |

|

No |

|

No |

|

Yes |

|

No |

|

No |

|

No |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

6-Channel DMA |

|

0 |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

ADVANCEINFORMATION |

On-chip Flash (16-bit word) |

– |

128K |

128K |

128K |

128K |

|

64K |

|

64K |

|

64K |

|

64K |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

On-chip SARAM (16-bit word) |

– |

|

50K |

|

50K |

|

50K |

|

34K |

|

50K |

|

50K |

|

34K |

|

26K |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Code security for on-chip |

– |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|||||||||

|

flash/SARAM/OTP blocks |

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Boot ROM (32K x 16) |

– |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

One-time programmable (OTP) ROM |

– |

|

1K |

|

1K |

|

1K |

|

1K |

|

1K |

|

1K |

|

1K |

|

1K |

|||||||||

|

(16-bit word) |

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ePWM outputs |

|

1 |

19 |

|

15 |

19 |

|

15 |

19 |

|

15 |

19 |

|

15 |

19 |

|

15 |

19 |

|

15 |

19 |

|

15 |

19 |

|

15 |

|

High-resolution ePWM Channels |

1 |

8 |

|

6 |

8 |

|

6 |

8 |

|

6 |

8 |

|

6 |

8 |

|

6 |

8 |

|

6 |

8 |

|

6 |

8 |

|

6 |

|

|

eCAP inputs |

|

0 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

||||||||

|

High-resolution capture modules |

0 |

|

4 |

|

4 |

|

4 |

|

4 |

|

4 |

|

4 |

|

4 |

|

4 |

|||||||||

|

(HRCAP) |

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

eQEP modules |

|

0 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

|

Watchdog timer |

|

– |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

||||||||

|

|

MSPS |

|

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

||||||||

|

|

Conversion Time |

|

325 ns |

325 ns |

325 ns |

325 ns |

325 ns |

325 ns |

325 ns |

325 ns |

||||||||||||||||

|

12-Bit ADC |

Channels |

3 |

16 |

|

12 |

16 |

|

12 |

16 |

|

12 |

16 |

|

12 |

16 |

|

12 |

16 |

|

12 |

16 |

|

12 |

16 |

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Temperature Sensor |

|

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

Dual Sample-and-Hold |

|

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

|

Yes |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

32-Bit CPU timers |

– |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

Comparators with Integrated DACs |

0 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

Inter-integrated circuit (I2C) |

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Multi-Channel Buffered Serial Port |

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|||||||||

|

(McBSP) |

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Enhanced Controller Area Network |

0 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|||||||||

|

(eCAN) |

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Serial Peripheral Interface (SPI) |

1 |

|

2 |

|

2 |

|

2 |

|

2 |

|

2 |

|

2 |

|

2 |

|

2 |

|||||||||

|

Serial Communications Interface (SCI) |

0 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

2 |

|

1 |

|

(1)A type change represents a major functional feature difference in a peripheral module. Within a peripheral type, there may be minor differences between devices that do not affect the basic functionality of the module. These device-specific differences are listed in the TMS320x28xx, 28xxx DSP Peripheral Reference Guide (literature number SPRU566) and in the peripheral reference guides.

8 Device Overview Copyright © 2010–2011, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011

Table 3-1. Hardware Features (continued)

|

FEATURE |

TYPE(1) |

|

28069 |

28068 |

28067 |

28066 |

28065 |

28064 |

28063 |

28062 |

|

|||||||||||||||||

|

|

|

|

(80 MHz) |

(80 MHz) |

(80 MHz) |

(80 MHz) |

(80 MHz) |

(80 MHz) |

(80 MHz) |

(80 MHz) |

|

|||||||||||||||||

|

|

|

|

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

100-Pin |

|

80-Pin |

|

|

Package Type |

|

|

|

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

PZ/PZP |

|

PN/PFP |

|

|

|

|

|

|

LQFP |

|

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

LQFP |

|

LQFP |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2-pin Oscillator |

|

|

|

|

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

1 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

0-pin Oscillator |

|

|

|

|

|

2 |

|

2 |

|

2 |

|

2 |

|

2 |

|

2 |

|

2 |

|

2 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

I/O pins |

|

GPIO |

– |

54 |

|

|

40 |

54 |

|

40 |

54 |

|

40 |

54 |

|

40 |

54 |

|

40 |

54 |

|

40 |

54 |

|

40 |

54 |

|

40 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(shared) |

|

AIO |

– |

|

|

6 |

|

6 |

|

6 |

|

6 |

|

6 |

|

6 |

|

6 |

|

6 |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

External interrupts |

– |

|

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

3 |

|

||||||||||

Supply voltage (nominal) |

– |

|

3.3 V |

3.3 V |

3.3 V |

3.3 V |

3.3 V |

3.3 V |

3.3 V |

3.3 V |

|

||||||||||||||||||

|

|

T: –40°C to 105°C |

– |

PZ |

|

|

PN |

PZ |

|

PN |

PZ |

|

PN |

PZ |

|

PN |

PZ |

|

PN |

PZ |

|

PN |

PZ |

|

PN |

PZ |

|

PN |

ADVANCEINFORMATION |

Temperature |

|

S: –40°C to 125°C |

– |

PZP |

|

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

|

options |

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

Q: –40°C to 125°C(1) |

– |

PZP |

|

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

PZP |

|

PFP |

|

Product status(2) |

– |

|

TMX |

TMX |

TMX |

TMX |

TMX |

TMX |

TMX |

TMX |

|

||||||||||||||||||

(1) "Q" refers to Q100 qualification for automotive applications.

(2) See Section 4.3, Device and Development Support Tool Nomenclature, for descriptions of device stages. The "TMX" product status denotes an experimental device that is not necessarily representative of the final device's electrical specifications.

Copyright © 2010–2011, Texas Instruments Incorporated |

Device Overview |

9 |

|

Submit Documentation Feedback |

|

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

www.ti.com |

3.2Memory Maps

In Figure 3-1 through Figure 3-7, the following apply:

•Memory blocks are not to scale.

•Peripheral Frame 0, Peripheral Frame 1, Peripheral Frame 2, and Peripheral Frame 3 memory maps are restricted to data memory only. A user program cannot access these memory maps in program space.

•Protected means the order of Write-followed-by-Read operations is preserved rather than the pipeline order.

•Certain memory ranges are EALLOW protected against spurious writes after configuration.

•Locations 0x3D 7C80–0x3D 7CC0 contain the internal oscillator and ADC calibration routines. These locations are not programmable by the user.

INFORMATIONADVANCE

10 |

Device Overview |

Copyright © 2010–2011, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com |

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

0x00 0000

0x00 0040

0x00 0400

0x00 0800

0x00 0D00

0x00 0E00

0x00 1400

0x00 1480

0x00 1500

0x00 1580

0x00 2000

0x00 5000

0x00 6000

0x00 7000

0x00 8000

0x00 8800

0x00 8C00

0x00 9000

0x00 A000

0x00 C000

0x00 E000

0x01 0000

0x01 2000

0x01 4000 0x3D 7800 0x3D 7BFA 0x3D 7C80

0x3D 7CC0

0x3D 7CD0 0x3D 7E80

0x3D 7EB0 0x3D 8000

0x3F 7FF8 0x3F 8000 0x3F FFC0

Data Space |

Prog Space |

|

|

M0 VECTOR RAM (ENABLED IF VMAP = 0)

M0 SARAM (1K x 16, 0-Wait)

M1 SARAM (1K x 16, 0-Wait)

Peripheral Frame 0

PIE Vector - RAM (256 x 16) (Enabled if VMAP = 1, ENPIE = 1)

Reserved

Peripheral Frame 0

CLA Registers

CLA-to-CPU Message RAM

CPU-to-CLA Message RAM

Reserved

Reserved

Peripheral Frame 3

(4K x 16, Protected)

DMA-Accessible

Peripheral Frame 1 |

Reserved |

|

(4K x 16, Protected) |

||

|

Peripheral Frame 2

(4K x 16, Protected)

L0 DPSARAM (2K x 16)

(0-Wait, Secure Zone + ECSL, CLA Data RAM2)

L1 DPSARAM (1K x 16)

(0-Wait, Secure Zone + ECSL, CLA Data RAM 0)

L2 DPSARAM (1K x 16)

(0-Wait, Secure Zone + ECSL, CLA Data RAM 1)

L3 DPSARAM (4K x 16)

(0-Wait, Secure Zone + ECSL, CLA Program RAM)

L4 SARAM (8K x 16)

(0-Wait, Secure Zone + ECSL, Dual Mapped)

L5 DPSARAM (8K x 16) (0-Wait, DMA RAM 0)

L6 DPSARAM (8K x 16) (0-Wait, DMA RAM 1)

L7 DPSARAM (8K x 16) (0-Wait, DMA RAM 2)

L8 DPSARAM (8K x 16) (0-Wait, DMA RAM 3)

Reserved

User OTP (1K x 16, Secure Zone + ECSL)

Reserved

Calibration Data

Get_mode function

Reserved

PARTID

Calibration Data

Reserved

FLASH

(128K x 16, 8 Sectors, Secure Zone + ECSL)

128-Bit Password

Boot ROM (32K x 16, 0-Wait)

VECTOR (32 VECTORS, ENABLED IF VMAP = 1)

Figure 3-1. 28069 Memory Map

Copyright © 2010–2011, Texas Instruments Incorporated |

Device Overview |

11 |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

ADVANCEINFORMATION

INFORMATIONADVANCE

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

www.ti.com |

0x00 0000

0x00 0040

0x00 0400

0x00 0800

0x00 0D00

0x00 0E00

0x00 1400

0x00 5000

0x00 6000

0x00 7000

0x00 8000

0x00 8800

0x00 8C00

0x00 9000

0x00 A000

0x00 C000

0x00 E000

0x01 0000

0x01 2000

0x01 4000 0x3D 7800 0x3D 7BFA 0x3D 7C80

0x3D 7CC0

0x3D 7CD0 0x3D 7E80

0x3D 7EB0 0x3D 8000

0x3F 7FF8 0x3F 8000 0x3F FFC0

Data Space |

Prog Space |

|

|

M0 VECTOR RAM (ENABLED IF VMAP = 0)

M0 SARAM (1K x 16, 0-Wait)

M1 SARAM (1K x 16, 0-Wait)

Peripheral Frame 0

PIE Vector - RAM (256 x 16)

(Enabled if Reserved VMAP = 1,

ENPIE = 1)

Peripheral Frame 0

Reserved

Peripheral Frame 3

(4K x 16, Protected)

DMA-Accessible

Peripheral Frame 1 |

Reserved |

|

(4K x 16, Protected) |

||

|

Peripheral Frame 2

(4K x 16, Protected)

L0 DPSARAM (2K x 16) (0-Wait, Secure Zone + ECSL)

L1 DPSARAM (1K x 16) (0-Wait, Secure Zone + ECSL)

L2 DPSARAM (1K x 16) (0-Wait, Secure Zone + ECSL)

L3 DPSARAM (4K x 16) (0-Wait, Secure Zone + ECSL)

L4 SARAM (8K x 16)

(0-Wait, Secure Zone + ECSL, Dual Mapped)

L5 DPSARAM (8K x 16) (0-Wait, DMA RAM 0)

L6 DPSARAM (8K x 16) (0-Wait, DMA RAM 1)

L7 DPSARAM (8K x 16) (0-Wait, DMA RAM 2)

L8 DPSARAM (8K x 16) (0-Wait, DMA RAM 3)

Reserved

User OTP (1K x 16, Secure Zone + ECSL)

Reserved

Calibration Data

Get_mode function

Reserved

PARTID

Calibration Data

Reserved

FLASH

(128K x 16, 8 Sectors, Secure Zone + ECSL)

128-Bit Password

Boot ROM (32K x 16, 0-Wait)

VECTOR (32 VECTORS, ENABLED IF VMAP = 1)

Figure 3-2. 28068/28067 Memory Map

12 |

Device Overview |

Copyright © 2010–2011, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com |

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

0x00 0000

0x00 0040

0x00 0400

0x00 0800

0x00 0D00

0x00 0E00

0x00 1400

0x00 5000

0x00 6000

0x00 7000

0x00 8000

0x00 8800

0x00 8C00

0x00 9000

0x00 A000

0x00 C000

0x00 E000

0x01 0000 0x3D 7800 0x3D 7BFA 0x3D 7C80

0x3D 7CC0

0x3D 7CD0 0x3D 7E80

0x3D 7EB0 0x3D 8000

0x3F 7FF8 0x3F 8000 0x3F FFC0

Data Space |

Prog Space |

|

|

M0 VECTOR RAM (ENABLED IF VMAP = 0)

M0 SARAM (1K x 16, 0-Wait)

M1 SARAM (1K x 16, 0-Wait)

Peripheral Frame 0

PIE Vector - RAM (256 x 16)

(Enabled if Reserved VMAP = 1,

ENPIE = 1)

Peripheral Frame 0

Reserved

Peripheral Frame 3

(4K x 16, Protected)

DMA-Accessible

Peripheral Frame 1 |

Reserved |

|

(4K x 16, Protected) |

||

|

Peripheral Frame 2

(4K x 16, Protected)

L0 DPSARAM (2K x 16) (0-Wait, Secure Zone + ECSL)

L1 DPSARAM (1K x 16) (0-Wait, Secure Zone + ECSL)

L2 DPSARAM (1K x 16) (0-Wait, Secure Zone + ECSL)

L3 DPSARAM (4K x 16) (0-Wait, Secure Zone + ECSL)

L4 SARAM (8K x 16)

(0-Wait, Secure Zone + ECSL, Dual Mapped)

L5 DPSARAM (8K x 16) (0-Wait, DMA RAM 0)

L6 DPSARAM (8K x 16) (0-Wait, DMA RAM 1)

Reserved

User OTP (1K x 16, Secure Zone + ECSL)

Reserved

Calibration Data

Get_mode function

Reserved

PARTID

Calibration Data

Reserved

FLASH

(128K x 16, 8 Sectors, Secure Zone + ECSL)

128-Bit Password

Boot ROM (32K x 16, 0-Wait)

VECTOR (32 VECTORS, ENABLED IF VMAP = 1)

Figure 3-3. 28066 Memory Map

ADVANCEINFORMATION

Copyright © 2010–2011, Texas Instruments Incorporated |

Device Overview |

13 |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

INFORMATIONADVANCE

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

www.ti.com |

0x00 0000

0x00 0040

0x00 0400

0x00 0800

0x00 0D00

0x00 0E00

0x00 1400

0x00 1480

0x00 1500

0x00 1580

0x00 2000

0x00 5000

0x00 6000

0x00 7000

0x00 8000

0x00 8800

0x00 8C00

0x00 9000

0x00 A000

0x00 C000

0x00 E000

0x01 0000

0x01 2000

0x01 4000 0x3D 7800 0x3D 7BFA 0x3D 7C80

0x3D 7CC0

0x3D 7CD0 0x3D 7E80

0x3D 7EB0 0x3E 8000

0x3F 7FF8 0x3F 8000 0x3F FFC0

Data Space |

Prog Space |

|

|

M0 VECTOR RAM (ENABLED IF VMAP = 0)

M0 SARAM (1K x 16, 0-Wait)

M1 SARAM (1K x 16, 0-Wait)

Peripheral Frame 0

PIE Vector - RAM (256 x 16) (Enabled if VMAP = 1, ENPIE = 1)

Reserved

Peripheral Frame 0

CLA Registers

CLA-to-CPU Message RAM

CPU-to-CLA Message RAM

Reserved

Reserved

Peripheral Frame 3

(4K x 16, Protected)

DMA-Accessible

Peripheral Frame 1 |

Reserved |

|

(4K x 16, Protected) |

||

|

Peripheral Frame 2

(4K x 16, Protected)

L0 DPSARAM (2K x 16)

(0-Wait, Secure Zone + ECSL, CLA Data RAM2)

L1 DPSARAM (1K x 16)

(0-Wait, Secure Zone + ECSL, CLA Data RAM 0)

L2 DPSARAM (1K x 16)

(0-Wait, Secure Zone + ECSL, CLA Data RAM 1)

L3 DPSARAM (4K x 16)

(0-Wait, Secure Zone + ECSL, CLA Program RAM)

L4 SARAM (8K x 16)

(0-Wait, Secure Zone + ECSL, Dual Mapped)

L5 DPSARAM (8K x 16) (0-Wait, DMA RAM 0)

L6 DPSARAM (8K x 16) (0-Wait, DMA RAM 1)

L7 DPSARAM (8K x 16) (0-Wait, DMA RAM 2)

L8 DPSARAM (8K x 16) (0-Wait, DMA RAM 3)

Reserved

User OTP (1K x 16, Secure Zone + ECSL)

Reserved

Calibration Data

Get_mode function

Reserved

PARTID

Calibration Data

Reserved

FLASH

(64K x 16, 8 Sectors, Secure Zone + ECSL)

128-Bit Password

Boot ROM (32K x 16, 0-Wait)

VECTOR (32 VECTORS, ENABLED IF VMAP = 1)

Figure 3-4. 28065 Memory Map

14 |

Device Overview |

Copyright © 2010–2011, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com |

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

0x00 0000

0x00 0040

0x00 0400

0x00 0800

0x00 0D00

0x00 0E00

0x00 1400

0x00 5000

0x00 6000

0x00 7000

0x00 8000

0x00 8800

0x00 8C00

0x00 9000

0x00 A000

0x00 C000

0x00 E000

0x01 0000

0x01 2000

0x01 4000 0x3D 7800 0x3D 7BFA 0x3D 7C80

0x3D 7CC0

0x3D 7CD0 0x3D 7E80

0x3D 7EB0 0x3E 8000

0x3F 7FF8 0x3F 8000 0x3F FFC0

Data Space |

Prog Space |

|

|

M0 VECTOR RAM (ENABLED IF VMAP = 0)

M0 SARAM (1K x 16, 0-Wait)

M1 SARAM (1K x 16, 0-Wait)

Peripheral Frame 0

PIE Vector - RAM (256 x 16)

(Enabled if Reserved VMAP = 1,

ENPIE = 1)

Peripheral Frame 0

Reserved

Peripheral Frame 3

(4K x 16, Protected)

DMA-Accessible

Peripheral Frame 1 |

Reserved |

|

(4K x 16, Protected) |

||

|

Peripheral Frame 2

(4K x 16, Protected)

L0 DPSARAM (2K x 16) (0-Wait, Secure Zone + ECSL)

L1 DPSARAM (1K x 16) (0-Wait, Secure Zone + ECSL)

L2 DPSARAM (1K x 16) (0-Wait, Secure Zone + ECSL)

L3 DPSARAM (4K x 16) (0-Wait, Secure Zone + ECSL)

L4 SARAM (8K x 16)

(0-Wait, Secure Zone + ECSL, Dual Mapped)

L5 DPSARAM (8K x 16) (0-Wait, DMA RAM 0)

L6 DPSARAM (8K x 16) (0-Wait, DMA RAM 1)

L7 DPSARAM (8K x 16) (0-Wait, DMA RAM 2)

L8 DPSARAM (8K x 16) (0-Wait, DMA RAM 3)

Reserved

User OTP (1K x 16, Secure Zone + ECSL)

Reserved

Calibration Data

Get_mode function

Reserved

PARTID

Calibration Data

Reserved

FLASH

(64K x 16, 8 Sectors, Secure Zone + ECSL)

128-Bit Password

Boot ROM (32K x 16, 0-Wait)

VECTOR (32 VECTORS, ENABLED IF VMAP = 1)

Figure 3-5. 28064 Memory Map

ADVANCEINFORMATION

Copyright © 2010–2011, Texas Instruments Incorporated |

Device Overview |

15 |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

INFORMATIONADVANCE

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

www.ti.com |

0x00 0000

0x00 0040

0x00 0400

0x00 0800

0x00 0D00

0x00 0E00

0x00 1400

0x00 5000

0x00 6000

0x00 7000

0x00 8000

0x00 8800

0x00 8C00

0x00 9000

0x00 A000

0x00 C000

0x00 E000

0x01 0000 0x3D 7800 0x3D 7BFA 0x3D 7C80

0x3D 7CC0

0x3D 7CD0 0x3D 7E80

0x3D 7EB0 0x3E 8000

0x3F 7FF8 0x3F 8000 0x3F FFC0

Data Space |

Prog Space |

|

|

M0 VECTOR RAM (ENABLED IF VMAP = 0)

M0 SARAM (1K x 16, 0-Wait)

M1 SARAM (1K x 16, 0-Wait)

Peripheral Frame 0

PIE Vector - RAM (256 x 16)

(Enabled if Reserved VMAP = 1,

ENPIE = 1)

Peripheral Frame 0

Reserved

Peripheral Frame 3

(4K x 16, Protected)

DMA-Accessible

Peripheral Frame 1 |

Reserved |

|

(4K x 16, Protected) |

||

|

Peripheral Frame 2

(4K x 16, Protected)

L0 DPSARAM (2K x 16) (0-Wait, Secure Zone + ECSL)

L1 DPSARAM (1K x 16) (0-Wait, Secure Zone + ECSL)

L2 DPSARAM (1K x 16) (0-Wait, Secure Zone + ECSL)

L3 DPSARAM (4K x 16) (0-Wait, Secure Zone + ECSL)

L4 SARAM (8K x 16)

(0-Wait, Secure Zone + ECSL, Dual Mapped)

L5 DPSARAM (8K x 16) (0-Wait, DMA RAM 0)

L6 DPSARAM (8K x 16) (0-Wait, DMA RAM 1)

Reserved

User OTP (1K x 16, Secure Zone + ECSL)

Reserved

Calibration Data

Get_mode function

Reserved

PARTID

Calibration Data

Reserved

FLASH

(64K x 16, 8 Sectors, Secure Zone + ECSL)

128-Bit Password

Boot ROM (32K x 16, 0-Wait)

VECTOR (32 VECTORS, ENABLED IF VMAP = 1)

Figure 3-6. 28063 Memory Map

16 |

Device Overview |

Copyright © 2010–2011, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com |

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 |

0x00 0000

0x00 0040

0x00 0400

0x00 0800

0x00 0D00

0x00 0E00

0x00 1400

0x00 5000

0x00 6000

0x00 7000

0x00 8000

0x00 8800

0x00 8C00

0x00 9000

0x00 A000

0x00 C000

0x00 E000 0x3D 7800 0x3D 7BFA 0x3D 7C80

0x3D 7CC0

0x3D 7CD0 0x3D 7E80

0x3D 7EB0 0x3E 8000

0x3F 7FF8 0x3F 8000 0x3F FFC0

Data Space |

Prog Space |

|

|

M0 VECTOR RAM (ENABLED IF VMAP = 0)

M0 SARAM (1K x 16, 0-Wait)

M1 SARAM (1K x 16, 0-Wait)

Peripheral Frame 0

PIE Vector - RAM (256 x 16)

(Enabled if Reserved VMAP = 1,

ENPIE = 1)

Peripheral Frame 0

Reserved

Peripheral Frame 3

(4K x 16, Protected)

DMA-Accessible

Peripheral Frame 1 |

Reserved |

|

(4K x 16, Protected) |

||

|

Peripheral Frame 2

(4K x 16, Protected)

L0 DPSARAM (2K x 16) (0-Wait, Secure Zone + ECSL)

L1 DPSARAM (1K x 16) (0-Wait, Secure Zone + ECSL)

L2 DPSARAM (1K x 16) (0-Wait, Secure Zone + ECSL)

L3 DPSARAM (4K x 16) (0-Wait, Secure Zone + ECSL)

L4 SARAM (8K x 16)

(0-Wait, Secure Zone + ECSL, Dual Mapped)

L5 DPSARAM (8K x 16) (0-Wait, DMA RAM 0)

Reserved

User OTP (1K x 16, Secure Zone + ECSL)

Reserved

Calibration Data

Get_mode function

Reserved

PARTID

Calibration Data

Reserved

FLASH

(64K x 16, 8 Sectors, Secure Zone + ECSL)

128-Bit Password

Boot ROM (32K x 16, 0-Wait)

VECTOR (32 VECTORS, ENABLED IF VMAP = 1)

Figure 3-7. 28062 Memory Map

ADVANCEINFORMATION

Copyright © 2010–2011, Texas Instruments Incorporated |

Device Overview |

17 |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

INFORMATIONADVANCE

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011 www.ti.com

Table 3-2. Addresses of Flash Sectors in F28069/28068/28067/28066

ADDRESS RANGE |

PROGRAM AND DATA SPACE |

|

|

|

|

0x3D 8000 – 0x3D BFFF |

Sector H (16K x 16) |

|

|

|

|

0x3D C000 – 0x3D FFFF |

Sector G (16K x 16) |

|

|

|

|

0x3E 0000 – 0x3E 3FFF |

Sector F (16K x 16) |

|

|

|

|

0x3E 4000 – 0x3E 7FFF |

Sector E (16K x 16) |

|

|

|

|

0x3E 8000 – 0x3E BFFF |

Sector D (16K x 16) |

|

|

|

|

0x3E C000 – 0x3E FFFF |

Sector C (16K x 16) |

|

|

|

|

0x3F 0000 – 0x3F 3FFF |

Sector B (16K x 16) |

|

|

|

|

0x3F 4000 – 0x3F 7F7F |

Sector A (16K x 16) |

|

0x3F 7F80 – 0x3F 7FF5 |

Program to 0x0000 when using the |

|

Code Security Module |

||

|

||

0x3F 7FF6 – 0x3F 7FF7 |

Boot-to-Flash Entry Point |

|

(program branch instruction here) |

||

|

||

0x3F 7FF8 – 0x3F 7FFF |

Security Password (128-Bit) |

|

(Do not program to all zeros) |

||

|

||

|

|

Table 3-3. Addresses of Flash Sectors in F28065/28064/28063/28062

ADDRESS RANGE |

PROGRAM AND DATA SPACE |

||

|

|

|

|

0x3E 8000 |

– 0x3E 9FFF |

Sector H (8K x 16) |

|

|

|

||

0x3E A000 – 0x3E BFFF |

Sector G (8K x 16) |

||

|

|

|

|

0x3E C000 |

– 0x3E DFFF |

Sector F (8K x 16) |

|

|

|

||

0x3E E000 – 0x3E FFFF |

Sector E (8K x 16) |

||

|

|

|

|

0x3F 0000 |

– 0x3F 1FFF |

Sector D (8K x 16) |

|

|

|

|

|

0x3F 2000 |

– 0x3F 3FFF |

Sector C (8K x 16) |

|

|

|

|

|

0x3F 4000 |

– 0x3F 5FFF |

Sector B (8K x 16) |

|

|

|

||

0x3F 6000 – 0x3F 7F7F |

Sector A (8K x 16) |

||

0x3F 7F80 – 0x3F 7FF5 |

Program to 0x0000 when using the |

||

Code Security Module |

|||

|

|

||

0x3F 7FF6 – 0x3F 7FF7 |

Boot-to-Flash Entry Point |

||

(program branch instruction here) |

|||

|

|

||

0x3F 7FF8 – 0x3F 7FFF |

Security Password (128-Bit) |

||

(Do not program to all zeros) |

|||

|

|

||

|

|

|

|

NOTE

•When the code-security passwords are programmed, all addresses between 0x3F 7F80 and 0x3F 7FF5 cannot be used as program code or data. These locations must be programmed to 0x0000.

•If the code security feature is not used, addresses 0x3F 7F80 through 0x3F 7FEF may be used for code or data. Addresses 0x3F 7FF0 – 0x3F 7FF5 are reserved for data and should not contain program code.

Table 3-4 shows how to handle these memory locations.

18 |

Device Overview |

Copyright © 2010–2011, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320F28069 TMS320F28068 TMS320F28067 TMS320F28066 TMS320F28065

TMS320F28064 TMS320F28063 TMS320F28062

TMS320F28069, TMS320F28068, TMS320F28067, TMS320F28066

TMS320F28065, TMS320F28064, TMS320F28063, TMS320F28062

www.ti.com SPRS698A –NOVEMBER 2010 –REVISED JANUARY 2011

Table 3-4. Impact of Using the Code Security Module

ADDRESS |

|

FLASH |

|

|

|

|

|

CODE SECURITY ENABLED |

|

CODE SECURITY DISABLED |

|

|

|

||

|

|

|

|

0x3F 7F80 – 0x3F 7FEF |

Fill with 0x0000 |

|

Application code and data |

|

|

|

|

0x3F 7FF0 – 0x3F 7FF5 |

|

Reserved for data only |

|

|

|

||

|

|

|

|

Peripheral Frame 1 and Peripheral Frame 2 are grouped together to enable these blocks to be write/read peripheral block protected. The protected mode makes sure that all accesses to these blocks happen as written. Because of the pipeline, a write immediately followed by a read to different memory locations, will appear in reverse order on the memory bus of the CPU. This can cause problems in certain peripheral applications where the user expected the write to occur first (as written). The CPU supports a block protection mode where a region of memory can be protected so that operations occur as written (the penalty is extra cycles are added to align the operations). This mode is programmable and by default, it protects the selected zones.

The wait-states for the various spaces in the memory map area are listed in Table 3-5.