TEXAS INSTRUMENTS TMS320F2810, TMS320F2811, TMS320F2812, TMS320C2810, TMS320C2811 Technical data

...

TMS320F2811

TMS320F2810, TMS320F2811, TMS320F2812 TMS320C2810, TMS320C2811, TMS320C2812 Digital Signal Processors

Data Manual

Literature Number: SPRS174M

April 2001 − Revised October 2005

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

Products |

|

Applications |

|

Amplifiers |

amplifier.ti.com |

Audio |

www.ti.com/audio |

Data Converters |

dataconverter.ti.com |

Automotive |

www.ti.com/automotive |

DSP |

dsp.ti.com |

Broadband |

www.ti.com/broadband |

Interface |

interface.ti.com |

Digital Control |

www.ti.com/digitalcontrol |

Logic |

logic.ti.com |

Military |

www.ti.com/military |

Power Mgmt |

power.ti.com |

Optical Networking |

www.ti.com/opticalnetwork |

Microcontrollers |

microcontroller.ti.com |

Security |

www.ti.com/security |

|

|

Telephony |

www.ti.com/telephony |

|

|

Video & Imaging |

www.ti.com/video |

|

|

Wireless |

www.ti.com/wireless |

Mailing Address: |

Texas Instruments |

|

|

|

Post Office Box 655303 Dallas, Texas 75265 |

|

|

Copyright 2005, Texas Instruments Incorporated

Revision History

REVISION HISTORY

This data sheet revision history highlights the technical changes made to the SPRS174L device-specific data sheet to make it an SPRS174M revision.

Global change:

|

PAGE |

ADDITIONS/CHANGES/DELETIONS |

|

|

|

||

|

NO. |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

15 |

Deleted the note on Table 2−1 on temperature options |

|

|

|

||

|

|

|

|

|

|

||

|

22 |

Modified description of |

|

in Table 2−2 |

|

|

|

|

TRST |

|

|

|

|||

|

|

|

|

|

|

||

|

26 |

Changed description of GPIOD0, GPIOD1, GPIOD5, and GPIOD6 signals |

|

|

|

||

|

|

|

|

|

|

||

|

19 |

Changed some signals in Table 2−2 from I/O/Z to I/O and changed some descriptions to include GPIO |

|

|

|

||

|

|

|

|

|

|

||

|

29 |

Changed Peripheral Frame data in memory map (Figure 3−2) |

|

|

|

||

|

|

|

|

|

|

||

|

30 |

Changed Peripheral Frame data in memory map (Figure 3−3) |

|

|

|

||

|

|

|

|

|

|

||

|

31 |

Changed Peripheral Frame data in memory map (Figure 3−4) |

|

|

|

||

|

|

|

|

|

|

||

|

36 |

Changed note in Section 3.2.6 by deleting “the pipeline mode is not available for the OTP block.” |

|

|

|

||

|

|

|

|

|

|

||

|

37 |

Changed header format of Table 3−4 |

|

|

|

||

|

|

|

|

|

|

||

|

37 |

Modified note under Section 3.2.11, making “passwords” singular instead of plural |

|

|

|

||

|

|

|

|

|

|

||

|

39 |

Modified description of low-power modes in Section 3.2.17 |

|

|

|

||

|

|

|

|

|

|

||

|

43 |

Changed DEVICEID to REVID and reserved to PARTID in Table 3−8 |

|

|

|

||

|

|

|

|

|

|

||

|

45 |

Modified text in Section 3.5.1 |

|

|

|

||

|

|

|

|

|

|

||

|

57 |

Modified note in Section 4.1 concerning use of CPU timers |

|

|

|

||

|

|

|

|

|

|||

|

91 |

Modified 6.1 Absolute Maximum Ratings table (added junction temperature range, removed note on S version temperature |

|

|

|||

|

|

range, and removed VDD3VFL range) |

|

|

|

||

|

92 |

Deleted note on temperature options from 6.2 Recommended Operating Conditions |

|

|

|

||

|

|

|

|

|

|

||

|

93 |

Changed IOZ in 6.3 Electrical Characteristics Over Recommended Operating Conditions |

|

|

|

||

|

|

|

|

|

|||

|

94 |

Modified 6.4 Current Consumption by Power−supply Pins Over Recommended Operating conditions During Low-Power |

|

|

|||

|

|

Modes at 150-MHz SYSCLKOUT (TMS320F281x) table |

|

|

|

||

|

|

|

|

|

|||

|

94 |

Modified 6.5 Current Consumption by Power-Supply Pins Over Recommended Operating conditions During Low-Power |

|

|

|||

|

|

Modes at 150-MHz SYSCLKOUT (TMS320C281x) |

|

|

|

||

|

|

|

|

|

|

||

|

95 |

Changed wording of note in Figure 6−1 |

|

|

|

||

|

|

|

|

|

|

||

|

96 |

Changed wording of note in Figure 6−3 |

|

|

|

||

|

|

|

|

|

|

||

|

97 |

Changed IOCA to IDDA in note in Table 6−1 |

|

|

|

||

|

|

|

|

|

|

||

|

99 |

Modified Section 6.9, Signal Transition Levels |

|

|

|

||

|

|

|

|

|

|

||

|

101 |

Modified Table 6−4, adding values for XCLKIN with and without PLL |

|

|

|

||

|

|

|

|

|

|

||

|

102 |

Modified Table 6−5 |

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

April 2001 − Revised October 2005 |

SPRS174M |

3 |

|||||

Revision History

PAGE |

ADDITIONS/CHANGES/DELETIONS |

|

NO. |

||

|

||

|

|

|

103 |

Modified Table 6−9 |

|

|

|

|

108 |

Modified Table 6−11 by moving values from MIN column to MAX column |

|

|

|

|

109 |

Modified Table 6−13 by moving values from MIN column to MAX column |

|

|

|

|

109 |

Modified td(WAKE-STBY) duration in Figure 6−15 |

|

|

|

|

110 |

Modified note C in Figure 6−16 |

|

|

|

|

110 |

Modified Table 6−15 by moving values from MIN column to MAX column |

|

|

|

|

111 |

Changed equation for IQT in note on Table 6−17 |

|

|

|

|

113 |

Changed equation for IQT in note on Table 6−21 |

|

|

|

|

115 |

Changed equation for IQT in note on Table 6−23 |

|

|

|

|

115 |

Modified Figure 6−23 |

|

|

|

|

128, 132 |

Clarified (in Table 6−32 and Table 6−37) that t dis(XD)XRNW is the maximum time the DSP takes to release the data bus after |

|

|

XR/W goes inactive high. Previously it was described as the minimum time external devices should wait to drive the data |

|

|

bus. |

|

|

|

|

141 |

Changed bit numbers and register in Table 6−44 |

|

|

|

|

149, 150, |

Changed value of 4.5 MHz to 4.6875 MHz in note on Table 6−50, Table 6−52, Table 6−54, and Table 6−56 |

|

151, 152 |

|

|

|

|

|

153 |

Modified Table 6−57 |

|

|

|

|

153 |

Added the word ambient to temperature ranges in 6.32.1 |

|

|

|

|

154 |

Added new section header 6.33 for ROM timing |

|

|

|

4 |

SPRS174M |

April 2001 − Revised October 2005 |

|

|

|

Contents |

|

|

|

Contents |

|

|

Section |

|

|

Page |

|

1 |

Features . . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . 13 |

|

2 |

Introduction . |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 14 |

|

2.1 |

Description . . |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 14 |

|

2.2 |

Device Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 15 |

|

|

2.3 |

Pin Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 16 |

|

|

|

2.3.1 |

Terminal Assignments for the GHH Package . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 16 |

|

|

2.3.2 |

Pin Assignments for the PGF Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 17 |

|

|

2.3.3 |

Pin Assignments for the PBK Package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 18 |

|

2.4 |

Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 19 |

|

|

3 |

Functional Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 28 |

|

|

3.1 |

Memory Map |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 29 |

|

3.2 |

Brief Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 34 |

|

|

|

3.2.1 |

C28x CPU . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 34 |

|

|

3.2.2 |

Memory Bus (Harvard Bus Architecture) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 35 |

|

|

3.2.3 |

Peripheral Bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 35 |

|

|

3.2.4 |

Real-Time JTAG and Analysis . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 35 |

|

|

3.2.5 |

External Interface (XINTF) (2812 Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 35 |

|

|

3.2.6 |

Flash (F281x Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 36 |

|

|

3.2.7 |

ROM (C281x Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 36 |

|

|

3.2.8 |

M0, M1 SARAMs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 36 |

|

|

3.2.9 |

L0, L1, H0 SARAMs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 36 |

|

|

3.2.10 |

Boot ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 36 |

|

|

3.2.11 |

Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 37 |

|

|

3.2.12 |

Peripheral Interrupt Expansion (PIE) Block . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 38 |

|

|

3.2.13 |

External Interrupts (XINT1, XINT2, XINT13, XNMI) . . . . . . . . . . . . . . . . . . . . |

. . . 38 |

|

|

3.2.14 |

Oscillator and PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 38 |

|

|

3.2.15 |

Watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 38 |

|

|

3.2.16 |

Peripheral Clocking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 38 |

|

|

3.2.17 |

Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 39 |

|

|

3.2.18 |

Peripheral Frames 0, 1, 2 (PFn) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 39 |

|

|

3.2.19 |

General-Purpose Input/Output (GPIO) Multiplexer . . . . . . . . . . . . . . . . . . . . . |

. . . 39 |

|

|

3.2.20 |

32-Bit CPU-Timers (0, 1, 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 39 |

|

|

3.2.21 |

Control Peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 40 |

|

|

3.2.22 |

Serial Port Peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 40 |

|

3.3 |

Register Map |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 40 |

|

3.4 |

Device Emulation Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 43 |

|

|

3.5 |

External Interface, XINTF (2812 Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 43 |

|

|

|

3.5.1 |

Timing Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 45 |

|

|

3.5.2 |

XREVISION Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 45 |

|

3.6 |

Interrupts . . . |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 46 |

|

|

3.6.1 |

External Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 49 |

|

3.7 |

System Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 50 |

|

|

3.8 |

OSC and PLL Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 52 |

|

|

|

3.8.1 |

Loss of Input Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 53 |

|

3.9 |

PLL-Based Clock Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 53 |

|

|

3.10 |

External Reference Oscillator Clock Option . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 55 |

|

|

3.11 |

Watchdog Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 55 |

|

|

April 2001 − Revised October 2005 |

SPRS174M |

5 |

Contents

3.12 |

Low-Power Modes Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

56 |

|

4 |

Peripherals . |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

57 |

4.1 |

32-Bit CPU-Timers 0/1/2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

57 |

|

4.2 |

Event Manager Modules (EVA, EVB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

60 |

|

|

4.2.1 |

General-Purpose (GP) Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

63 |

|

4.2.2 |

Full-Compare Units . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

63 |

|

4.2.3 |

Programmable Deadband Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

63 |

|

4.2.4 |

PWM Waveform Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

63 |

|

4.2.5 |

Double Update PWM Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

63 |

|

4.2.6 |

PWM Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

64 |

|

4.2.7 |

Capture Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

64 |

|

4.2.8 |

Quadrature-Encoder Pulse (QEP) Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

64 |

|

4.2.9 |

External ADC Start-of-Conversion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

65 |

4.3 |

Enhanced Analog-to-Digital Converter (ADC) Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

65 |

|

4.4 |

Enhanced Controller Area Network (eCAN) Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

70 |

|

4.5 |

Multichannel Buffered Serial Port (McBSP) Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

74 |

|

4.6 |

Serial Communications Interface (SCI) Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

78 |

|

4.7 |

Serial Peripheral Interface (SPI) Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

81 |

|

4.8 |

GPIO MUX . |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

84 |

5 |

Development Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

87 |

|

5.1 |

Device and Development Support Tool Nomenclature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

87 |

|

5.2 |

Documentation Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

88 |

|

6 |

Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

91 |

|

6.1 |

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

91 |

|

6.2 |

Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

92 |

|

6.3 |

Electrical Characteristics Over Recommended Operating Conditions |

|

|

|

(Unless Otherwise Noted) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

93 |

|

6.4Current Consumption by Power-Supply Pins Over Recommended Operating Conditions

During Low-Power Modes at 150-MHz SYSCLKOUT (TMS320F281x) . . . . . . . . . . . . . . . . . . 94

6.5Current Consumption by Power-Supply Pins Over Recommended Operating Conditions

|

During Low-Power Modes at 150-MHz SYSCLKOUT (TMS320C281x) . . . . . . . . . . . . . . . . . |

. 94 |

|

6.6 |

Current Consumption Graphs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 95 |

|

6.7 |

Reducing Current Consumption . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 97 |

|

6.8 |

Power Sequencing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 97 |

|

6.9 |

Signal Transition Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 99 |

|

6.10 |

Timing Parameter Symbology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

100 |

|

6.11 |

General Notes on Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

100 |

|

6.12 |

Test Load Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

100 |

|

6.13 |

Device Clock Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

101 |

|

6.14 |

Clock Requirements and Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

101 |

|

|

6.14.1 |

Input Clock Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

101 |

|

6.14.2 |

Output Clock Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

103 |

6.15 |

Reset Timing |

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

103 |

6.16 |

Low-Power Mode Wakeup Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

108 |

|

6.17 |

Event Manager Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

111 |

|

|

6.17.1 |

PWM Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

111 |

|

6.17.2 |

Interrupt Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

113 |

6.18 |

General-Purpose Input/Output (GPIO) − Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

114 |

|

6.19 |

General-Purpose Input/Output (GPIO) − Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

115 |

|

6.20 |

SPI Master Mode Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

116 |

|

6.21 |

SPI Slave Mode Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

120 |

|

6 |

SPRS174M |

April 2001 − Revised October 2005 |

Contents

6.22 External Interface (XINTF) Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123 6.23 XINTF Signal Alignment to XCLKOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125 6.24 External Interface Read Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127 6.25 External Interface Write Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128 6.26 External Interface Ready-on-Read Timing With One External Wait State . . . . . . . . . . . . . . . . 129 6.27 External Interface Ready-on-Write Timing With One External Wait State . . . . . . . . . . . . . . . . 132 6.28 XHOLD and XHOLDA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135 6.29 XHOLD/XHOLDA Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 136 6.30 On-Chip Analog-to-Digital Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

6.30.1 ADC Absolute Maximum Ratings† . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 138

6.30.2ADC Electrical Characteristics Over Recommended Operating

Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 139

6.30.3Current Consumption for Different ADC Configurations

(at 25-MHz ADCCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 140 6.30.4 ADC Power-Up Control Bit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 141 6.30.5 Detailed Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142 6.30.6 Sequential Sampling Mode (Single-Channel) (SMODE = 0) . . . . . . . . . . . . . . . 142 6.30.7 Simultaneous Sampling Mode (Dual-Channel) (SMODE = 1) . . . . . . . . . . . . . . 144 6.30.8 Definitions of Specifications and Terminology . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

6.31 Multichannel Buffered Serial Port (McBSP) Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146 6.31.1 McBSP Transmit and Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 146 6.31.2 McBSP as SPI Master or Slave Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 149

6.32 Flash Timing (F281x Only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153 6.32.1 Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153 6.33 ROM Timing (C281x only) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

6.34 Migrating From F281x Devices to C281x Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

7 Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 156

April 2001 − Revised October 2005 |

SPRS174M |

7 |

Figures |

|

List of Figures |

|

Figure |

Page |

2−1. TMS320F2812 and TMS320C2812 179-Ball GHH MicroStar BGAE (Bottom View) . . . . . . . . . . . . . . . . |

. .16 |

2−2. TMS320F2812 and TMS320C2812 176-Pin PGF LQFP (Top View) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.17 |

2−3. TMS320F2810, TMS320F2811, TMS320C2810, and TMS320C2811 128-Pin PBK LQFP |

|

(Top View) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 18 |

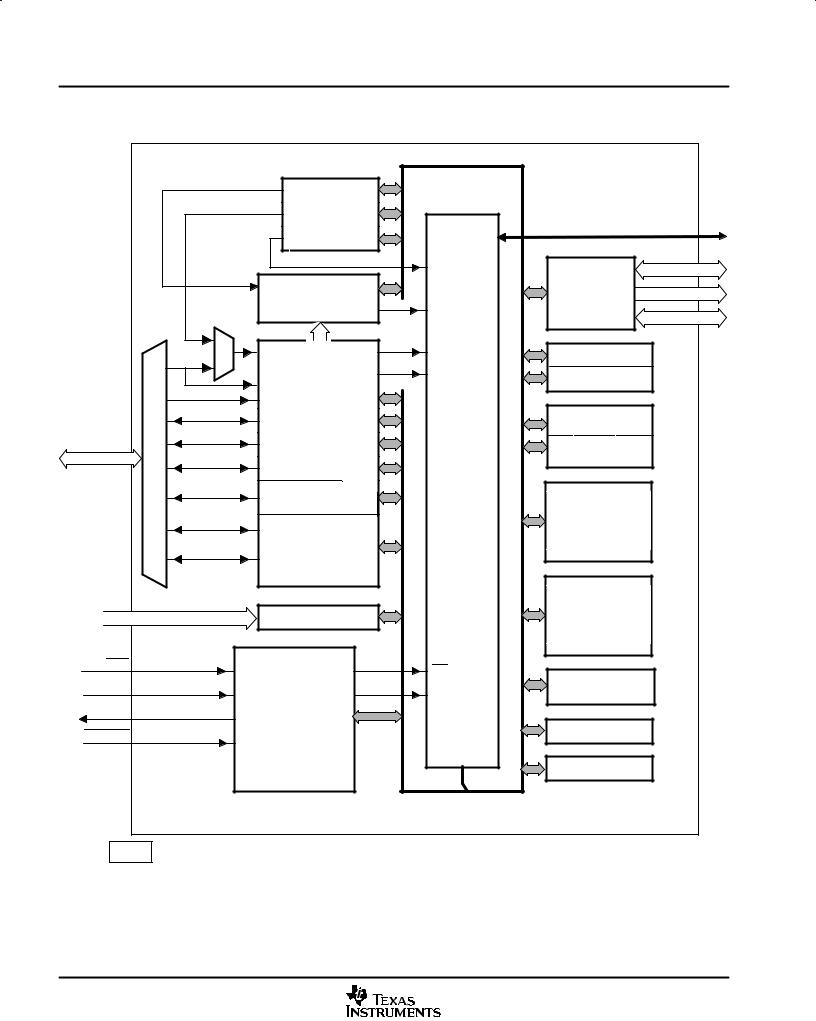

3−1. Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 28 |

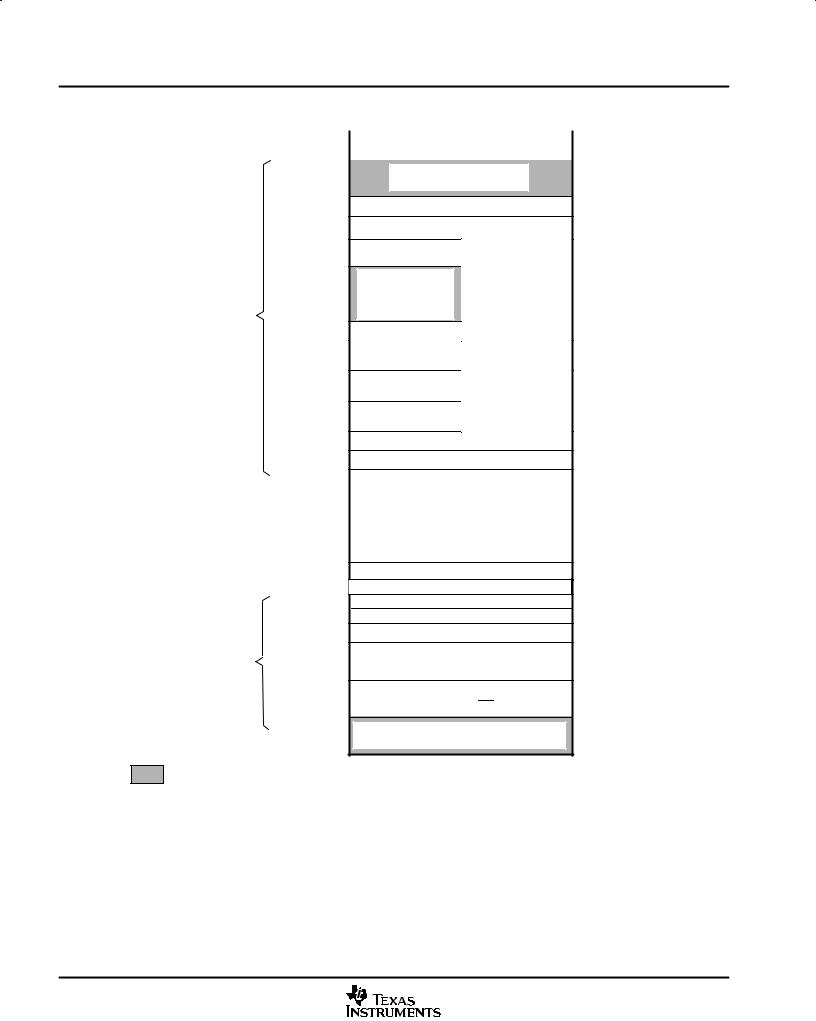

3−2. F2812/C2812 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 29 |

3−3. F2811/C2811 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 30 |

3−4. F2810/C2810 Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 31 |

3−5. External Interface Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.44 |

3−6. Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 46 |

3−7. Multiplexing of Interrupts Using the PIE Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.47 |

3−8. Clock and Reset Domains . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 50 |

3−9. OSC and PLL Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 52 |

3−10. Recommended Crystal/Clock Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.54 |

3−11. Watchdog Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 55 |

4−1. CPU-Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 57 |

4−2. CPU-Timer Interrupts Signals and Output Signal . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.58 |

4−3. Event Manager A Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.62 |

4−4. Block Diagram of the F281x and C281x ADC Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.66 |

4−5. ADC Pin Connections With Internal Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.67 |

4−6. ADC Pin Connections With External Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.68 |

4−7. eCAN Block Diagram and Interface Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.71 |

4−8. eCAN Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 72 |

4−9. McBSP Module With FIFO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 75 |

4−10. Serial Communications Interface (SCI) Module Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.80 |

4−11. Serial Peripheral Interface Module Block Diagram (Slave Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.83 |

4−12. GPIO/Peripheral Pin Multiplexing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.86 |

5−1. TMS320x28x Device Nomenclature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.88 |

6−1. F2812/F2811/F2810 Typical Current Consumption Over Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.95 |

6−2. F2812/F2811/F2810 Typical Power Consumption Over Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.95 |

6−3. C2812/C2811/C2810 Typical Current Consumption Over Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.96 |

6−4. C2812/C2811/C2810 Typical Power Consumption Over Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.96 |

6−5. F2812/F2811/F2810 Typical Power-Up and Power-Down Sequence − Option 2 . . . . . . . . . . . . . . . . . . . . |

.98 |

6−6. Output Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 99 |

6−7. Input Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 99 |

6−8. 3.3-V Test Load Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

100 |

6−9. Clock Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

103 |

6−10. Power-on Reset in Microcomputer Mode (XMP/MC = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

104 |

6−11. Power-on Reset in Microprocessor Mode (XMP/MC = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

105 |

6−12. Warm Reset in Microcomputer Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

106 |

6−13. Effect of Writing Into PLLCR Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

107 |

8 |

SPRS174M |

April 2001 − Revised October 2005 |

|

Figures |

6−14. IDLE Entry and Exit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 108 |

6−15. STANDBY Entry and Exit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .109 |

6−16. HALT Wakeup Using XNMI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 110 |

6−17. PWM Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 111 |

6−18. TDIRx Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 111 |

6−19. EVASOC Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 112 |

6−20. EVBSOC Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 112 |

6−21. External Interrupt Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 114 |

6−22. General-Purpose Output Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.114 |

6−23. GPIO Input Qualifier − Example Diagram for QUALPRD = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.115 |

6−24. General-Purpose Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.115 |

6−25. SPI Master Mode External Timing (Clock Phase = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.117 |

6−26. SPI Master External Timing (Clock Phase = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.119 |

6−27. SPI Slave Mode External Timing (Clock Phase = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.121 |

6−28. SPI Slave Mode External Timing (Clock Phase = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.122 |

6−29. Relationship Between XTIMCLK and SYSCLKOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.125 |

6−30. Example Read Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 127 |

6−31. Example Write Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 128 |

6−32. Example Read With Synchronous XREADY Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.130 |

6−33. Example Read With Asynchronous XREADY Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.131 |

6−34. Write With Synchronous XREADY Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.133 |

6−35. Write With Asynchronous XREADY Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.134 |

6−36. External Interface Hold Waveform . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.136 |

6−37. XHOLD /XHOLDA Timing Requirements (XCLKOUT = 1/2 XTIMCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 137 |

6−38. ADC Analog Input Impedance Model . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.141 |

6−39. ADC Power-Up Control Bit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.141 |

6−40. Sequential Sampling Mode (Single-Channel) Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.143 |

6−41. Simultaneous Sampling Mode Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.144 |

6−42. McBSP Receive Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 148 |

6−43. McBSP Transmit Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 148 |

6−44. McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.149 |

6−45. McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.150 |

6−46. McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.151 |

6−47. McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.152 |

April 2001 − Revised October 2005 |

SPRS174M |

9 |

Tables |

|

List of Tables |

|

Table |

Page |

2−1. Hardware Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 15 |

2−2. Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 19 |

3−1. Addresses of Flash Sectors in F2812 and F2811 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .32 |

3−2. Addresses of Flash Sectors in F2810 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .32 |

3−3. Wait States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 34 |

3−4. Boot Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 37 |

3−5. Peripheral Frame 0 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 41 |

3−6. Peripheral Frame 1 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 41 |

3−7. Peripheral Frame 2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 42 |

3−8. Device Emulation Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 43 |

3−9. XINTF Configuration and Control Register Mappings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .45 |

3−10. XREVISION Register Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .45 |

3−11. PIE Peripheral Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 47 |

3−12. PIE Configuration and Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .48 |

3−13. External Interrupts Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 49 |

3−14. PLL, Clocking, Watchdog, and Low-Power Mode Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .51 |

3−15. PLLCR Register Bit Definitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .52 |

3−16. Possible PLL Configuration Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .54 |

3−17. F281x and C281x Low-Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .56 |

4−1. CPU-Timers 0, 1, 2 Configuration and Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .59 |

4−2. Module and Signal Names for EVA and EVB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .60 |

4−3. EVA Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 61 |

4−4. ADC Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 69 |

4−5. 3.3-V eCAN Transceivers for the TMS320F281x and TMS320C281x DSPs . . . . . . . . . . . . . . . . . . . . . . |

. .71 |

4−6. CAN Registers Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 73 |

4−7. McBSP Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 76 |

4−8. SCI-A Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 79 |

4−9. SCI-B Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 79 |

4−10. SPI Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 82 |

4−11. GPIO Mux Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 84 |

4−12. GPIO Data Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 85 |

6−1. Typical Current Consumption by Various Peripherals (at 150 MHz) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .97 |

6−2. Recommended “Low-Dropout Regulators” . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. .98 |

6−3. TMS320F281x and TMS320C281x Clock Table and Nomenclature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.101 |

6−4. Input Clock Frequency . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 101 |

6−5. XCLKIN Timing Requirements − PLL Bypassed or Enabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

102. |

6−6. XCLKIN Timing Requirements − PLL Disabled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

102. |

6−7. Possible PLL Configuration Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.102 |

6−8. XCLKOUT Switching Characteristics (PLL Bypassed or Enabled) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.103 |

6−9. Reset (XRS) Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.103 |

6−10. IDLE Mode Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.108 |

6−11. IDLE Mode Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.108 |

6−12. STANDBY Mode Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.108 |

6−13. STANDBY Mode Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.109 |

6−14. HALT Mode Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.110 |

6−15. HALT Mode Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.110 |

10 |

SPRS174M |

April 2001 − Revised October 2005 |

|

Tables |

6−16. PWM Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . 111 |

6−17. Timer and Capture Unit Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 111 |

6−18. External ADC Start-of-Conversion − EVA − Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . |

112. |

6−19. External ADC Start-of-Conversion − EVB − Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . |

112. |

6−20. Interrupt Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.113 |

6−21. Interrupt Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.113 |

6−22. General-Purpose Output Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.114 |

6−23. General-Purpose Input Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.115 |

6−24. SPI Master Mode External Timing (Clock Phase = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.116 |

6−25. SPI Master Mode External Timing (Clock Phase = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.118 |

6−26. SPI Slave Mode External Timing (Clock Phase = 0) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.120 |

6−27. SPI Slave Mode External Timing (Clock Phase = 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.122 |

6−28. Relationship Between Parameters Configured in XTIMING and Duration of Pulse . . . . . . . . . . . . . . . . |

.123 |

6−29. XINTF Clock Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 125 |

6−30. External Memory Interface Read Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.127 |

6−31. External Memory Interface Read Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.127 |

6−32. External Memory Interface Write Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.128 |

6−33. External Memory Interface Read Switching Characteristics (Ready-on-Read, 1 Wait State) . . . . . . . . |

.129 |

6−34. External Memory Interface Read Timing Requirements (Ready-on-Read, 1 Wait State) . . . . . . . . . . . |

.129 |

6−35. Synchronous XREADY Timing Requirements (Ready-on-Read, 1 Wait State) . . . . . . . . . . . . . . . . . . . . |

.129 |

6−36. Asynchronous XREADY Timing Requirements (Ready-on-Read, 1 Wait State) . . . . . . . . . . . . . . . . . . . |

.129 |

6−37. External Memory Interface Write Switching Characteristics (Ready-on-Write, 1 Wait State) . . . . . . . |

.132 |

6−38. Synchronous XREADY Timing Requirements (Ready-on-Write, 1 Wait State) . . . . . . . . . . . . . . . . . . . . |

.132 |

6−39. Asynchronous XREADY Timing Requirements (Ready-on-Write, 1 Wait State) . . . . . . . . . . . . . . . . . . . |

.132 |

6−40. XHOLD /XHOLDA Timing Requirements (XCLKOUT = XTIMCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 136 |

6−41. XHOLD /XHOLDA Timing Requirements (XCLKOUT = 1/2 XTIMCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 137 |

6−42. DC Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 139 |

6−43. AC Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 140 |

6−44. ADC Power-Up Delays . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 141 |

6−45. Sequential Sampling Mode Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.143 |

6−46. Simultaneous Sampling Mode Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.144 |

6−47. McBSP Timing Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.146 |

6−48. McBSP Switching Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.147 |

6−49. McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 0) . . . . . . . . . . . . . . |

.149 |

6−50. McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 0) . . . . . . . . . . |

.149 |

6−51. McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 0) . . . . . . . . . . . . . . |

.150 |

6−52. McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 0) . . . . . . . . . . |

.150 |

6−53. McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 1) . . . . . . . . . . . . . . |

.151 |

6−54. McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 1) . . . . . . . . . . |

.151 |

6−55. McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 1) . . . . . . . . . . . . . . |

.152 |

6−56. McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 1) . . . . . . . . . . |

.152 |

6−57. Flash Parameters at 150-MHz SYSCLKOUT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.153 |

6−58. Flash/OTP Access Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 153 |

6−59. Minimum Required Wait-States at Different Frequencies (F281x devices) . . . . . . . . . . . . . . . . . . . . . . . |

.153 |

6−60. ROM Access Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. 154 |

6−61. Minimum Required Wait-States at Different Frequencies (C281x devices) . . . . . . . . . . . . . . . . . . . . . . . |

.154 |

7−1. Thermal Resistance Characteristics for 179-Ball GHH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.156 |

7−2. Thermal Resistance Characteristics for 179-Ball ZHH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

.156 |

April 2001 − Revised October 2005 |

SPRS174M |

11 |

Tables

7−3. Thermal Resistance Characteristics for 176-Pin PGF . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .156 7−4. Thermal Resistance Characteristics for 128-Pin PBK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .156

12 |

SPRS174M |

April 2001 − Revised October 2005 |

Features

1 Features

DHigh-Performance Static CMOS Technology

−150 MHz (6.67-ns Cycle Time)

−Low-Power (1.8-V Core @135 MHz, 1.9-V Core @150 MHz, 3.3-V I/O) Design

DJTAG Boundary Scan Support†

DHigh-Performance 32-Bit CPU (TMS320C28x)

−16 x 16 and 32 x 32 MAC Operations

−16 x 16 Dual MAC

−Harvard Bus Architecture

−Atomic Operations

−Fast Interrupt Response and Processing

−Unified Memory Programming Model

−4M Linear Program/Data Address Reach

−Code-Efficient (in C/C++ and Assembly)

−TMS320F24x/LF240x Processor Source Code Compatible

DOn-Chip Memory

−Flash Devices: Up to 128K x 16 Flash (Four 8K x 16 and Six 16K x 16 Sectors)

−ROM Devices: Up to 128K x 16 ROM

−1K x 16 OTP ROM

−L0 and L1: 2 Blocks of 4K x 16 Each Single-Access RAM (SARAM)

−H0: 1 Block of 8K x 16 SARAM

−M0 and M1: 2 Blocks of 1K x 16 Each SARAM

DBoot ROM (4K x 16)

−With Software Boot Modes

−Standard Math Tables

DExternal Interface (2812)

−Up to 1M Total Memory

−Programmable Wait States

−Programmable Read/Write Strobe Timing

−Three Individual Chip Selects

DClock and System Control

−Dynamic PLL Ratio Changes Supported

−On-Chip Oscillator

−Watchdog Timer Module

DThree External Interrupts

DPeripheral Interrupt Expansion (PIE) Block That Supports 45 Peripheral Interrupts

DThree 32-Bit CPU-Timers

D128-Bit Security Key/Lock

−Protects Flash/ROM/OTP and L0/L1 SARAM

−Prevents Firmware Reverse Engineering

DMotor Control Peripherals

−Two Event Managers (EVA, EVB)

−Compatible to 240xA Devices

DSerial Port Peripherals

−Serial Peripheral Interface (SPI)

−Two Serial Communications Interfaces (SCIs), Standard UART

−Enhanced Controller Area Network (eCAN)

−Multichannel Buffered Serial Port (McBSP)

D12-Bit ADC, 16 Channels

−2 x 8 Channel Input Multiplexer

−Two Sample-and-Hold

−Single/Simultaneous Conversions

−Fast Conversion Rate: 80 ns/12.5 MSPS

DUp to 56 General Purpose I/O (GPIO) Pins

DAdvanced Emulation Features

−Analysis and Breakpoint Functions

−Real-Time Debug via Hardware

DDevelopment Tools Include

−ANSI C/C++ Compiler/Assembler/Linker

−Code Composer Studio IDE

−DSP/BIOS

−JTAG Scan Controllers †

DLow-Power Modes and Power Savings

−IDLE, STANDBY, HALT Modes Supported

−Disable Individual Peripheral Clocks

DPackage Options

−179-Ball MicroStar BGA With External

Memory Interface (GHH), (ZHH) (2812)

−176-Pin Low-Profile Quad Flatpack (LQFP) With External Memory Interface (PGF) (2812)

−128-Pin LQFP Without External Memory Interface (PBK) (2810, 2811)

DTemperature Options:

−A: −40 °C to 85°C (GHH, ZHH, PGF, PBK)

−S/Q: −40 °C to 125°C (GHH, ZHH, PGF,

PBK)

TMS320C24x, Code Composer Studio, DSP/BIOS, and MicroStar BGA are trademarks of Texas Instruments.

†IEEE Standard 1149.1−1990, IEEE Standard Test-Access Port

April 2001 − Revised October 2005 |

SPRS174M |

13 |

Introduction

2 Introduction

This section provides a summary of each device’s features, lists the pin assignments, and describes the function of each pin. This document also provides detailed descriptions of peripherals, electrical specifications, parameter measurement information, and mechanical data about the available packaging.

2.1Description

The TMS320F2810, TMS320F2811, TMS320F2812, TMS320C2810, TMS320C2811, and TMS320C2812 devices, members of the TMS320C28x DSP generation, are highly integrated, high-performance solutions for demanding control applications. The functional blocks and the memory maps are described in Section 3, Functional Overview.

Throughout this document, TMS320F2810, TMS320F2811, and TMS320F2812 are abbreviated as F2810, F2811, and F2812, respectively. F281x denotes all three Flash devices. TMS320C2810, TMS320C2811, and TMS320C2812 are abbreviated as C2810, C2811, and C2812, respectively. C281x denotes all three ROM devices. 2810 denotes both F2810 and C2810 devices; 2811 denotes both F2811 and C2811 devices; and 2812 denotes both F2812 and C2812 devices.

TMS320C28x is a trademark of Texas Instruments.

All trademarks are the property of their respective owners.

14 |

SPRS174M |

April 2001 − Revised October 2005 |

Introduction

2.2Device Summary

Table 2−1 provides a summary of each device’s features.

Table 2−1. Hardware Features †

|

FEATURE |

|

F2810 |

F2811 |

F2812 |

C2810 |

C2811 |

C2812 |

||

|

|

|

|

|

|

|

|

|

||

Instruction Cycle (at 150 MHz) |

|

6.67 ns |

6.67 ns |

6.67 ns |

6.67 ns |

6.67 ns |

6.67 ns |

|||

|

|

|

|

|

|

|

|

|

||

Single-Access RAM (SARAM) |

|

18K |

18K |

18K |

18K |

18K |

18K |

|||

(16-bit word) |

|

|||||||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||

3.3-V On-Chip Flash (16-bit word) |

|

64K |

128K |

128K |

— |

— |

— |

|||

|

|

|

|

|

|

|

|

|

||

On-Chip ROM (16-bit word) |

|

— |

— |

— |

64K |

128K |

128K |

|||

|

|

|

|

|

|

|

|

|

||

Code Security for |

|

Yes |

Yes |

Yes |

Yes |

Yes |

Yes |

|||

On-Chip Flash/SARAM/OTP/ROM |

|

|||||||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||

Boot ROM |

|

Yes |

Yes |

Yes |

Yes |

Yes |

Yes |

|||

|

|

|

|

|

|

|

|

|

||

OTP ROM (1K X 16) |

|

Yes |

Yes |

Yes |

Yes‡ |

Yes‡ |

Yes‡ |

|||

External Memory Interface |

|

— |

— |

Yes |

— |

— |

Yes |

|||

|

|

|

|

|

|

|

|

|

||

Event Managers A and B |

|

EVA, EVB |

EVA, EVB |

EVA, EVB |

EVA, EVB |

EVA, EVB |

EVA, EVB |

|||

(EVA and EVB) |

|

|||||||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

||

S |

General-Purpose (GP) Timers |

4 |

4 |

4 |

4 |

4 |

4 |

|||

|

|

|

|

|

|

|

|

|

|

|

S |

Compare (CMP)/PWM |

|

16 |

16 |

16 |

16 |

16 |

16 |

||

|

|

|

|

|

|

|

|

|

||

S |

Capture (CAP)/QEP Channels |

6/2 |

6/2 |

6/2 |

6/2 |

6/2 |

6/2 |

|||

|

|

|

|

|

|

|

|

|

||

Watchdog Timer |

|

Yes |

Yes |

Yes |

Yes |

Yes |

Yes |

|||

|

|

|

|

|

|

|

|

|

||

12-Bit ADC |

|

Yes |

Yes |

Yes |

Yes |

Yes |

Yes |

|||

|

|

|

|

|

|

|

|

|

|

|

S |

Channels |

|

16 |

16 |

16 |

16 |

16 |

16 |

||

|

|

|

|

|

|

|

|

|

||

32-Bit CPU Timers |

|

3 |

3 |

3 |

3 |

3 |

3 |

|||

|

|

|

|

|

|

|

|

|

|

|

SPI |

|

|

|

Yes |

Yes |

Yes |

Yes |

Yes |

Yes |

|

|

|

|

|

|

|

|

|

|

||

SCIA, SCIB |

|

SCIA, SCIB |

SCIA, SCIB |

SCIA, SCIB |

SCIA, SCIB |

SCIA, SCIB |

SCIA, SCIB |

|||

|

|

|

|

|

|

|

|

|

|

|

CAN |

|

|

|

Yes |

Yes |

Yes |

Yes |

Yes |

Yes |

|

|

|

|

|

|

|

|

|

|

|

|

McBSP |

|

|

|

Yes |

Yes |

Yes |

Yes |

Yes |

Yes |

|

|

|

|

|

|

|

|

|

|

||

Digital I/O Pins (Shared) |

|

56 |

56 |

56 |

56 |

56 |

56 |

|||

|

|

|

|

|

|

|

|

|

||

External Interrupts |

|

3 |

3 |

3 |

3 |

3 |

3 |

|||

|

|

|

|

|

|

|

|

|

||

Supply Voltage |

|

|

1.8-V Core, (135 MHz) 1.9-V Core (150 MHz), 3.3-V I/O |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

179-ball GHH |

|

|

179-ball GHH |

|

Packaging |

|

128-pin PBK |

128-pin PBK |

and ZHH |

128-pin PBK |

128-pin PBK |

and ZHH |

|||

|

|

|

|

|

|

176-pin PGF |

|

|

176-pin PGF |

|

|

|

|

|

|

|

|

|

|

||

|

|

A: −40 °C to |

Yes |

Yes |

Yes |

Yes |

Yes |

Yes |

||

|

|

85°C |

|

|||||||

Temperature Options |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|||

S/Q: −40 |

°C to |

Yes |

Yes |

Yes |

Yes |

Yes |

Yes |

|||

|

|

|||||||||

|

|

125°C |

|

|||||||

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

||

Product Status§ |

|

|

TMS |

TMS |

TMS |

TMS |

TMS |

TMS |

||

†The TMS320F2810, TMS320F2811, TMS320F2812, TMS320C2810, TMS320C2811, TMS320C2812 Digital Signal Processors Silicon Errata

(literature number SPRZ193) has been posted on the Texas Instruments (TI) website. It will be updated as needed.

‡ On C281x devices, OTP is replaced by a 1K X 16 block of ROM.

§ See Section 5.1, Device and Development Support Nomenclature for descriptions of device stages.

April 2001 − Revised October 2005 |

SPRS174M |

15 |

Introduction

2.3Pin Assignments

Figure 2−1 illustrates the ball locations for the 179-ball GHH and ZHH ball grid array (BGA) package. Figure 2−2 shows the pin assignments for the 176-pin PGF low-profile quad flatpack (LQFP) and Figure 2−3 shows the pin assignments for the 128-pin PBK LQFP. Table 2−2 describes the function(s) of each pin.

2.3.1Terminal Assignments for the GHH Package

See Table 2−2 for a description of each terminal’s function(s).

P |

XZCS0AND1 PWM8 |

PWM10 |

VSS |

VDD |

CAP6 |

XD[8] |

VSS |

VDD |

T3CTRIP |

T4CTRIP/ |

VDD |

XZCS2 |

SCITXDB |

||

_QEPI2 |

_PDPINTB EVBSOC |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||

N |

SPISOMIA |

PWM7 |

PWM9 |

XR/W |

T4PWM |

C4TRIP |

TEST2 |

VDD3VFL |

XD[11] |

XA[2] |

XWE |

CANTXA |

CANRXA |

VDDIO |

|

_T4CMP |

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

M |

SPISIMOA |

XA[1] |

XRD |

PWM12 |

CAP4 |

CAP5 |

TEST1 |

XD[9] |

X2 |

VSS |

XA[3] |

PWM1 |

SCIRXDB |

PWM2 |

|

_QEP3 |

_QEP4 |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

L |

VDD |

VSS |

XD[6] |

PWM11 |

XD[7] |

C5TRIP |

VDDIO |

TDIRB |

XD[10] |

VDDIO |

VSS |

PWM3 |

PWM4 |

XD[12] |

|

K |

VSS |

SPICLKA |

XD[4] |

SPISTEA |

T3PWM |

VSS |

C6TRIP |

TCLKINB |

X1/ |

XHOLDA |

PWM5 |

VDD |

VSS |

PWM6 |

|

_T3CMP |

XCLKIN |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

J |

MCLKXA |

MFSRA |

XD[3] |

VDDIO |

XD[5] |

|

|

|

|

XD[13] |

T1PWM |

XA[4] |

T2PWM |

VSS |

|

|

|

|

|

_T1CMP |

_T2CMP |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

H |

VDD |

MCLKRA |

XD[1] |

MFSXA |

XD[2] |

|

|

|

|

CAP1 |

CAP2 |

CAP3 |

XA[5] |

T1CTRIP |

|

|

|

|

|

_QEP1 _QEP2 _QEPI1 |

_PDPINTA |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|||||

G |

MDXA |

MDRA |

XD[0] |

VSS |

XA[0] |

|

|

|

|

T2CTRIP/ |

VDDIO |

VDD |

VSS |

XA[6] |

|

|

|

|

|

EVASOC |

|||||||||||

F |

XMP/MC |

ADC- |

VSSA1 |

VDDA1 |

ADCINB7 |

|

|

|

|

C3TRIP |

XCLKOUT |

XA[7] |

TCLKINA |

TDIRA |

|

RESEXT |

|

|

|

|

|||||||||||

E |

AVDD- |

ADCREFP |

AVSS- |

ADCREFM ADCINA5 |

ADC- |

XHOLD |

XNMI |

VDDIO |

XA[13] |

C2TRIP |

XA[8] |

C1TRIP |

VSS |

||

REFBG |

REFBG |

BGREFIN |

_XINT13 |

||||||||||||

D |

ADCINB6 ADCINB5 ADCINB4 ADCINA1 ADCINA6 |

XRS |

XA[18] |

XINT2 |

XINT1 |

VSS |

EMU0 |

TDO |

TMS |

XA[9] |

|||||

_ADCSOC |

_XBIO |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

C |

ADCINB3 ADCINB0 ADCINB1 ADCINA2 |

VSSA2 |

VSS1 |

SCITXDA |

VDD |

EMU1 |

VSS |

XA[12] |

XA[10] |

TDI |

VDD |

||||

B |

ADCINB2 |

VDDAIO |

ADCLO |

ADCINA3 ADCINA7 |

XREADY |

XA[17] |

VSS |

XA[15] |

VDD |

XD[14] |

TRST |

XZCS6AND7 VSS |

|||

A |

|

VSSAIO |

ADCINA0 ADCINA4 |

VDDA2 |

VDD1 |

SCIRXDA |

XA[16] |

XD[15] |

XA[14] |

XF |

TCK |

TESTSEL |

XA[11] |

||

|

_XPLLDIS |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

11 |

12 |

13 |

14 |

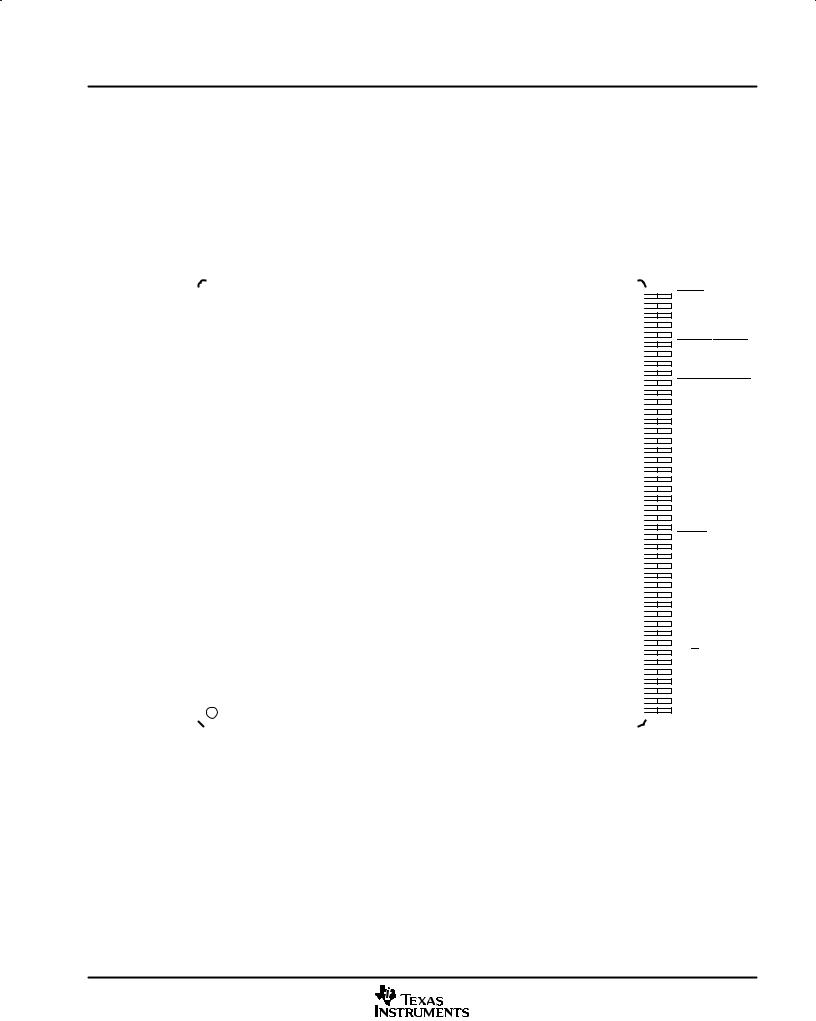

Figure 2−1. TMS320F2812 and TMS320C2812 179-Ball GHH MicroStar BGA (Bottom View)

16 |

SPRS174M |

April 2001 − Revised October 2005 |

Introduction

2.3.2Pin Assignments for the PGF Package

The TMS320F2812 and TMS320C2812 176-pin PGF low-profile quad flatpack (LQFP) pin assignments are shown in Figure 2−2. See Table 2−2 for a description of each pin’s function(s).

|

|

|

|

|

|

|

|

|

|

XA[11] |

TDI |

XA[10] |

V |

V |

TDO |

TMS |

XA[9] |

|

C3TRIP |

|

C1TRIP |

XA[8] |

V |

XCLKOUT |

|

XA[7] |

TCLKINA |

TDIRA |

|

T2CTRIP/ EVASOC |

V |

V |

V |

XA[6] |

T1CTRIPPDPINTA |

CAP3QEPI1 |

XA[5] |

CAP2QEP2 |

CAP1QEP1 |

V |

T2PWMT2CMP |

XA[4] |

T1PWMT1CMP |

PWM6 |

V |

V |

PWM5 |