Texas Instruments TMS320LC57SRBK80, TMS320LC57SRBK50, TMS320LC57SRBK, TMS320LC57SPJEA80, TMS320LC57SPJEA50 Datasheet

...

TMS320C5x, TMS320LC5x

DIGITAL SIGNAL PROCESSORS

SPRS030A ± APRIL 1995 ± REVISED APRIL 1996

DPowerful 16-Bit TMS320C5x CPU

D20-, 25-, 35-, and 50-ns Single-Cycle Instruction Execution Time for 5-V Operation

D25-, 40-, and 50-ns Single-Cycle Instruction Execution Time for 3-V Operation

DSingle-Cycle 16 × 16-Bit Multiply/Add

D224K × 16-Bit Maximum Addressable

External Memory Space (64K Program, 64K Data, 64K I/O, and 32K Global)

D2K, 4K, 8K, 16K, 32K × 16-Bit Single-Access

On-Chip Program ROM

D1K, 3K, 6K, 9K × 16-Bit Single-Access

On-Chip Program/Data RAM (SARAM)

D1K Dual-Access On-Chip Program/Data RAM (DARAM)

DFull-Duplex Synchronous Serial Port for Coder/Decoder Interface

DTime-Division-Multiplexed (TDM) Serial Port

DHardware or Software Wait-State Generation Capability

DOn-Chip Timer for Control Operations

DRepeat Instructions for Efficient Use of Program Space

DBuffered Serial Port

DHost Port Interface

DMultiple Phase-Locked Loop (PLL) Clocking Options (×1, ×2, ×3, ×4, ×5, ×9

Depending on Device)

DBlock Moves for Data/Program Management

DOn-Chip Scan-Based Emulation Logic

DBoundary Scan

DFive Packaging Options

±100-Pin Quad Flat Package (PJ Suffix)

±100-Pin Thin Quad Flat Package (PZ Suffix)

±128-Pin Thin Quad Flat Package (PBK Suffix)

±132-Pin Quad Flat Package (PQ Suffix)

±144-Pin Thin Quad Flat Package (PGE Suffix)

DLow Power Dissipation and Power-Down Modes:

±47 mA (2.35 mA/MIP) at 5 V, 40-MHz Clock (Average)

±23 mA (1.15 mA/MIP) at 3 V, 40-MHz Clock (Average)

±10 mA at 5 V, 40-MHz Clock (IDLE1 Mode)

±3 mA at 5 V, 40-MHz Clock (IDLE2 Mode)

±5 µA at 5 V, Clocks Off (IDLE2 Mode)

DHigh-Performance Static CMOS Technology

DIEEE Standard 1149.1² Test-Access Port (JTAG)

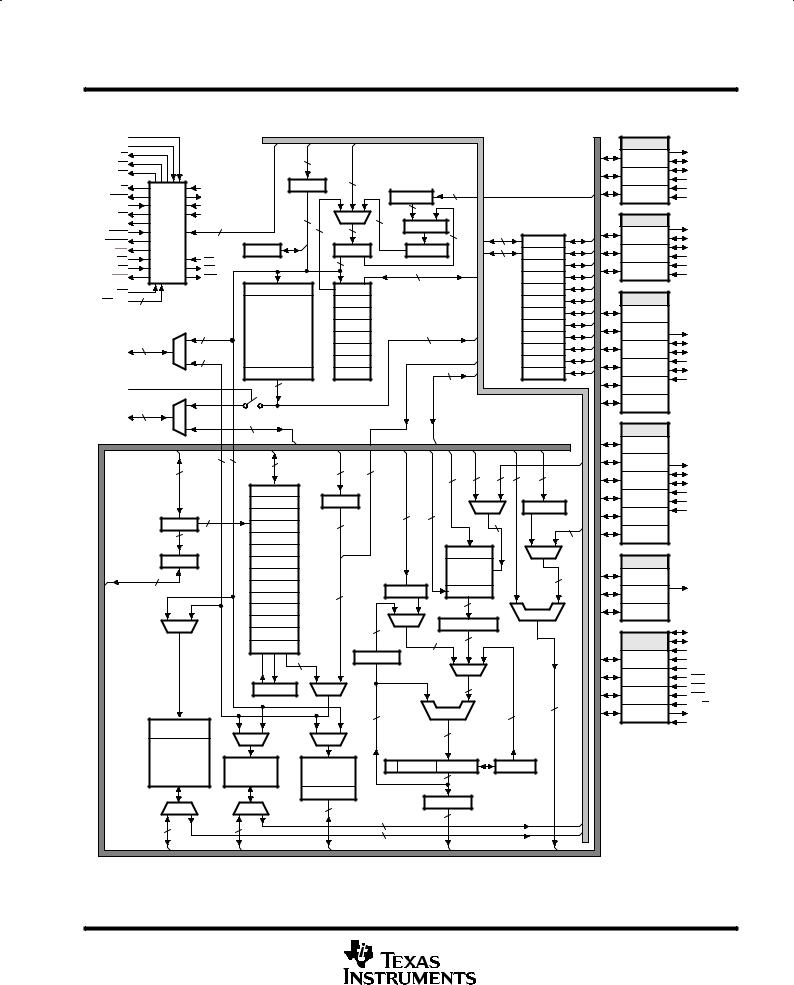

description

The TMS320C5x generation of the Texas Instruments (TI ) TMS320 digital signal processors (DSPs) is fabricated with static CMOS integrated circuit technology; the architectural design is based upon that of an earlier TI DSP, the TMS320C25. The combination of advanced Harvard architecture, on-chip peripherals, on-chip memory, and a highly specialized instruction set is the basis of the operational flexibility and speed of the 'C5x³ devices. They execute up to 50 million instructions per second (MIPS).

The 'C5x devices offer these advantages:

DEnhanced TMS320 architectural design for increased performance and versatility

DModular architectural design for fast development of spin-off devices

DAdvanced integrated-circuit processing technology for increased performance

DUpward-compatible source code (source code for 'C1x and 'C2x DSPs is upward compatible with 'C5x DSPs.)

DEnhanced TMS320 instruction set for faster algorithms and for optimized high-level language operation

DNew static-design techniques for minimizing power consumption and maximizing radiation tolerance

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TI is a trademark of Texas Instruments Incorporated.

² IEEE Standard 1149.1±1990, IEEE Standard Test-Access Port and Boundary-Scan Architecture

³ References to 'C5x in this document include both TMS320C5x and TMS320LC5x devices unless specified otherwise.

PRODUCTION DATA information is current as of publication date. |

Copyright 1996, Texas Instruments Incorporated |

Products conform to specifications per the terms of Texas Instruments |

|

standard warranty. Production processing does not necessarily include |

|

testing of all parameters. |

|

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

1 |

TMS320C5x, TMS320LC5x

DIGITAL SIGNAL PROCESSORS

SPRS030A ± APRIL 1995 ± REVISED APRIL 1996

description (continued)

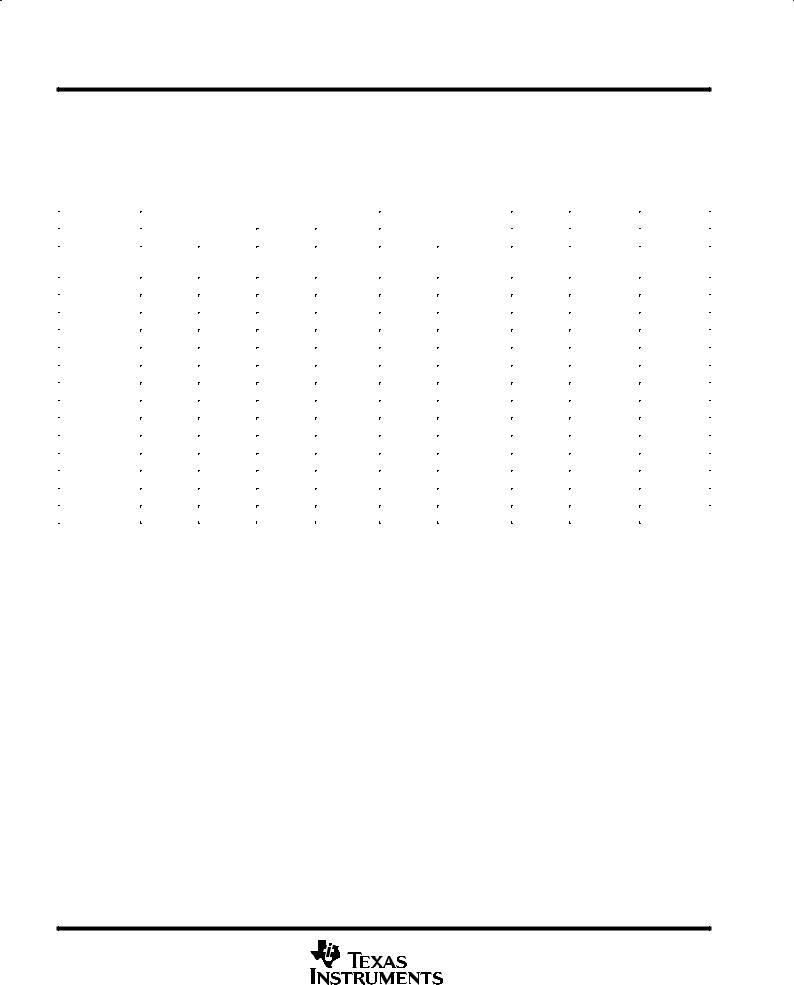

Table 1 provides a comparison of the devices in the 'C5x generation. It shows the capacity of on-chip RAM and ROM memories, number of serial and parallel I/O ports, execution time of one machine cycle, and type of package with total pin count.

Table 1. Characteristics of the 'C5x Processors

|

ON-CHIP MEMORY (16-BIT WORDS) |

I/O PORTS |

POWER |

CYCLE |

|

||||||

TMS320 |

|

|

|

|

|

PACKAGE |

|||||

|

DARAM |

SARAM |

ROM |

||||||||

|

|

|

SUPPLY |

TIME |

TYPE |

||||||

DEVICES |

|

|

|

|

|

|

|

||||

DATA |

DATA + |

DATA + |

PROG |

SERIAL |

² |

(V) |

(ns) |

QFP³ |

|||

|

|||||||||||

|

PROG |

PROG |

PARALLEL |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

TMS320C50 |

544 |

|

512 |

9K |

2K§ |

2 |

64K |

5 |

50/35/25 |

132 pin |

|

TMS320LC50 |

544 |

|

512 |

9K |

2K§ |

2 |

64K |

3.3 |

50/40/25 |

132 pin |

|

TMS320C51 |

544 |

|

512 |

1K |

8K§ |

2 |

64K |

5 |

50/35/25/20 |

100/132 pin |

|

TMS320LC51 |

544 |

|

512 |

1K |

8K§ |

2 |

64K |

3.3 |

50/40/25 |

100/132 pin |

|

TMS320C52 |

544 |

|

512 |

± |

4K§ |

1¶ |

64K |

5 |

50/35/25/20 |

100 pin |

|

TMS320LC52 |

544 |

|

512 |

± |

4K§ |

1¶ |

64K |

3.3 |

50/40/25 |

100 pin |

|

TMS320C53 |

544 |

|

512 |

3K |

16K§ |

2 |

64K |

5 |

50/35/25 |

132 pin |

|

TMS320LC53 |

544 |

|

512 |

3K |

16K§ |

2 |

64K |

3.3 |

50/40/25 |

132 pin |

|

TMS320C53S |

544 |

|

512 |

3K |

16K§ |

2 ¶ |

64K |

5 |

50/35/25 |

100 pin |

|

TMS320LC53S |

544 |

|

512 |

3K |

16K§ |

2 ¶ |

64K |

3.3 |

50/40/25 |

100 pin |

|

TMS320LC56 |

544 |

|

512 |

6K |

32K |

2 # |

64K |

3.3 |

35/25 |

100 pin |

|

TMS320LC57 |

544 |

|

512 |

6K |

32K |

2 # |

64K + HPI || |

3.3 |

35/25 |

128 pin |

|

TMS320C57S |

544 |

|

512 |

6K |

2K§ |

2 # |

64K + HPI || |

5 |

50/35/25 |

144 pin |

|

TMS320LC57S |

544 |

|

512 |

6K |

2K§ |

2 # |

64K + HPI || |

3.3 |

50/35 |

144 pin |

|

² Sixteen of the 64K parallel I/O ports are memory mapped. ³ QFP = Quad flatpack

§ ROM boot loader available

¶ TDM serial port not available

# Includes auto-buffered serial port (BSP) but TDM serial port not available || HPI = Host port interface

Pinouts for each package are device-specific.

2 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

TMS320C5x, TMS320LC5x

DIGITAL SIGNAL PROCESSORS

SPRS030A ± APRIL 1995 ± REVISED APRIL 1996

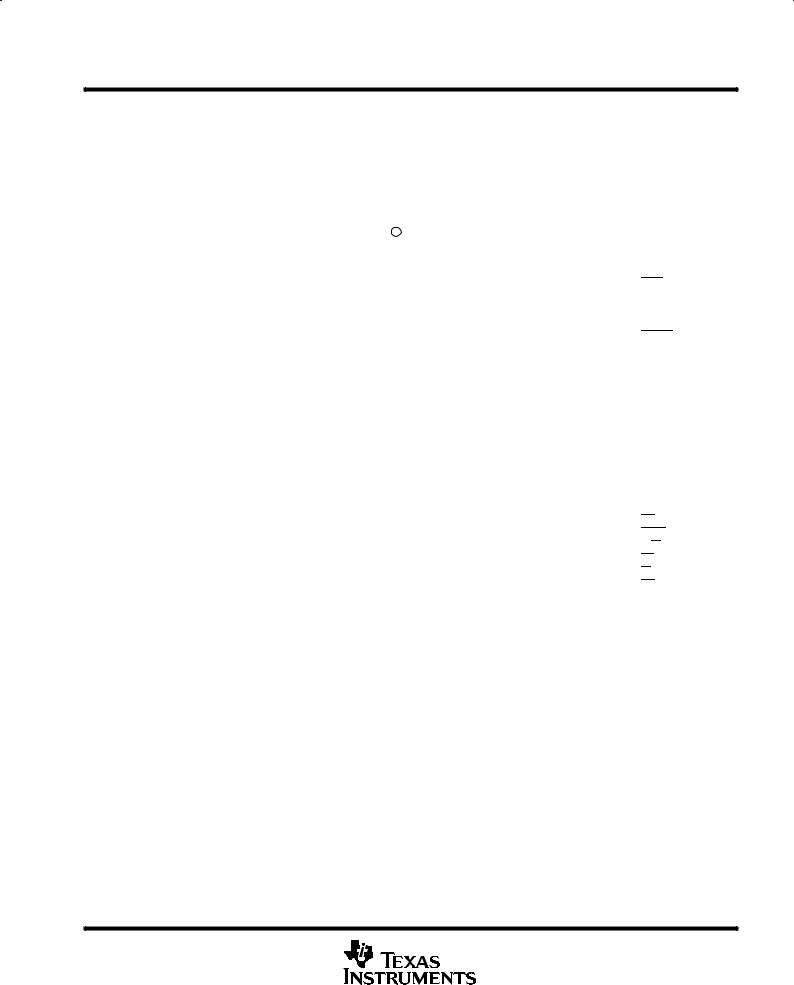

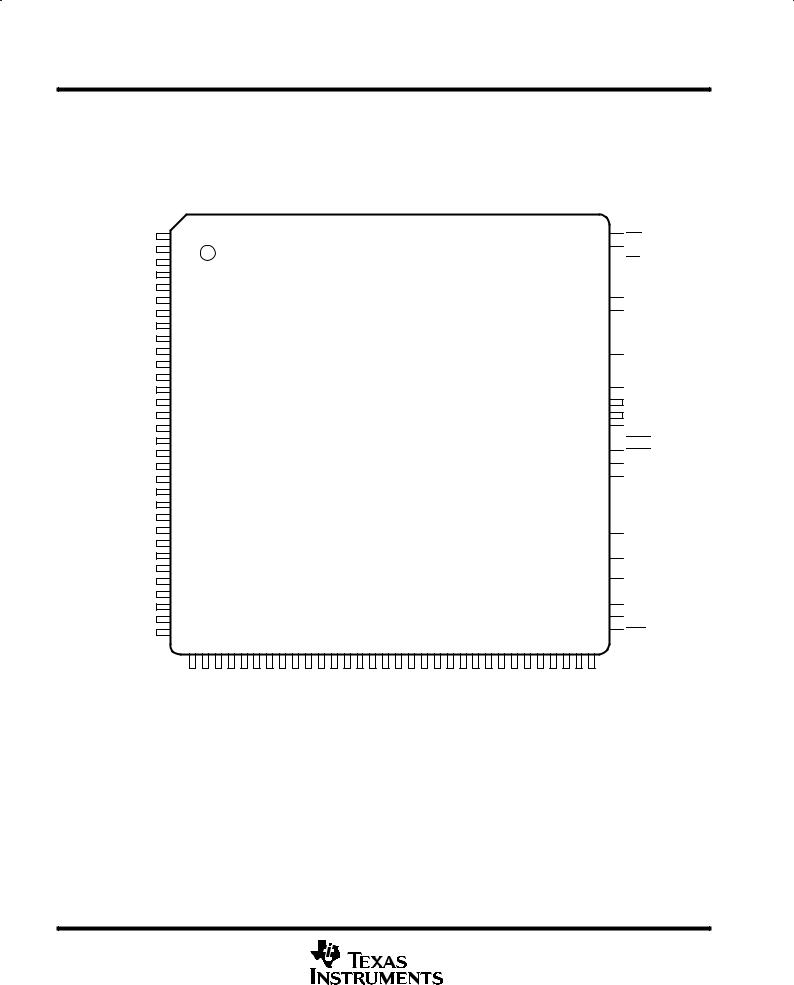

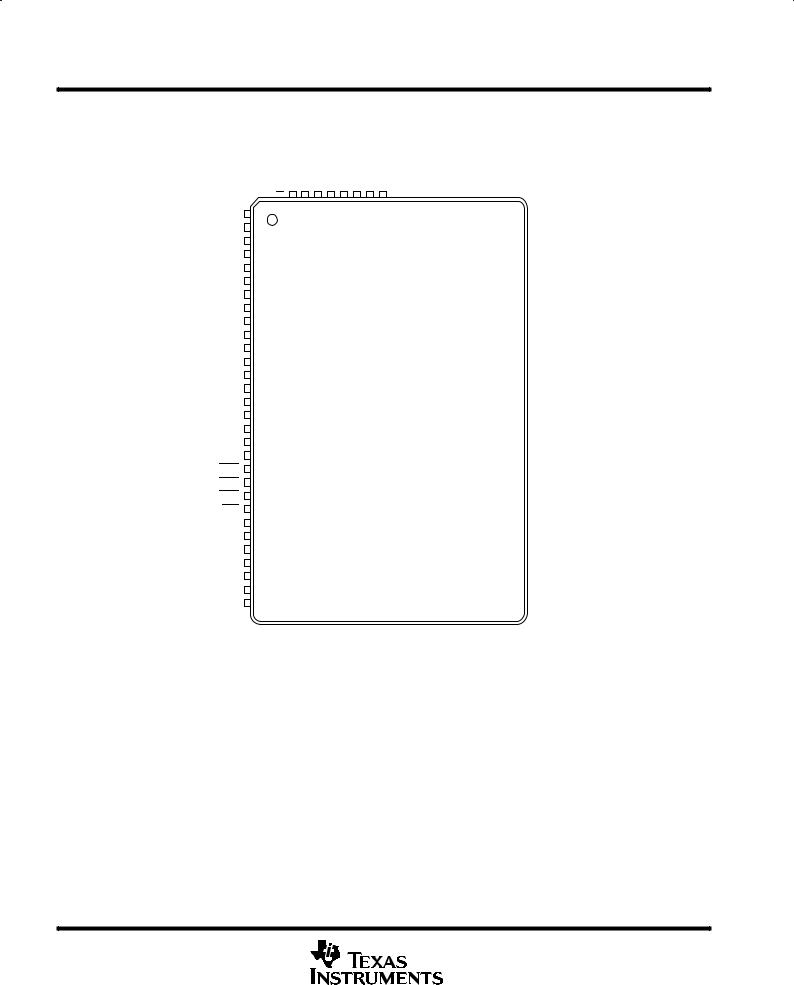

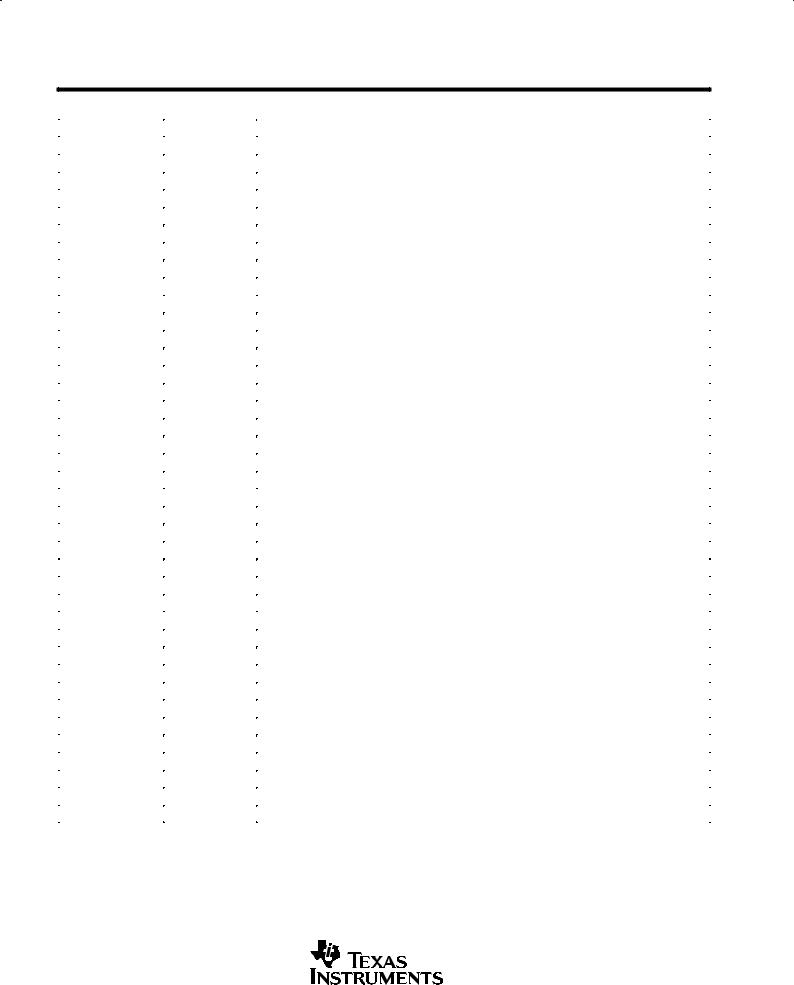

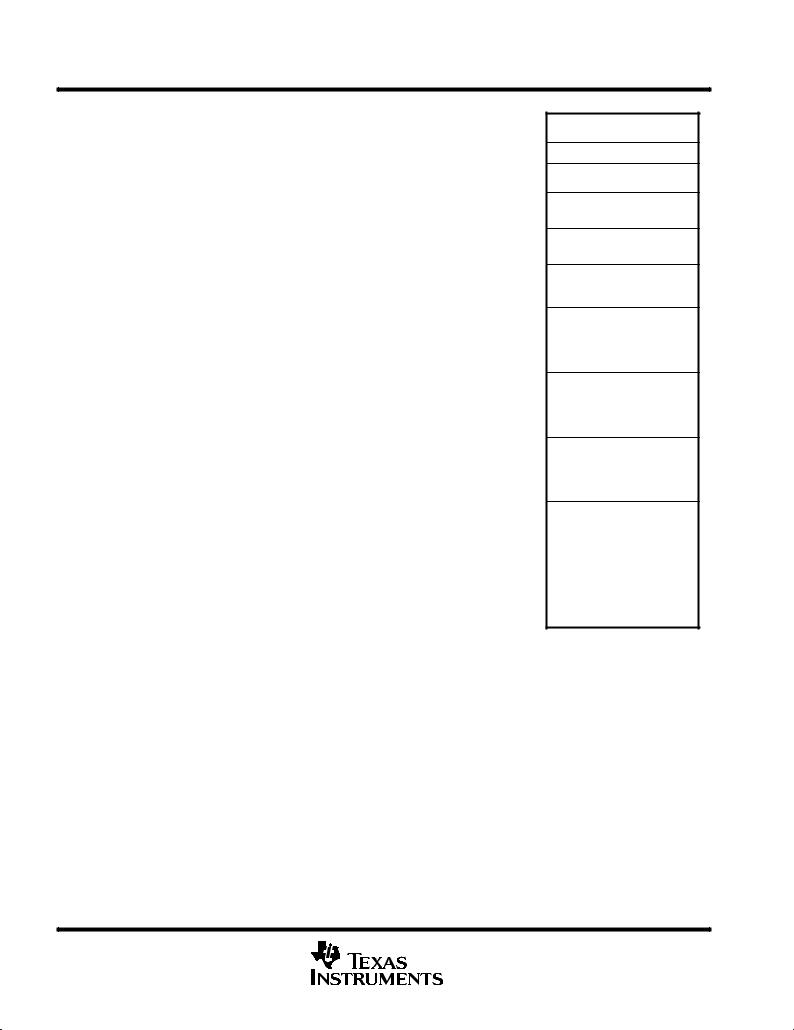

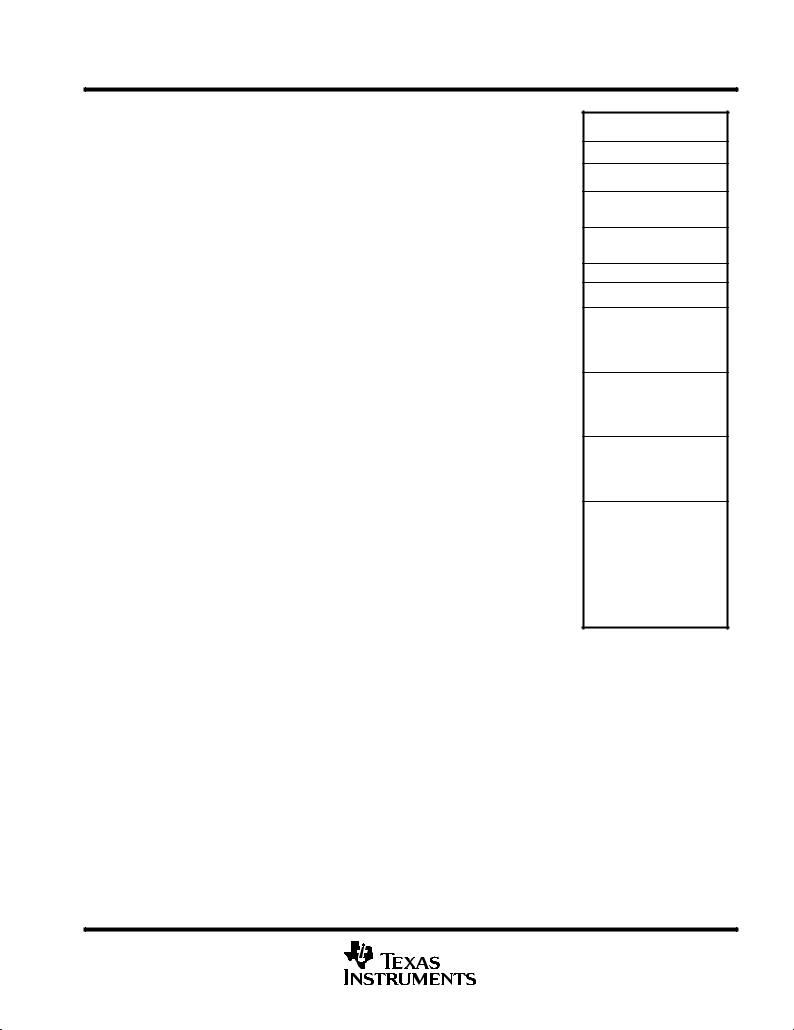

TMS320C50, TMS320LC50, TMS320C51, TMS320LC51, TMS320C53, TMS320LC53

PQ PACKAGE

( TOP VIEW )

|

|

|

|

|

|

NC |

|

NC |

|

V |

|

V |

|

D8 |

|

D9 |

|

D10 |

|

D11 |

|

D12 |

|

D13 |

|

D14 |

|

D15 |

|

MCMP/ |

|

V |

|

V |

|

TRST |

|

IAQ |

|

V |

V |

|

BIO |

|

HOLD |

|

READY |

|

RS |

|

TCLKR |

|

/TFSRTADD |

|

CLKX |

|

TCLKX |

|

TOUT |

|

V |

|

V |

|

EMU1/OFF |

|

EMU0 |

NC |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

DDD |

|

DDD |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SSI |

|

SSI |

|

|

|

|

|

DDC |

DDC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SSC |

|

SSC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

132 131 130 129 128 127 126 125 124 123 122 121 120 119 118 117 |

|

|

||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

|

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

116 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

NC |

|

19 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

115 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

VSSD |

|

20 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

114 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VSSD |

|

21 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

113 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

NC |

|

22 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

112 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

D7 |

|

23 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

111 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

D6 |

|

24 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

110 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

D5 |

|

25 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

109 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

D4 |

|

26 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

108 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

D3 |

|

27 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

107 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

D2 |

|

28 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

106 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

D1 |

|

29 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

105 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

D0 |

|

30 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

104 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

TMS |

|

31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

103 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

VDDD |

|

32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

102 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VDDD |

|

33 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

101 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

TCK |

|

34 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

100 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

VSSD |

|

35 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

99 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VSSD |

|

36 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

98 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

NC |

|

37 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

97 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INT1 |

|

|

|

38 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

96 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INT2 |

|

|

|

39 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

95 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INT3 |

|

|

|

40 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

94 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

INT4 |

|

|

|

41 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

93 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

NMI |

|

|

42 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

92 |

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

DR |

|

43 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

91 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

TDR |

|

44 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

90 |

|

|||

|

FSR |

|

45 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

89 |

|

|||

CLKR |

|

46 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

88 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VDDA |

|

47 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

87 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

VDDA |

|

48 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

86 |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

NC |

|

49 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

85 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

NC |

|

50 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

84 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

51 |

52 |

53 |

54 |

55 |

56 |

57 |

58 |

59 |

60 |

61 |

62 |

63 |

64 |

65 |

66 |

67 |

68 |

|

69 |

70 |

71 |

72 |

73 |

74 |

75 |

76 |

77 |

78 |

79 |

80 |

81 |

82 |

|

83 |

|

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC |

|

NC |

|

V |

|

V |

|

A0 |

|

A1 |

|

A2 |

|

A3 |

|

A4 |

|

A5 |

|

A6 |

|

A7 |

|

A8 |

|

A9 |

|

V |

|

V |

|

TDI |

|

V |

V |

|

NC |

|

CLKMD1 |

|

A10 |

|

A11 |

|

A12 |

|

A13 |

|

A14 |

|

A15 |

|

NC |

|

NC |

|

V |

|

V |

|

RD |

WE |

|

|||

|

|

|

|

|

|

|

|

|

|

SSA |

|

SSA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DDI |

|

DDI |

|

|

|

SSA |

SSA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DDA |

|

DDA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

NC

NC

VDDI

VDDI

IACK

NC CLKOUT1 XF

HOLDA

TDX

DX

TFSX / TFRM FSX CLKMD2 VSSI

VSSI

TDO

VDDC

VDDC

X1

X2 / CLKIN CLKIN2

BR

STRB

R/ W

PS

IS

DS

NC

VSSC

VSSC

NC

NC

NOTE: NC = No connect (These pins are reserved.)

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

3 |

TMS320C5x, TMS320LC5x

DIGITAL SIGNAL PROCESSORS

SPRS030A ± APRIL 1995 ± REVISED APRIL 1996

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

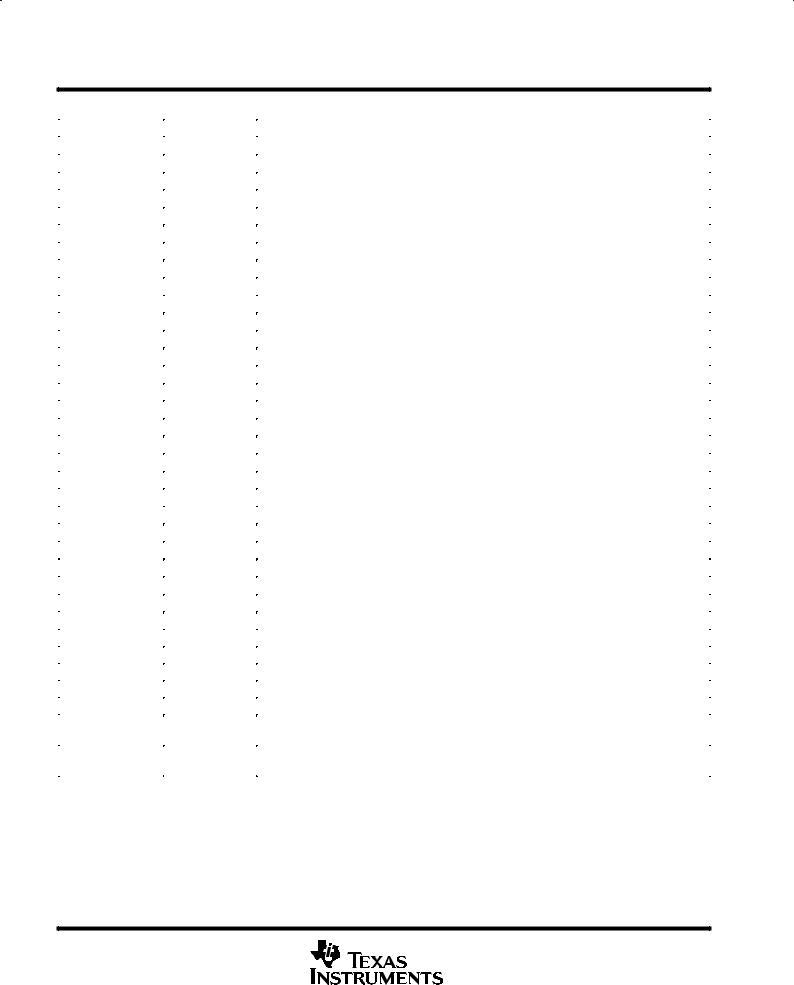

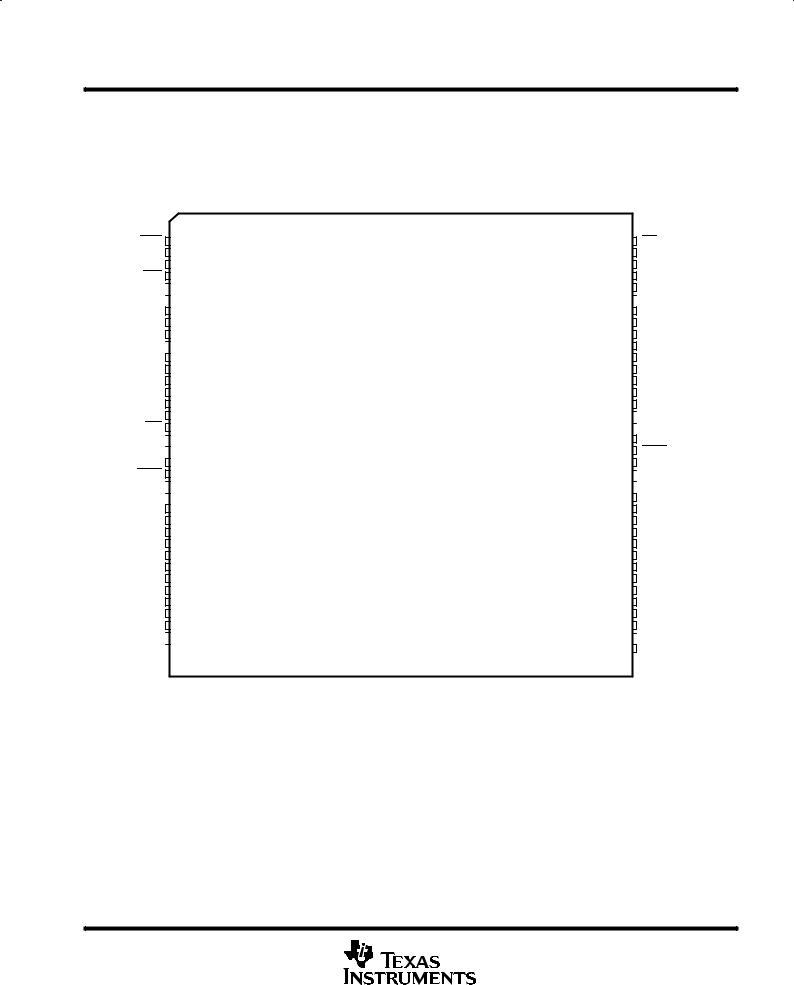

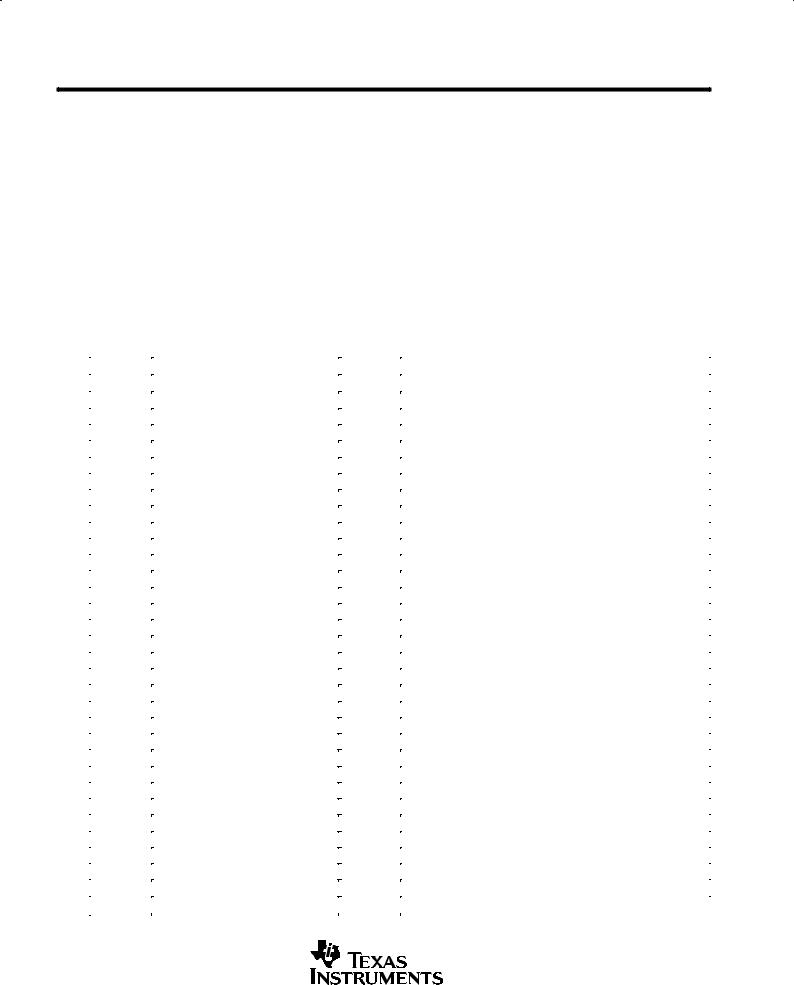

Pin Functions for Devices in the PQ Package |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SIGNAL |

|

TYPE |

|

DESCRIPTION |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PARALLEL INTERFACE BUS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A0 ± A15 |

|

I / O / Z |

|

16-bit external address bus (MSB: A15, LSB: A0) |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

D0 ± D15 |

|

I / O / Z |

|

16-bit external data bus (MSB: D15, LSB: D0) |

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

O / Z |

|

Program, data, and I /O space select outputs, respectively |

|

PS, |

|

|

|

|

|

|

DS, |

|

|

|

|

IS |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I / O / Z |

|

Timing strobe for external cycles and external DMA |

|

STRB |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

R / |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I / O / Z |

|

Read/ write select for external cycles and external DMA |

|

W |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

O / Z |

|

Read and write strobes, respectively, for external cycles |

|

RD, |

|

|

|

|

|

WE |

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

READY |

|

|

|

|

|

I |

|

External bus ready/ wait-state control input |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I / O / Z |

|

Bus request. Arbitrates global memory and external DMA |

|

BR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SYSTEM INTERFACE / CONTROL SIGNALS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

RS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

Reset. Initializes device and sets PC to zero |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

Microprocessor/microcomputer mode select. Enables internal ROM |

|

MP/MC |

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

Puts parallel I/ F bus in high-impedance state after current cycle |

|

HOLD |

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

O / Z |

|

Hold acknowledge. Indicates external bus in hold state |

|

HOLDA |

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

XF |

|

|

|

|

|

O / Z |

|

External flag output. Set /cleared through software |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

I /O branch input. Implements conditional branches |

|

BIO |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

TOUT |

|

|

|

|

|

O / Z |

|

Timer output signal. Indicates output of internal timer |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

O / Z |

|

Instruction acquisition signal |

|

IAQ |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

O / Z |

|

Interrupt acknowledge signal |

|

IACK |

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

± |

|

|

|

|

|

|

|

|

|

I |

|

External interrupt inputs |

||||

|

INT1 |

INT4 |

|

|

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

Nonmaskable external interrupt |

|

NMI |

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SERIAL PORT INTERFACE (SPI) |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

DR |

|

|

|

|

|

I |

|

Serial receive-data input |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

DX |

|

|

|

|

|

O / Z |

|

Serial transmit-data output. In high-impedance state when not transmitting |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

CLKR |

|

|

|

|

|

I |

|

Serial receive-data clock input |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

CLKX |

|

|

|

|

|

I / O / Z |

|

Serial transmit-data clock. Internal or external source |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

FSR |

|

|

|

|

|

I |

|

Serial receive-frame-synchronization input |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

FSX |

|

|

|

|

|

I / O / Z |

|

Serial transmit-frame-synchronization signal. Internal or external source |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TDM SERIAL-PORT INTERFACE |

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

TDR |

|

|

|

|

|

I |

|

TDM serial receive-data input |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

TDX |

|

|

|

|

|

O / Z |

|

TDM serial transmit-data output. In high-impedance state when not transmitting |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

TCLKR |

|

|

|

|

|

I |

|

TDM serial receive-data clock input |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

TCLKX |

|

|

|

|

|

I / O / Z |

|

TDM serial transmit-data clock. Internal or external source |

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TFSR / TADD |

|

I / O / Z |

|

TDM serial receive-frame-synchronization input. In the TDM mode, TFSR / TADD is used to output / |

||||||||||||||||||||||

|

|

|

input the address of the port. |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TFSX / TFRM |

|

I |

|

TDM serial transmit-frame-synchronization signal. Internal or external source. In the TDM mode, |

||||||||||||||||||||||

|

|

|

TFSX / TFRM becomes TFRM, the TDM frame synchronization. |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LEGEND: |

|

|

|

||||||||||||||||||||||||

|

I = |

Input |

|

|

|

||||||||||||||||||||||

|

O = |

Output |

|

|

|

||||||||||||||||||||||

|

Z = |

High impedance |

|

|

|

||||||||||||||||||||||

4 |

POST OFFICE BOX 1443 •HOUSTON, TEXAS 77251±1443 |

TMS320C5x, TMS320LC5x

DIGITAL SIGNAL PROCESSORS

SPRS030A ± APRIL 1995 ± REVISED APRIL 1996

|

|

|