Texas Instruments TPS3707-50DR, TPS3707-50DGNR, TPS3707-25DGNR, TPS3707-25DGN, TPS3707-25D Datasheet

...

TPS3705-30, TPS3705-33, TPS3705-50 TPS3707-25, TPS3707-30, TPS3707-33, TPS3707-50 PROCESSOR SUPERVISORY CIRCUITS WITH POWER-FAIL

SLVS184B ± NOVEMBER 1998 ± REVISED JANUARY 1999

features

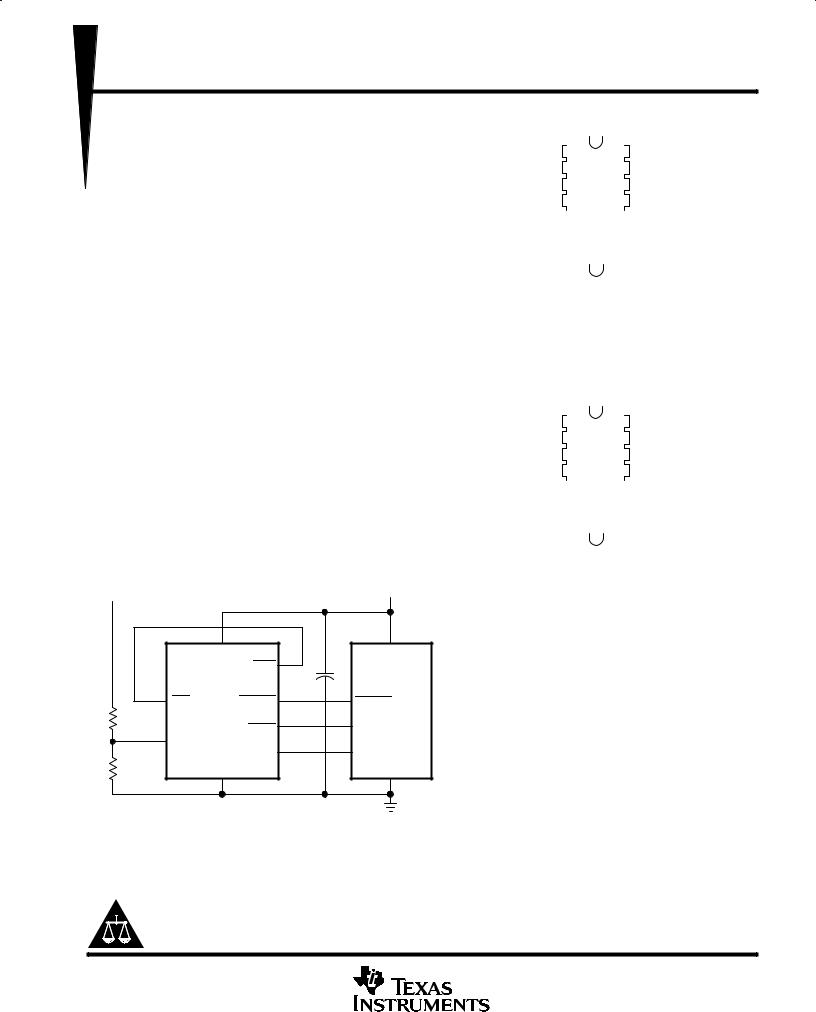

TPS3705 . . . D PACKAGE

(TOP VIEW)

DPower-On Reset Generator with Fixed Delay Time of 200 ms, no External Capacitor Needed

DPrecision Supply Voltage Monitor 2.5 V, 3 V, 3.3 V, and 5 V

DPin-For-Pin Compatible with the MAX705 through MAX708 Series

DIntegrated Watchdog Timer (TPS3705 only)

DVoltage Monitor for Power-Fail or Low-Battery Warning

DMaximum Supply Current of 50 μA

DMSOP-8 and SO-8 Packages

DTemperature Range . . . ±40°C to 85°C

typical applications

DDesigns Using DSPs, Microcontrollers or Microprocessors

DIndustrial Equipment

DProgrammable Controls

DAutomotive Systems

DPortable/Battery Powered Equipment

DIntelligent Instruments

DWireless Communication Systems

DNotebook/Desktop Computers

12 V |

5 V |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MR |

1 |

8 |

|

WDO |

|||||||

VDD |

2 |

7 |

|

RESET |

|

|||||||

GND |

3 |

6 |

|

WDI |

||||||||

|

PFI |

|

|

|

|

|

||||||

|

4 |

5 |

|

PFO |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

TPS3707 . . . D PACKAGE |

||||||||||||

|

|

|

|

|

(TOP VIEW) |

|

|

|

|

|

||

|

|

|

|

|

|

|

RESET |

|||||

|

|

|

|

|

||||||||

|

MR |

|

|

1 |

8 |

|

||||||

|

||||||||||||

VDD |

|

|

|

|

|

|

|

|

|

|||

|

2 |

7 |

|

RESET |

||||||||

GND |

|

3 |

6 |

|

NC |

|||||||

|

|

|||||||||||

PFI |

|

|

|

|

|

|

|

|

|

|||

|

4 |

5 |

|

PFO |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC ± No internal connection

TPS3705 . . . DGN PACKAGE

(TOP VIEW)

|

|

|

|

|

|

|

|

|

|

|

|

|

RESET |

1 |

8 |

WDI |

|||||||||

|

WDO |

|

|

2 |

7 |

|

PFO |

|

|

|||

|

|

MR |

|

|

3 |

6 |

PFI |

|||||

|

VDD |

4 |

5 |

GND |

||||||||

TPS3707 . . . DGN PACKAGE |

||||||||||||

|

|

|

|

|

|

|

(TOP VIEW) |

|

|

|

|

|

|

|

|

|

|

|

|

NC |

|||||

|

|

|

|

|

|

|||||||

RESET |

|

|

1 |

8 |

|

|||||||

|

||||||||||||

RESET |

|

|

|

|

|

|

|

|||||

|

2 |

7 |

|

PFO |

|

|||||||

|

|

|

|

|

|

|

|

PFI |

||||

|

|

MR |

|

3 |

6 |

|

||||||

|

VDD |

|

4 |

5 |

|

GND |

||||||

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

NC ± No internal connection

|

VDD |

VDD |

|

PFO |

|

|

TPS3705±50 |

MSP430P112 |

|

|

100 nF |

MR |

RESET |

RESET/NMI |

910 kΩ |

WDO |

I/O |

|

||

PFI |

WDI |

I/O |

|

||

120 kΩ |

GND |

GND |

Figure 1. Typical MSP430 Application

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1999, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

TPS3705-30, TPS3705-33, TPS3705-50

TPS3707-25, TPS3707-30, TPS3707-33, TPS3707-50

PROCESSOR SUPERVISORY CIRCUITS WITH POWER-FAIL

SLVS184B ± NOVEMBER 1998 ± REVISED JANUARY 1999

description

The TPS3705, TPS3707 family of microprocessor supply-voltage supervisors provide circuit initialization and timing supervision, primarily for DSP and processor-based systems.

During power-on, RESET is asserted when the supply voltage VDD becomes higher than 1.1 V. Thereafter, the

supply voltage supervisor monitors VDD and keeps RESET active as long as VDD remains below the threshold voltage VIT+. An internal timer delays the return of the output to the inactive state (high) to ensure proper system reset. The delay time, td typ = 200 ms, starts after VDD has risen above the threshold voltage VIT+. When the supply voltage drops below the threshold voltage VIT± , the output becomes active (low) again. No external components are required. All the devices of this family have a fixed-sense threshold voltage VIT± set by an internal voltage divider.

The TPS3705-xx and TPS3707-xx devices incorporate a manual reset input, MR. A low level at MR causes RESET to become active.

The TPS370x-xx families integrate a power-fail comparator which can be used for low-battery detection, power-fail warning, or for monitoring a power supply other than the main supply.

The TPS3705-xx devices have a watchdog timer that is periodically triggered by a positive or negative transition at WDI. When the supervising system fails to retrigger the watchdog circuit within the time-out interval,

tt(out) = 1.6 s, WDO becomes active. This event also reinitializes the watchdog timer. Leaving WDI unconnected disables the watchdog.

The TPS3707-xx devices do not have the Watchdog function, but include a high-level output RESET.

The product spectrum is designed for supply voltages of 2.5 V, 3 V, 3.3 V, and 5 V. The circuits are available in either 8-pin MSOP or standard SOIC packages. The TPS3705, TPS3707 devices are characterized for operation over a temperature range of ±40°C to 85°C.

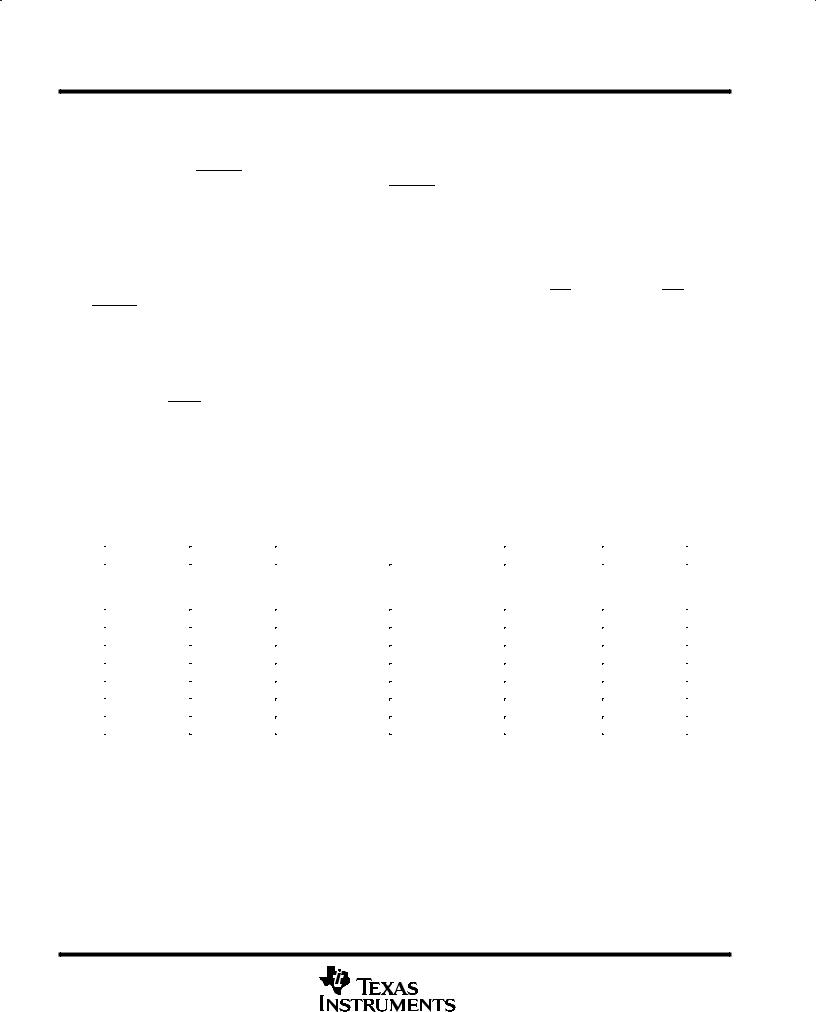

AVAILABLE OPTIONS

|

|

PACKAGED DEVICES |

|

|

||

|

THRESHOLD |

|

|

MARKING DGN |

CHIP FORM |

|

TA |

SMALL OUTLINE |

POWER±PAD |

||||

VOLTAGE |

μ-SMALL OUTLINE |

PACKAGE |

(Y) |

|||

|

(D) |

|||||

|

|

(DGN) |

|

|

||

|

|

|

|

|

||

|

|

|

|

|

|

|

|

2.63 V |

TPS3705±30D |

TPS3705±30DGN |

TIAAT |

TPS3705-30Y |

|

|

|

|

|

|

|

|

|

2.93 V |

TPS3705±33D |

TPS3705±33DGN |

TIAAU |

TPS3705±33Y |

|

|

|

|

|

|

|

|

|

4.55 V |

TPS3705±50D |

TPS3705±50DGN |

TIAAV |

TPS3705±50Y |

|

±40°C to 85°C |

|

|

|

|

|

|

2.25 V |

TPS3707±25D |

TPS3707±25DGN |

TIAAW |

TPS3707±25Y |

||

|

|

|

|

|

|

|

|

2.63 V |

TPS3707±30D |

TPS3707±30DGN |

TIAAX |

TPS3707±30Y |

|

|

|

|

|

|

|

|

|

2.93 V |

TPS3707±33D |

TPS3707±33DGN |

TIAAY |

TPS3707±33Y |

|

|

|

|

|

|

|

|

|

4.55 V |

TPS3707±50D |

TPS3707±50DGN |

TIAAZ |

TPS3707±50Y |

|

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TPS3705-30, TPS3705-33, TPS3705-50

TPS3707-25, TPS3707-30, TPS3707-33, TPS3707-50

PROCESSOR SUPERVISORY CIRCUITS WITH POWER-FAIL

SLVS184B ± NOVEMBER 1998 ± REVISED JANUARY 1999

Function Tables

TRUTH TABLE, TPS3705

|

|

|

VDD>VIT |

|

|

|

TYPICAL |

|

MR |

|

RESET |

||||

|

|

DELAY |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

H→ L |

1 |

|

H→ L |

30 ns |

|||

L→ H |

1 |

|

L→ H |

200 ms |

|||

|

H |

1→ 0 |

|

H→ L |

3 ms |

||

|

H |

0→ 1 |

|

L→ H |

200 ms |

||

TRUTH TABLE, TPS3707

|

|

|

VDD>VIT |

|

|

|

|

|

RESET |

TYPICAL |

|

|

MR |

|

|

RESET |

|||||||

|

|

|

DELAY |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

H→ L |

1 |

|

|

H→ L |

L→ H |

30 ns |

|||||

L→ H |

1 |

|

|

L→ H |

H→ L |

200 ms |

|||||

|

H |

1→ 0 |

|

|

H→ L |

L→ H |

3 ms |

||||

|

H |

0→ 1 |

|

|

L→ H |

H→ L |

200 ms |

||||

|

|

|

|

TRUTH TABLE, TPS370x |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TYPICAL |

|

|

|

|

|

PFI>VIT |

|

|

PFO |

|

|||

|

|

|

|

|

|

DELAY |

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

0→ 1 |

|

L→ H |

0.5 ms |

|

|||

|

|

|

|

1→ 0 |

|

H→ L |

0.5 ms |

|

|||

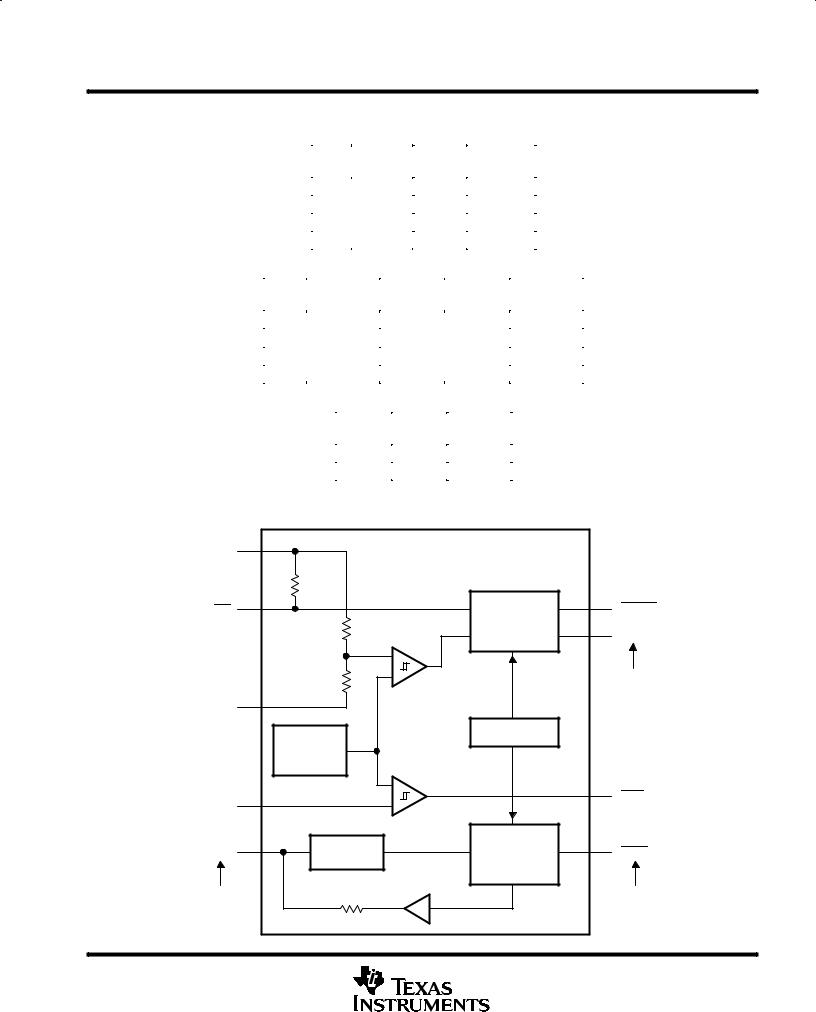

functional block diagram

VDD |

|

TPS3705 |

|

|

|

TPS3707 |

|

||

|

14 kW |

|

|

|

MR |

|

Reset |

RESET |

|

|

R1 |

Logic + Timer |

RESET |

|

|

|

|||

|

|

|

||

|

|

+ |

|

|

|

R2 |

_ |

Only |

|

|

|

|||

|

|

TPS3707 |

||

|

|

|

||

GND |

|

|

|

|

|

Reference |

Oscillator |

|

|

|

|

|

||

|

Voltage |

|

|

|

|

of 1.25 V |

|

|

|

|

|

_ |

|

|

PFI |

|

+ |

PFO |

|

|

|

|||

WDI |

Transition |

Watchdog |

WDO |

|

Detection |

Logic + Timer |

|||

|

|

|||

Only |

40 kW |

|

Only |

|

TPS3705 |

|

|

TPS3705 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

TPS3705-30, TPS3705-33, TPS3705-50 TPS3707-25, TPS3707-30, TPS3707-33, TPS3707-50

PROCESSOR SUPERVISORY CIRCUITS WITH POWER-FAIL

SLVS184B ± NOVEMBER 1998 ± REVISED JANUARY 1999

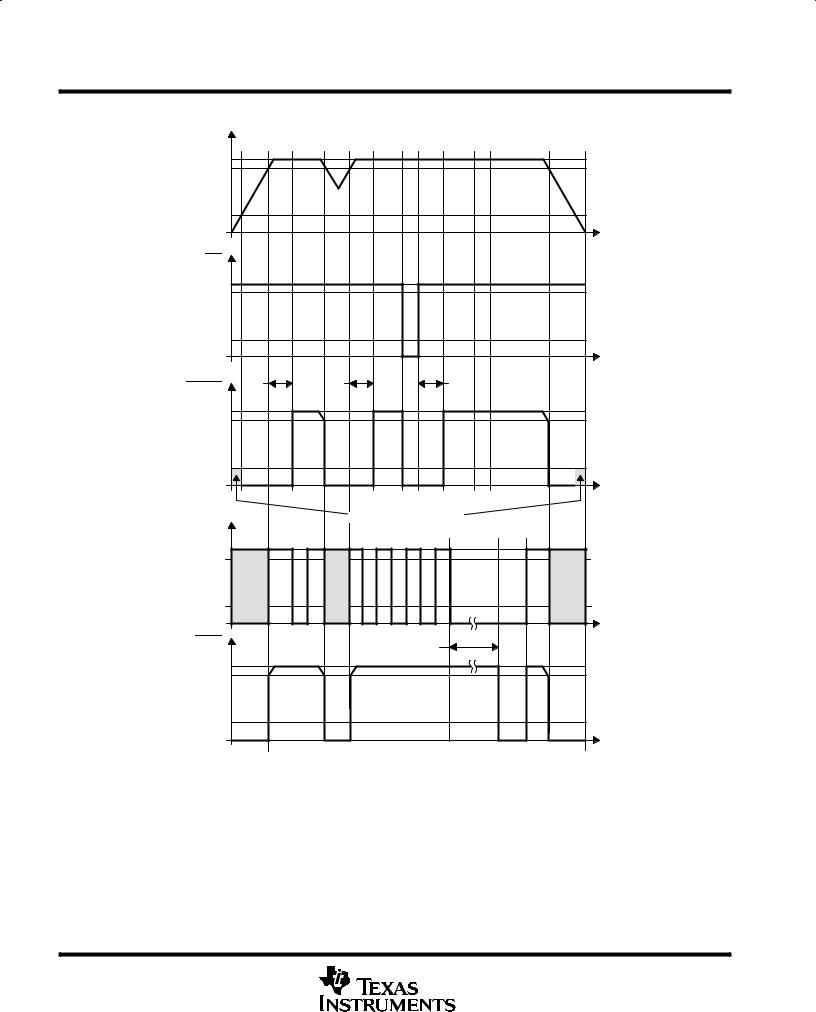

timing diagrams

VDD |

|

|

5 V |

|

|

4.5 |

V |

|

1.1 |

V |

|

0 |

V |

t |

MR |

|

|

5 V |

|

|

4.5 |

V |

|

1.1 |

V |

|

|

|

0 |

V |

|

|

t |

RESET |

t d |

t d |

t d |

|

5 V |

|

|

|

|

4.5 |

V |

|

|

|

1.1 |

V |

|

|

|

0 |

V |

|

|

t |

WDI |

|

|

Undefined Behavior |

|

|

|

|

||

5 V |

|

|

|

|

4.5 |

V |

Don't Care |

Don't Care |

Don't Care |

1.1 |

V |

|||

0 |

V |

|

|

t |

WDO |

|

|

t t(out) |

|

|

|

|

|

|

5 V |

|

|

|

|

4.5 |

V |

|

|

|

1.1 |

V |

|

0 |

V |

t |

4 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

Loading...

Loading...