Texas Instruments TPS2321IPWR, TPS2321IPW, TPS2321IDR, TPS2321ID, TPS2320IPWR Datasheet

...

TPS2320, TPS2321 DUAL HOT SWAP POWER CONTROLLER WITH INDEPENDENT CIRCUIT BREAKER

SLVS276A ± MARCH 200 ± REVISED APRIL 2000

features

DDual-Channel High-Side MOSFET Drivers

DIN1: 3 V to 13 V; IN2: 3 V to 5.5 V

DInrush Current Limiting With dv/dt Control

DIndependent Circuit-Breaker Control With Programmable Current Limit and Transient Timer

DCMOSand TTL-Compatible Enable Input

DLow, 5- A Standby Supply Current . . . Max

DAvailable in 16-Pin SOIC and TSSOP Package

D±40°C to 85°C Ambient Temperature Range

DElectrostatic Discharge Protection

D OR PW PACKAGE

(TOP VIEW)

GATE1 |

|

|

1 |

16 |

|

|

DISCH1 |

|

|

|

|

||||

GATE2 |

|

2 |

15 |

|

|

DISCH2 |

|

|

|

|

|

||||

DGND |

|

3 |

14 |

|

|

ENABLE |

|

|

|

|

|

||||

TIMER |

|

4 |

13 |

|

|

FAULT |

|

|

|

|

|

||||

VREG |

|

5 |

12 |

|

|

ISET1 |

|

|

|

|

|

||||

|

|

|

|

||||

|

6 |

11 |

|

|

|

||

AGND |

|

|

|

|

ISET2 |

||

|

|

|

|

||||

ISENSE2 |

|

7 |

10 |

|

|

IN2 |

|

|

|

|

|

||||

|

|

|

|

||||

|

8 |

9 |

|

|

|

||

ISENSE1 |

|

|

|

|

IN1 |

||

|

|

|

|

||||

|

|

|

|

|

|

|

|

NOTE: Terminal 14 is active high on TPS2321.

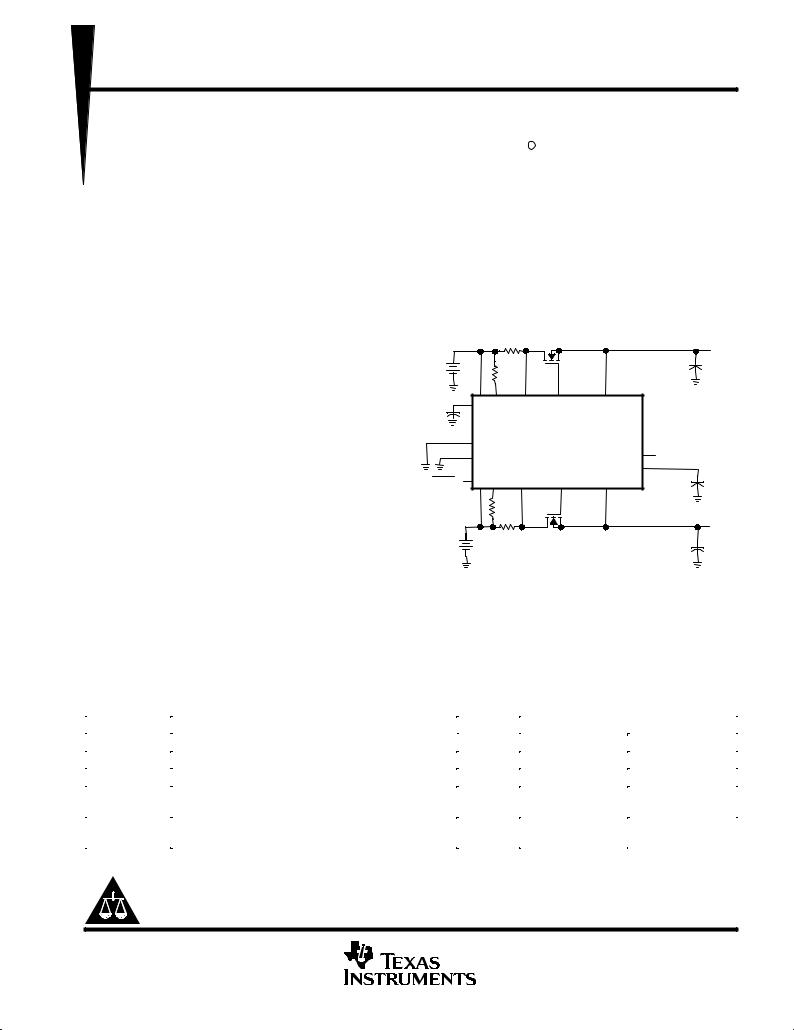

typical application

applications

DHot-Swap/Plug/Dock Power Management

DHot-Plug PCI, Device Bay

DElectronic Circuit Breaker

description

The TPS2320 and TPS2321 are dual-channel hot-swap controllers that use external N-channel MOSFETs as high-side switches in power applications. Features of these devices, such as overcurrent protection (OCP), inrush-current control, and separation of load transients from actual load increases, are critical requirements for hot-swap applications.

VO1

+

V1

3 V ± 13 V

|

IN1 ISET1 ISENSE1 GATE1 |

DISCH1 |

VREG |

|

|

AGND |

TPS2320 |

|

|

|

|

DGND |

|

FAULT |

|

|

|

|

|

TIMER |

ENABLE

IN2 |

ISET2 ISENSE2 |

GATE2 |

DISCH2 |

|

|

|

VO2 |

V2 |

|

|

+ |

|

|

|

|

|

3 V ± 5.5 V |

|

|

The TPS2320/21 devices incorporate undervoltage lockout (UVLO) to ensure the device is off at startup. Each internal charge pump, capable of driving multiple MOSFETs, provides enough gate-drive voltage to fully enhance the N-channel MOSFETs. The charge pumps control both the rise times and fall times (dv/dt) of the MOSFETs, reducing power transients during power up/down. The circuit-breaker functionality combines the ability to sense overcurrent conditions with a timer function; this allows designs such as DSPs, that may have high peak currents during power-state transitions, to disregard transients for a programmable period.

AVAILABLE OPTIONS

TA |

HOT-SWAP CONTROLLER DESCRIPTION |

PIN |

|

|

PACKAGES |

|||

COUNT |

ENABLE |

ENABLE |

||||||

|

|

|

||||||

|

Dual-channel with independent OCP and adjustable PG |

|

20 |

TPS2300IPW |

TPS2301IPW |

|||

|

Dual-channel with interdependent OCP and adjustable PG |

|

20 |

TPS2310IPW |

TPS2311IPW |

|||

± 40°C to 85°C |

Dual-channel with independent OCP |

16 |

TPS2320ID |

TPS2321ID |

||||

TPS2320IPW |

TPS2321IPW |

|||||||

|

|

|

|

|||||

|

|

|

|

|

|

|||

|

Single-channel with OCP and adjustable PG |

|

14 |

TPS2330ID |

TPS2331ID |

|||

|

|

TPS2330IPW |

TPS2331IPW |

|||||

|

|

|

|

|||||

² The packages are available left-end taped and reeled (indicated by the R suffix on the device type; e.g., TPS2321IPWR).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 2000, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

TPS2320, TPS2321

DUAL HOT SWAP POWER CONTROLLER

WITH INDEPENDENT CIRCUIT BREAKER

SLVS276A ± MARCH 200 ± REVISED APRIL 2000

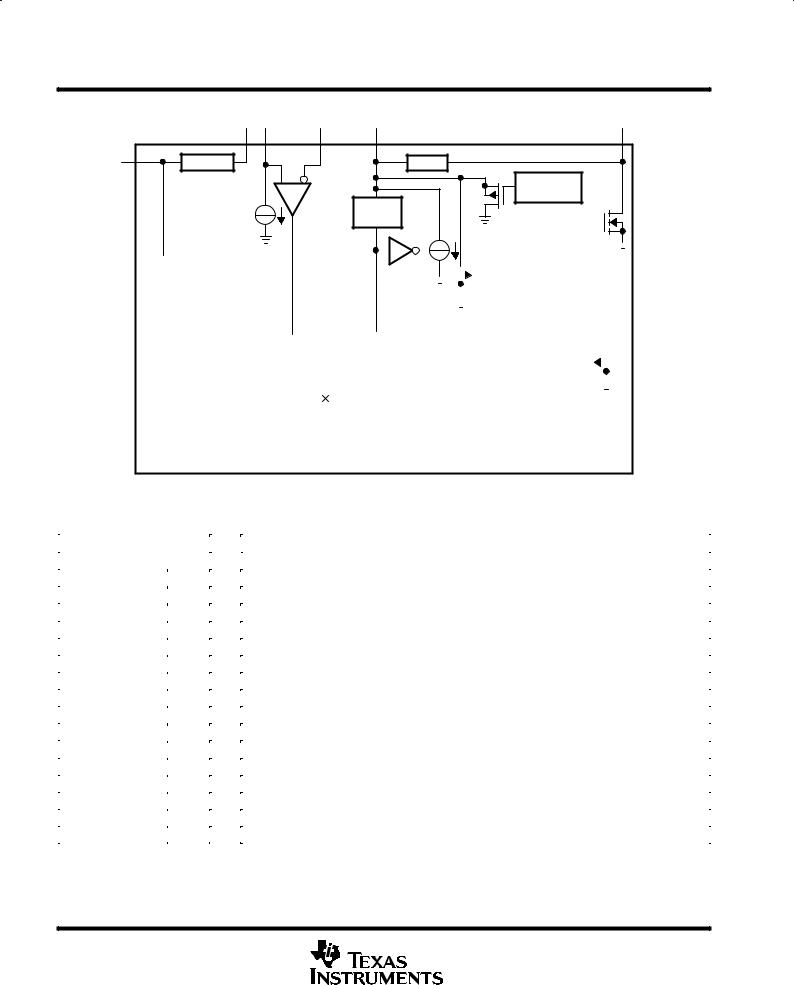

functional block diagram

IN1 |

ISET1 |

ISENSE1 GATE1 |

DISCH1 |

VREG |

PREREG |

|

Clamp |

|

|

|

dv/dt Rate |

|

|

|

Protection |

|

50 A |

Circuit |

Charge |

|

Pump |

||

|

Breaker |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pulldown FET |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

AGND |

|

|

|

|

|

UVLO and |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Circuit Breaker |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

Power-Up |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

DGND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

75 A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FAULT |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ENABLE |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Logic |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

50- s Deglitch |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TIMER |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Second Channel |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IN2 |

|

|

ISET2 |

ISENSE2 |

GATE2 |

DISCH2 |

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Terminal Functions |

|||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

TERMINAL |

|

I/O |

|

|

|

|

|

|

|

|

|

|

DESCRIPTION |

|||||||||||||||||||||||||||||||||||||

|

NAME |

|

|

NO. |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||

|

AGND |

6 |

|

|

I |

Analog ground, connects to DGND as close as possible |

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

DGND |

3 |

|

|

I |

Digital ground |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

DISCH1 |

16 |

|

|

O |

Discharge transistor 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

DISCH2 |

15 |

|

|

O |

Discharge transistor 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

|

ENABLE |

14 |

|

|

I |

Active low (TPS2320) or active high enable (TPS2321) |

|||||||||||||||||||||||||||||||||||||||||||||

|

ENABLE/ |

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

FAULT |

13 |

|

|

O |

Overcurrent fault, open-drain output |

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

GATE1 |

1 |

|

|

O |

Connects to gate of channel 1 high-side MOSFET |

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

GATE2 |

2 |

|

|

O |

Connects to gate of channel 2 high-side MOSFET |

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

IN1 |

9 |

|

|

I |

Input voltage for channel 1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

IN2 |

10 |

|

|

I |

Input voltage for channel 2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

ISENSE1 |

8 |

|

|

I |

Current-sense input channel 1 |

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

ISENSE2 |

7 |

|

|

I |

Current-sense input channel 2 |

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

ISET1 |

12 |

|

|

I |

Adjusts circuit-breaker threshold with resistor connected to IN1 |

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

ISET2 |

11 |

|

|

I |

Adjusts circuit-breaker threshold with resistor connected to IN2 |

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

TIMER |

4 |

|

|

O |

Adjusts circuit-breaker deglitch time |

||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||

|

VREG |

5 |

|

|

O |

Connects to bypass capacitor, for stable operation |

||||||||||||||||||||||||||||||||||||||||||||||

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TPS2320, TPS2321

DUAL HOT SWAP POWER CONTROLLER

WITH INDEPENDENT CIRCUIT BREAKER

SLVS276A ± MARCH 200 ± REVISED APRIL 2000

detailed description

DISCH1, DISCH2 ± DISCH1 and DISCH2 should be connected to the sources of the external N-channel MOSFET transistors connected to GATE1 and GATE2, respectively. These pins discharge the loads when the MOSFET transistors are disabled. They also serve as reference-voltage connections for internal gate voltage-clamp circuitry.

ENABLE or ENABLE ± ENABLE for TPS2320 is active low. ENABLE for TPS2321 is active high. When the controller is enabled, both GATE1 and GATE2 voltages will power up to turn on the external MOSFETs. When the ENABLE pin is pulled high for TPS2320 or the ENABLE pin is pulled low for TPS2321 for more than 50 s, the gate of the MOSFET is discharged at a controlled rate by a current source, and a transistor is enabled to discharge the output bulk capacitance. In addition, the device turns on the internal regulator PREREG (see VREG) when enabled and shuts down PREREG when disabled so that total supply current is much less than 5 A.

FAULT ± FAULT is an open-drain overcurrent flag output. When an overcurrent condition in either channel is sustained long enough to charge TIMER to 0.5 V, the overcurrent channel latches off and pulls FAULT low. The other channel will run normally if not in overcurrent.

GATE1, GATE2 ± GATE1 and GATE2 connect to the gates of external N-channel MOSFET transistors. When the device is enabled, internal charge-pump circuitry pulls these pins up by sourcing approximately 15 A to each. The turnon slew rates depend upon the capacitance present at the GATE1 and GATE2 terminals. If desired, the turnon slew rates can be further reduced by connecting capacitors between these pins and ground. These capacitors also reduce inrush current and protect the device from false overcurrent triggering during powerup. The charge-pump circuitry will generate gate-to-source voltages of 9 V±12 V across the external MOSFET transistors.

IN1, IN2 ± IN1 and IN2 should be connected to the power sources driving the external N-channel MOSFET transistors connected to GATE1 and GATE2, respectively. The TPS2320/TPS2321 draws its operating current from IN1, and both channels will remain disabled until the IN1 power supply has been established. The IN1 channel has been constructed to support 3-V, 5-V, or 12-V operation, while the IN2 channel has been constructed to support 3-V or 5-V operation

ISENSE1, ISENSE2, ISET1, ISET2 ± ISENSE1 and ISENSE2, in combination with ISET1 and ISET2, implement overcurrent sensing for GATE1 and GATE2. ISET1 and ISET2 set the magnitude of the current that generates an overcurrent fault, through external resistors connected to ISET1 and ISET2. An internal current source draws 50 A from ISET1 and ISET2. With a sense resistor from IN1 to ISENSE1 or from IN2 to ISENSE2, which is also connected to the drains of external MOSFETs, the voltage on the sense resistor reflects the load current. An overcurrent condition is assumed to exist if ISENSE1 is pulled below ISET1 or if ISENSE2 is pulled below ISET2.

TIMER ± A capacitor on TIMER sets the time during which the power switch can be in overcurrent before turning off. When the overcurrent protection circuits sense an excessive current, a current source is enabled which charges the capacitor on TIMER. Once the voltage on TIMER reaches approximately 0.5 V, the circuit-breaker latch is set and the power switch is latched off. Power must be recycled or the ENABLE pin must be toggled to restart the controller. In high-power or high-temperature applications, a minimum 50-pF capacitor is strongly recommended from TIMER to ground, to prevent any false triggering.

VREG ± The VREG pin is the output of an internal low-dropout voltage regulator. This regulator draws current from IN1. A 0.1- F ceramic capacitor should be connected between VREG and ground. VREG can be connected to IN1, IN2, or to a separated power supply through a low-resistance resistor. However, the voltage on VREG must be less than 5.5 V.

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

TPS2320, TPS2321

DUAL HOT SWAP POWER CONTROLLER

WITH INDEPENDENT CIRCUIT BREAKER

SLVS276A ± MARCH 200 ± REVISED APRIL 2000

absolute maximum ratings over operating free-air temperature (unless otherwise noted)²

Input voltage range: |

VI(IN1), VI(ISENSE1), VI(ISET1), VI(ENABLE) . . . . . . . . . . . . . . . . . . . |

. . . . ±0.3 V to 15 |

V |

|

VI(IN2), VI(ISENSE2), VI(ISET2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . ±0.3 V to 7 |

V |

Output voltage range: VO(GATE1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . ±0.3 V to 30 |

V |

|

|

VO(GATE2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . ±0.3 V to 22V |

|

|

VO(DISCH1), VO(FAULT), VO(VREG), VO(DISCH2), VO(TIMER), |

. . . . . ±0.3 V to 15V |

|

Sink current range: |

IGATE1, IGATE2, IDISCH1, IDISCH2 . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . 0 mA to 100 mA |

|

|

ITIMER, IFAULT . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . 0 mA to 10 mA |

|

Operating virtual junction temperature range, TJ . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . ±40°C to 100°C |

||

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . ±55°C to 150°C |

||

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . 260°C |

||

² Stresses beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltages are respect to DGND.

DISSIPATION RATING TABLE

PACKAGE |

TA ≤ 25°C |

DERATING FACTOR |

TA = 70°C |

TA = 85°C |

|

POWER RATING |

ABOVE TA = 25°C |

POWER RATING |

POWER RATING |

||

|

|||||

PW-16 |

823 mW |

10.98 mW/°C |

329 mW |

165 mW |

|

|

|

|

|

|

|

D-16 |

674 mW |

8.98 mW/°C |

270 mW |

135 mW |

recommended operating conditions

|

|

MIN NOM |

MAX |

UNIT |

|

|

|

|

|

|

|

Input voltage, VI |

VI(IN1), VI(ISENSE1), VI(ISET1) |

3 |

13 |

V |

|

VI(IN2), VI(ISENSE2), VI(ISET2) |

3 |

5.5 |

|||

|

|

||||

VREG voltage, VO(VREG), when VREG is directly connected to IN1 |

2.95 |

5.5 |

V |

||

Operating virtual junction temperature, TJ |

±40 |

100 |

°C |

||

4 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TPS2320, TPS2321

DUAL HOT SWAP POWER CONTROLLER

WITH INDEPENDENT CIRCUIT BREAKER

SLVS276A ± MARCH 200 ± REVISED APRIL 2000

electrical characteristics over recommended operating temperature range (±40°C < TA < 85°C), 3 V ≤ VI(IN1) ≤13 V, 3 V ≤ VI(IN2) ≤ 5.5 V (unless otherwise noted)

general

|

PARAMETER |

|

TEST CONDITIONS |

MIN TYP |

MAX |

UNIT |

||

|

|

|

|

|

|

|

|

|

II(IN1) |

Input current, IN1 |

VI(ENABLE) = 5 |

V (TPS2321), |

0.5 |

1 |

mA |

||

|

|

|

|

|

|

A |

||

II(IN2) |

Input current, IN2 |

V |

I(ENABLE) |

= 0 |

V (TPS2320) |

75 |

200 |

|

|

Standby current (sum of currents into IN1, IN2, |

VI(ENABLE) = 0 |

V (TPS2321), |

|

|

|

||

II(stby) |

ISENSE1, ISENSE2, ISET1, and ISET2) |

|

|

|

|

|

5 |

A |

VI(ENABLE) = 5 V (TPS2320) |

|

|||||||

|

|

|

|

|||||

|

|

|

|

|

||||

GATE1

|

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

||

|

|

|

|

|

|

|

|

|

VG(GATE1_3V) |

|

|

II(GATE1) = 500 nA, |

VI(IN1) = 3 V |

9 |

11.5 |

|

|

VG(GATE1_4.5V) |

|

Gate voltage |

VI(IN1) = 4.5 V |

10.5 |

14.5 |

|

V |

|

|

DISCH1 open |

|

||||||

VG(GATE1_10.8V) |

|

|

VI(IN1) = 10.8 V |

16.8 |

21 |

|

|

|

VC(GATE1) |

|

Clamping voltage, GATE1 |

|

|

9 |

10 |

12 |

V |

|

to DISCH1 |

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IS(GATE1) |

|

Source current, GATE1 |

3 V ≤ VI(IN1) ≤ 13.2 V, 3 V ≤ VO(VREG) ≤ 5.5 V, |

10 |

14 |

20 |

A |

|

|

VI(GATE1) = VI(IN1) + 6 V |

|

||||||

|

|

|

|

|

|

|

|

|

|

|

Sink current, GATE1 |

3 V ≤ VI(IN1) ≤ 13.2 V, 3 V ≤ VO(VREG) ≤ 5.5 V, |

50 |

75 |

100 |

A |

|

|

|

VI(GATE1) = VI(IN1) |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

VI(IN1) = 3 V |

|

0.5 |

|

|

tr(GATE1) |

|

Rise time, GATE1 |

Cg to GND = 1 nF (see Note 2) |

VI(IN1) = 4.5 V |

|

0.6 |

|

ms |

|

|

|

|

VI(IN1) = 10.8 V |

|

1 |

|

|

|

|

|

|

VI(IN1) = 3 V |

|

0.1 |

|

|

tf(GATE1) |

|

Fall time, GATE1 |

Cg to GND = 1 nF (see Note 2) |

VI(IN1) = 4.5 V |

|

0.12 |

|

ms |

|

|

|

|

VI(IN1) = 10.8 V |

|

0.2 |

|

|

GATE2

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

||||

|

|

|

|

|

|

|

|

|

|

VG(GATE2_3V) |

Gate voltage |

II(GATE2) = 500 nA, DISCH2 open |

VI(IN2) = 3 V |

9 |

11.7 |

|

V |

||

VG(GATE2_4.5V) |

VI(IN2) = 4.5 V |

10.5 |

14.7 |

|

|||||

|

|

|

|

|

|||||

VC(GATE2) |

Clamping voltage, |

|

|

|

9 |

10 |

12 |

V |

|

GATE2 to DISCH2 |

|

|

|

||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

||

IS(GATE2) |

Source current, |

3 V ≤ VI(IN2) ≤ 5.5 V, |

3 V ≤ VO(VREG) ≤ 5.5 V, |

10 |

14 |

20 |

A |

||

GATE2 |

VI(GATE2) = VI(IN2) |

+ 6 V |

|||||||

|

|

|

|

|

|||||

|

Sink current, GATE2 |

3 V ≤ VI(IN2) ≤ 5.5 V, |

3 V ≤ VO(VREG) ≤ 5.5 V, |

50 |

75 |

100 |

A |

||

|

VI(GATE2) = VI(IN2) |

|

|

||||||

|

|

|

|

|

|

|

|

||

tr(GATE2) |

Rise time, GATE2 |

Cg to GND = 1 nF |

VI(IN2) = 3 V |

|

|

0.5 |

|

ms |

|

(see Note 2) |

VI(IN2) = 4.5 V |

VO(VREG) = 3 V |

|

0.6 |

|

||||

|

|

|

|

|

|||||

tf(GATE2) |

Fall time, GATE2 |

Cg to GND = 1 nF |

VI(IN2) = 3 V |

|

0.1 |

|

ms |

||

|

|

|

|||||||

(see Note 2) |

VI(IN2) = 4.5 V |

|

|

0.12 |

|

||||

|

|

|

|

|

|

|

|||

NOTE 2: Specified, but not production tested.

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

5 |

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

|

|

|

|

|

|

VOT(TIMER) Threshold voltage, TIMER |

|

0.4 |

0.5 |

0.6 |

V |

Charge current, TIMER |

VI(TIMER) = 0 V |

35 |

50 |

65 |

µA |

Discharge current, TIMER |

VI(TIMER) = 1 V |

1 |

2.5 |

|

mA |

|

|

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

|

|

|

|

|

|

|

|

|

|

VIT(CB) |

Undervoltage voltage, circuit breaker |

RISETx = 1 kΩ |

|

40 |

50 |

60 |

mV |

|

IIB(ISENSEx) |

Input bias current, ISENSEx |

|

|

|

0.1 |

5 |

µA |

|

|

|

Discharge current, GATEx |

VO(GATEx) = 4 V |

|

400 |

800 |

|

mA |

|

|

VO(GATEx) = 1 V |

|

25 |

150 |

|

||

|

|

|

|

|

|

|||

tpd(CB) |

Propagation (delay) time, comparator inputs to |

Cg = 50 pF, |

10 mV overdrive, |

|

1.3 |

|

µs |

|

gate output |

(50% to 10%) |

CO(timer) = 50 pF |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PARAMETER |

|

|

TEST CONDITIONS |

|

|

MIN |

TYP |

MAX |

UNIT |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

V |

|

|

|

|

|

|

High-level input voltage, |

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

V |

|||||||

IH(ENABLE) |

|

|

ENABLE |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

V |

|

|

|

|

|

|

|

Low-level input voltage, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

0.8 |

V |

|||||

IL(ENABLE) |

|

|

ENABLE |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

Input pullup resistance, |

|

|

|

|

|

|

|

|

|

|

|

kΩ |

||||||||||

RI(ENABLE) |

See Note 3 |

|

|

|

100 |

200 |

300 |

||||||||||||||||||||||||

ENABLE |

|

|

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

increasing above stop threshold; 100 |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I(ENABLE) |

|

|

|

µs |

|||||||

td_off(ENABLE) |

Turnoff delay time, ENABLE |

|

60 |

|

|||||||||||||||||||||||||||

ns rise time, 20 mV overdrive (see Note 2) |

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

decreasing below start threshold; |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I(ENABLE) |

|

|

|

µs |

|||||||

td_on(ENABLE) |

Turnon delay time, ENABLE |

|

125 |

|

|||||||||||||||||||||||||||

100 ns fall time, 20 mV overdrive (see Note 2) |

|

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES: 2. Specified, but not production tested. |

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 V |

|

|

|

|

||

|

|

|

|

3. Test IO of ENABLE at VI(ENABLE) = 1 V and 0 V, then RI(ENABLE) = |

|

|

|

||||||||||||||||||||||||

|

|

|

|

IO_0V |

IO_1V |

|

|

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

|

|

|

|

|

|

|

VIH(ENABLE) |

High-level input voltage, ENABLE |

|

2 |

|

|

V |

VIL(ENABLE) |

Low-level input voltage, ENABLE |

|

|

|

0.7 |

V |

RI(ENABLE) |

Input pulldown resistance, |

|

100 |

150 |

300 |

kΩ |

ENABLE |

|

|||||

td_on(ENABLE) |

Turnon delay time, ENABLE |

VI(ENABLE) increasing above start threshold; |

|

85 |

|

µs |

100 ns rise time, 20 mV overdrive (see Note 2) |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

td_off(ENABLE) |

Turnoff delay time, ENABLE |

VI(ENABLE) decreasing below stop threshold; |

|

100 |

|

µs |

100 ns fall time, 20 mV overdrive (see Note 2) |

|

|

||||

|

|

|

|

|

|

NOTE 2: Specified, but not production tested.

PREREG

|

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

|

|

|

|

|

|

|

VREG |

PREREG output voltage |

4.5 ≤ VI(IN1) ≤ 13 V |

3.5 |

4.1 |

5.5 |

V |

Vdrop_PREREG |

PREREG dropout voltage |

VI(IN1) = 3 V |

|

|

0.1 |

V |

6 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TPS2320, TPS2321

DUAL HOT SWAP POWER CONTROLLER

WITH INDEPENDENT CIRCUIT BREAKER

SLVS276A ± MARCH 200 ± REVISED APRIL 2000

electrical characteristics over recommended operating temperature range (±40°C < TA < 85°C), 3 V ≤ VI(IN1) ≤13 V, 3 V ≤ VI(IN2) ≤ 5.5 V (unless otherwise noted) (continued)

VREG UVLO

|

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

|

|

|

|

|

|

|

VOT(UVLOstart) |

Output threshold voltage, start |

|

2.75 |

2.85 |

2.95 |

V |

VOT(UVLOstop) |

Output threshold voltage, stop |

|

2.65 |

2.78 |

|

V |

Vhys(UVLO) |

Hysteresis |

|

50 |

75 |

|

mV |

|

UVLO sink current, GATEx |

VI(GATEx) = 2 V |

10 |

|

|

mA |

FAULT output

|

PARAMETER |

TEST CONDITIONS |

MIN TYP MAX |

UNIT |

|

|

|

|

|

VO(sat)(FAULT) |

Output saturation voltage, FAULT |

IO = 2 mA |

0.4 |

V |

Ilkg(FAULT) |

Leakage current, FAULT |

VO(FAULT) = 13 V |

1 |

A |

DISCH1 and DISCH2

|

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX |

UNIT |

|

|

|

|

|

|

|

IDISCH |

Discharge current, DISCHx |

VI(DISCHx) = 1.5 V, VI(VIN1) = 5 V |

5 |

10 |

|

mA |

VIH(DISCH) |

Discharge on high-level input voltage |

|

2 |

|

|

V |

VIL(DISCH) |

Discharge on low-level input voltage |

|

|

|

1 |

V |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

7 |

Loading...

Loading...