Texas Instruments TLV2352MUB, TLV2352MJGB, TLV2352MJG, TLV2352MFKB, TLV2352IPWR Datasheet

...

TLV2352, TLV2352Y

LinCMOS DUAL LOW-VOLTAGE DIFFERENTIAL COMPARATORS

|

SLCS011B ± MAY 1992 ± REVISED MARCH 1999 |

|

|

D Wide Range of Supply Voltages |

D High Input Impedance . . . 1012 Ω Typ |

2 V to 8 V |

D Extremely Low Input Bias Current |

|

|

D Fully Characterized at 3 V and 5 V |

5 pA Typ |

D Very-Low Supply-Current Drain |

D Common-Mode Input Voltage Range |

120 µA Typ at 3 V |

Includes Ground |

D Output Compatible With TTL, MOS, and |

D Built-In ESD Protection |

CMOS |

|

D Fast Response Time . . . 200 ns Typ for |

|

TTL-Level Input Step |

|

description |

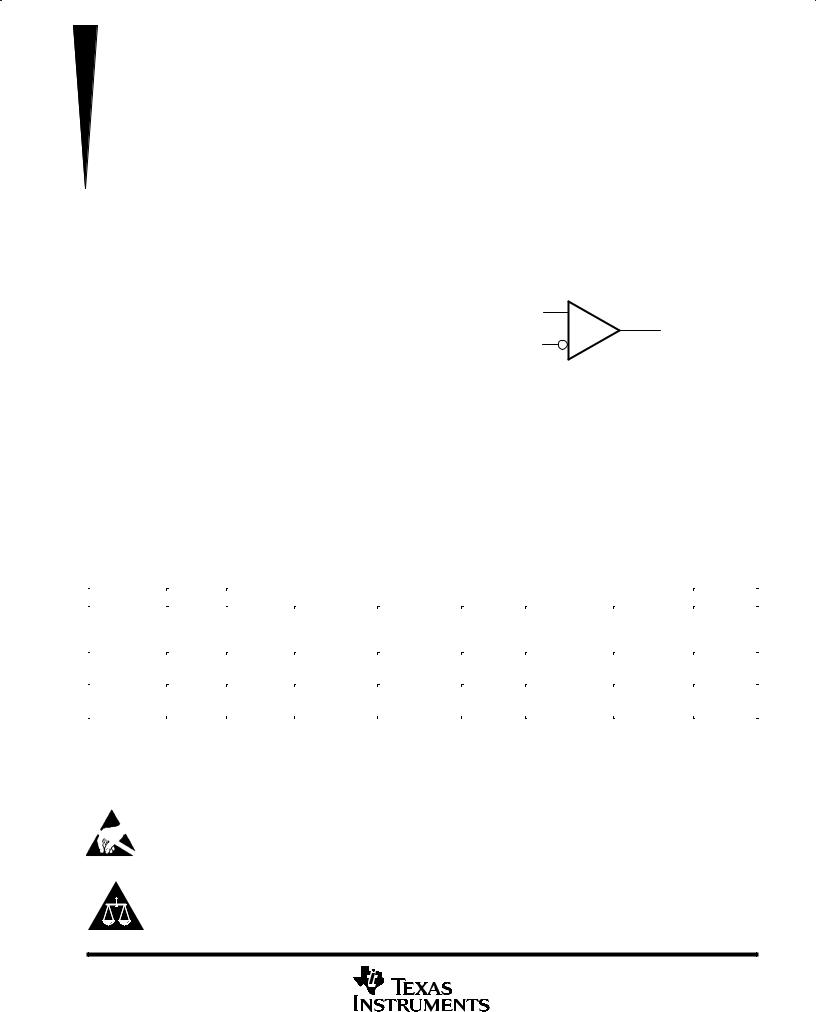

symbol (each comparator) |

|

The TLV2352 consists of two independent, low-power comparators specifically designed for single power-supply applications and operates with power-supply rails as low as 2 V. When powered from a 3-V supply, the typical supply current is only 120 µA.

IN +

OUT

IN ±

The TLV2352 is designed using the Texas Instruments LinCMOS technology and therefore features an extremely high input impedance (typically greater than 1012 Ω), which allows direct interfacing with high-impedance sources. The outputs are N-channel open-drain configurations that require an external pullup resistor to provide a positive output voltage swing, and they can be connected to achieve positive-logic wired-AND relationships. The TLV2352I is fully characterized at 3 V and 5 V for operation from ± 40°C to 85°C. The TLV2352M is fully characterized at 3 V and 5 V for operation from ± 55°C to 125°C.

The TLV2352 has internal electrostatic-discharge (ESD)-protection circuits and has been classified with a 1000-V ESD rating using Human Body Model testing. However, care should be exercised in handling this device as exposure to ESD may result in degradation of the device parametric performance.

AVAILABLE OPTIONS

|

|

|

|

PACKAGED DEVICES |

|

|

CHIP |

||

|

VIO max |

|

|

|

|

|

|

||

TA |

SMALL |

CHIP |

CERAMIC |

PLASTIC |

|

PLASTIC |

|||

TSSOP |

FORM |

||||||||

at 25°C |

OUTLINE |

CARRIER |

DIP |

DIP |

DIP |

||||

|

(PW)³ |

(Y) |

|||||||

|

|

(D)² |

(FK) |

(JG) |

(P) |

(U) |

|||

|

|

|

|

||||||

± 40°C to |

5 mV |

TLV2352ID |

Ð |

Ð |

TLV2352IP |

TLV2352IPWLE |

Ð |

|

|

85°C |

|

||||||||

|

|

|

|

|

|

|

TLV2352Y |

||

|

|

|

|

|

|

|

|

||

± 55°C to |

5 mV |

Ð |

TLV2352MFK |

TLV2352MJG |

Ð |

Ð |

TLV2352MU |

||

|

|||||||||

125°C |

|

||||||||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

² The D package is available taped and reeled. Add the suffix R to the device type (e.g., TLV2352IDR). ³ The PW packages are only available left-ended taped and reeled (e.g., TLV2352IPWLE)

These devices have limited built-in protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

LinCMOS is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1999, Texas Instruments Incorporated

On products compliant to MIL-PRF-38535, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters.

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

TLV2352, TLV2352Y

LinCMOS DUAL LOW-VOLTAGE DIFFERENTIAL COMPARATORS

SLCS011B ± MAY 1992 ± REVISED MARCH 1999

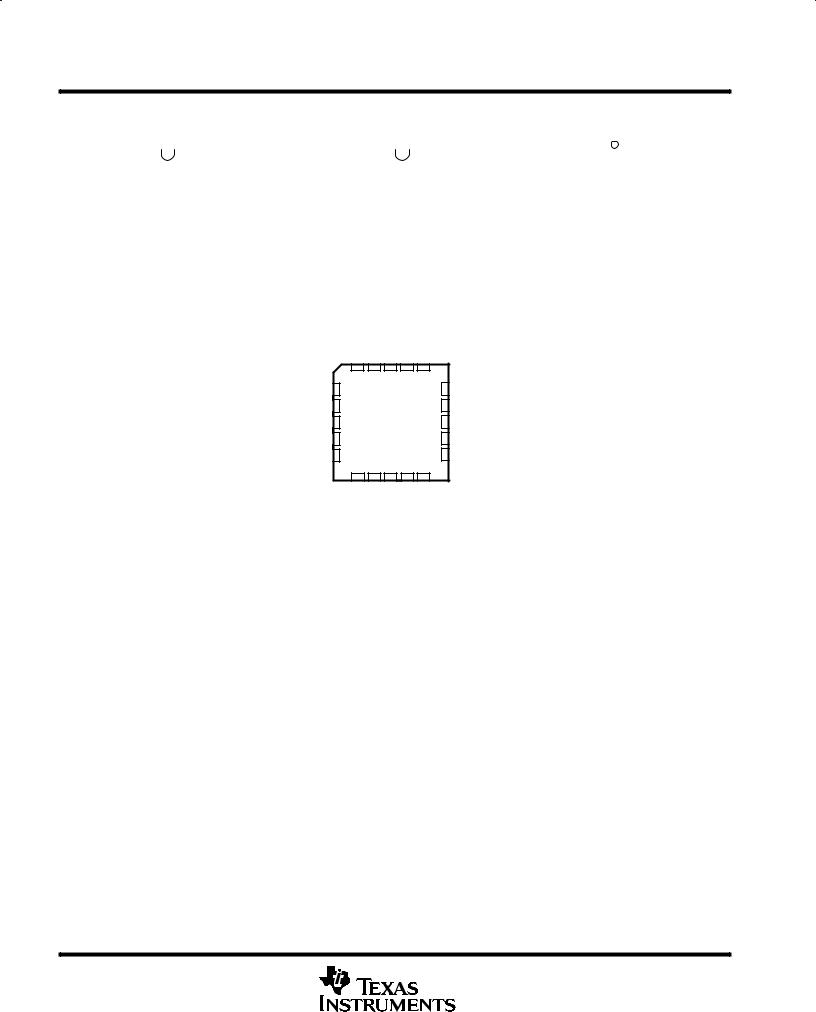

TLV2352I . . . D OR P PACKAGE |

|

|

TLV2254M |

|

TLV2352I . . . PW PACKAGE |

|||||||||||||

TLV2352M . . . JG PACKAGE |

|

|

U PACKAGE |

|

|

|

(TOP VIEW) |

|

||||||||||

|

|

(TOP VIEW) |

|

|

(TOP VIEW) |

|

1OUT |

|

|

|

|

VDD+ |

||||||

|

|

|

|

|

|

1 |

8 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

1OUT |

|

1 |

8 |

|

VDD+ |

NC |

|

•1 |

|

|

|

NC |

||||||

|

|

|

10 |

|

|

1IN ± |

|

2 |

7 |

|

2OUT |

|||||||

1IN ± |

|

2 |

7 |

|

2OUT |

1OUT |

|

2 |

9 |

|

|

VDD + |

1IN + |

|

3 |

6 |

|

2IN ± |

|

|

|

|

|

|

|

||||||||||||

1IN + |

|

3 |

6 |

|

2IN ± |

1IN ± |

|

3 |

8 |

|

|

2OUT |

VDD±/GND |

|

4 |

5 |

|

2IN + |

VDD±/GND |

|

4 |

5 |

|

2IN + |

1IN + |

|

4 |

7 |

|

|

2IN ± |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

VDD ±/GND |

|

5 |

6 |

|

|

2IN + |

NC ± No internal connection |

|||||

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TLV2352M |

|

||

|

FK PACKAGE |

|

|||

|

NC |

(TOP VIEW) |

|

||

|

1OUT |

NC |

V NC |

|

|

|

|

|

|

DD+ |

|

NC |

3 |

2 |

1 |

20 19 |

NC |

4 |

|

|

18 |

||

1IN ± |

5 |

|

|

17 |

2OUT |

NC |

6 |

|

|

16 |

NC |

1IN + |

7 |

|

|

15 |

2IN ± |

NC |

8 |

|

|

14 |

NC |

|

9 |

10 11 12 13 |

|

||

|

NC |

/GND |

NC |

2IN+ NC |

|

|

|

DD ± |

|

|

|

|

|

V |

|

|

|

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TLV2352, TLV2352Y

LinCMOS DUAL LOW-VOLTAGE DIFFERENTIAL COMPARATORS

SLCS011B ± MAY 1992 ± REVISED MARCH 1999

|

|

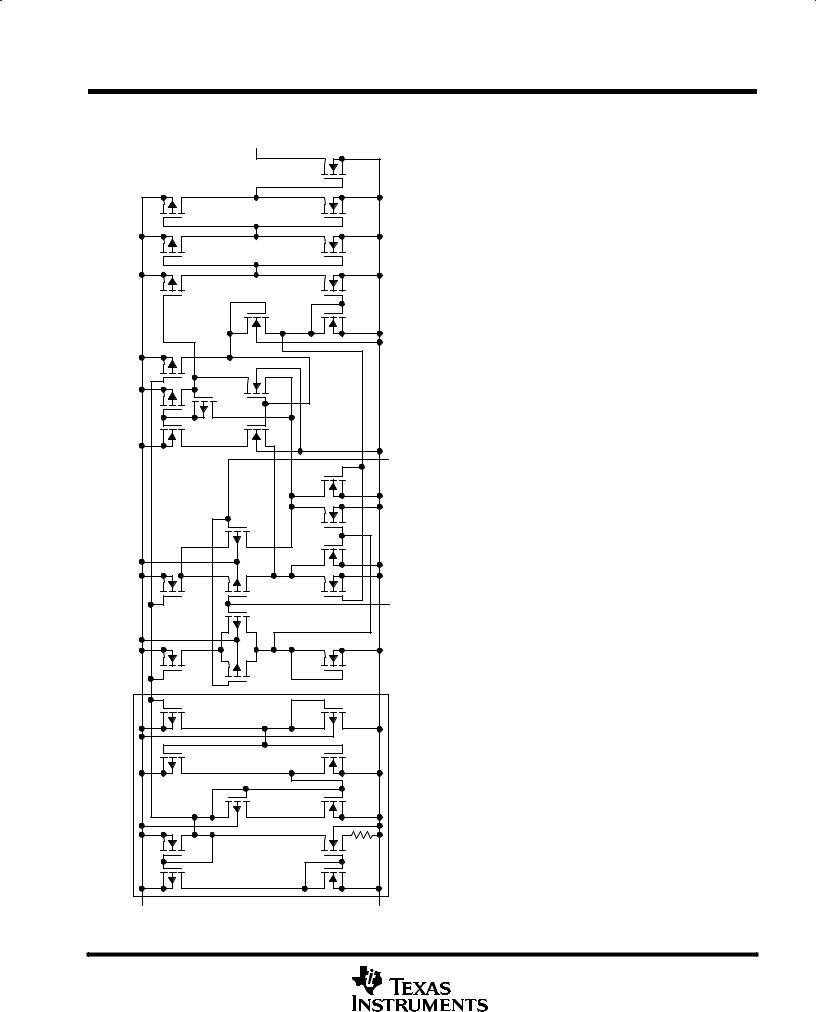

OUT |

|

|

IN ± |

|

|

IN + |

schematic |

Common to All Channels |

|

equivalent |

DD |

GND |

V |

POST OFFICE BOX 655303• DALLAS, TEXAS 75265 |

3 |

TLV2352, TLV2352Y

LinCMOS DUAL LOW-VOLTAGE DIFFERENTIAL COMPARATORS

SLCS011B ± MAY 1992 ± REVISED MARCH 1999

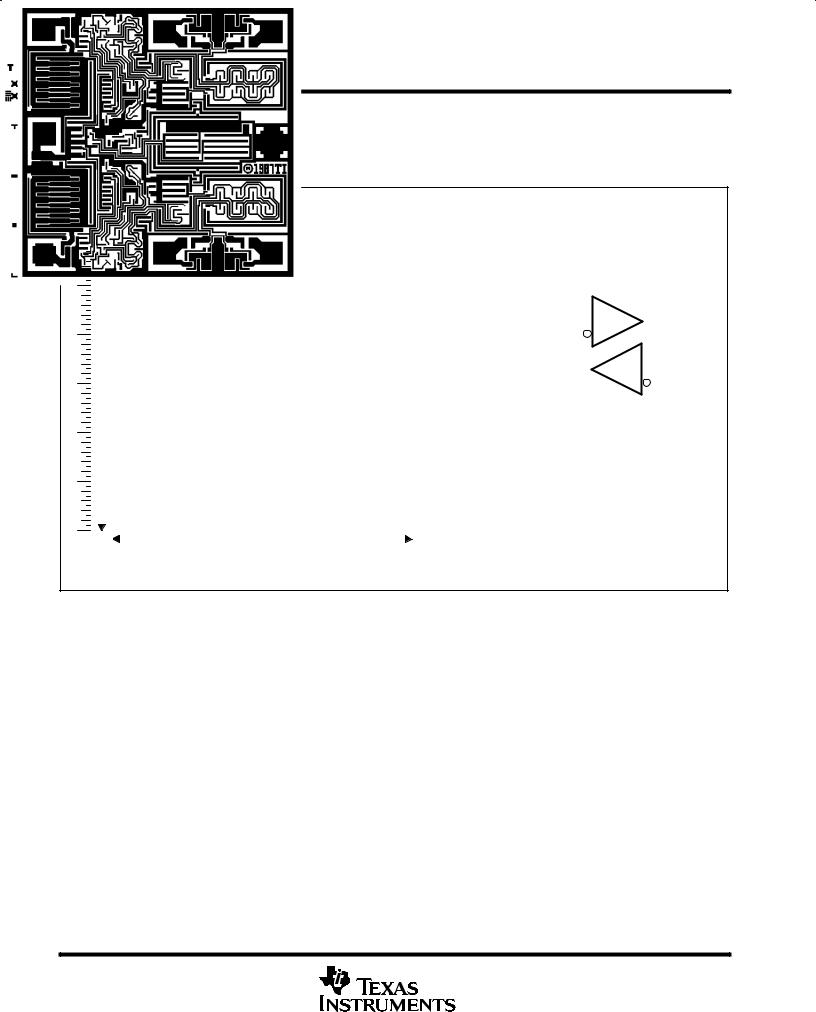

TLV2352Y chip information

These chips, when properly assembled, display characteristics similar to the TLV2352. Thermal compression or ultrasonic bonding may be used on the doped-aluminum bonding pads. This chip can be mounted with conductive epoxy or a gold-silicon preform.

BONDING PAD ASSIGNMENTS

|

|

|

|

|

(7) |

|

(6) |

(5) |

|

|

|

|

|

|

|

|

|

|

|

|

VDD |

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(3) |

|

|

|

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IN + |

|

+ |

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(1) |

|

OUT |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IN ± |

|

(2) |

± |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(5) |

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

+ |

|

|

IN + |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT |

(7) |

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

(8) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

± |

|

(6) |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

57 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(4) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IN ± |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(4) |

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

GND |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CHIP THICKNESS: 15 MILS TYPICAL |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

BONDING PADS: 4 × 4 MILS MINIMUM |

|||||||||||

|

|

|

|

|

(1) |

(2) |

|

(3) |

|

|

|

|

|

|

|

|

TJmax = 150°C |

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TOLERANCES ARE ± 10%. |

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ALL DIMENSIONS ARE IN MILS. |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

57 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN (4) INTERNALLY CONNECTED |

|

|||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TO BACKSIDE OF CHIP. |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

4 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TLV2352, TLV2352Y

LinCMOS DUAL LOW-VOLTAGE DIFFERENTIAL COMPARATORS

SLCS011B ± MAY 1992 ± REVISED MARCH 1999

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)²

Supply voltage, VDD (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . |

. . . . . . . . . . . 8 |

V |

Differential input voltage, VID (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . . . . . . . . ± 8 |

V |

Input voltage range, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . . ±0.3 to 8 |

V |

Output voltage, VO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . . . . . . . . . 8 |

V |

Input current, II . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . . . . . . ± 5 mA |

|

Output current, IO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . . . . . . 20 mA |

|

Duration of output short-circuit current to GND (see Note 3) . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . . . . unlimited |

|

Continuous total power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

See Dissipation Rating Table |

||

Operating free-air temperature range, TA: TLV2352I . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

±40°C to 85°C |

|

TLV2352M . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . |

±55°C to 125°C |

|

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . |

±65°C to 150°C |

|

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: D, P, and PW Packages . . |

. . . . . . . 260°C |

||

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: FK, JG, and U Packages . |

. . . . . . . 300°C |

||

²Stress beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratingsonly, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTES: 1. All voltage values, except differential voltages, are with respect to network ground.

2.Differential voltages are at IN+ with respect to IN ±.

3.Short circuits from outputs to VDD can cause excessive heating and eventual device destruction.

DISSIPATION RATING TABLE

PACKAGE |

TA ≤ 25°C |

DERATING |

TA = 85°C |

TA = 125°C |

|

POWER RATING |

FACTOR |

POWER RATING |

POWER RATING |

||

|

|||||

|

|

|

|

|

|

D |

725 mW |

5.8 mW/°C |

377 mW |

Ð |

|

FK |

1375 mW |

11.0 mW/°C |

715 mW |

275 mW |

|

JG |

1050 mW |

8.4 mW/°C |

546 mW |

210 mW |

|

P |

1000 mW |

8.0 mW/°C |

520 mW |

Ð |

|

PW |

525 mW |

4.2 mW/°C |

273 mW |

Ð |

|

U |

700 mW |

5.5 mW/°C |

370 mW |

150 mW |

|

|

|

|

|

|

recommended operating conditions

|

|

MIN |

MAX |

UNIT |

|

|

|

|

|

|

|

Supply voltage, VDD |

|

2 |

8 |

V |

|

Common-mode input voltage, VIC |

VDD = 3 V |

0 |

1.75 |

V |

|

VDD = 5 V |

0 |

3.75 |

|||

|

|

||||

Operating free-air temperature, TA |

TLV2352I |

± 40 |

85 |

°C |

|

|

|

|

|||

TLV2352M |

± 55 |

125 |

|||

|

|

||||

|

|

|

|

|

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

5 |

TLV2352, TLV2352Y

LinCMOS DUAL LOW-VOLTAGE DIFFERENTIAL COMPARATORS

SLCS011B ± MAY 1992 ± REVISED MARCH 1999

electrical characteristics at specified free-air temperature²

|

|

|

|

|

|

|

TLV2352I |

|

|

|

|

|

|

|

PARAMETER |

TEST CONDITIONS |

T ³ |

|

|

|

|

|

|

|

|

UNIT |

|

|

|

V = 3 V |

|

|

V |

DD |

= 5 V |

|

|||||

|

|

|

|

A |

|

DD |

|

|

|

|

|

|

|

|

|

|

|

|

MIN |

TYP |

MAX |

MIN |

|

TYP |

MAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIO |

Input offset voltage |

VIC = VICRmin, |

See Note 4 |

25°C |

|

1 |

5 |

|

|

|

1 |

5 |

mV |

|

|

|

|

|

|

|

|

|

|||||

Full range |

|

|

7 |

|

|

|

|

7 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IIO |

Input offset current |

|

|

25°C |

|

1 |

|

|

|

|

1 |

|

pA |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

85°C |

|

|

1 |

|

|

|

|

1 |

nA |

||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IIB |

Input bias current |

|

|

25°C |

|

5 |

|

|

|

|

5 |

|

pA |

|

|

85°C |

|

|

2 |

|

|

|

|

2 |

nA |

||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Common-mode input |

|

|

25°C |

0 to 2 |

|

|

0 to 4 |

|

|

|

|

|

VICR |

|

|

|

|

|

|

|

|

|

|

|

V |

|

|

|

|

0 to |

|

|

0 to |

|

|

|

|

|||

voltage range |

|

|

Full range |

|

|

|

|

|

|

||||

|

|

|

1.75 |

|

|

3.75 |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IOH |

High-level output |

VID = 1 V |

|

25°C |

|

0.1 |

|

|

|

|

0.1 |

|

nA |

current |

|

Full range |

|

|

1 |

|

|

|

|

1 |

µA |

||

|

|

|

|

|

|

|

|

|

|||||

VOL |

Low-level output |

VID = ±1 V, |

IOL = 2 mA |

25°C |

|

115 |

300 |

|

|

|

150 |

400 |

mV |

voltage |

Full range |

|

|

600 |

|

|

|

|

700 |

||||

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IOL |

Low-level output |

VID = ± 1 V, |

VOL = 1.5 V |

25°C |

6 |

16 |

|

6 |

|

|

16 |

|

mA |

current |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IDD |

Supply current |

VID = 1 V, |

No load |

25°C |

|

120 |

250 |

|

|

|

140 |

300 |

µA |

Full range |

|

|

350 |

|

|

|

|

400 |

|||||

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

² All characteristics are measured with zero common-mode input voltages unless otherwise noted. ³ Full range is ± 40°C to 85°C. IMPORTANT: See Parameter Measurement Information.

NOTE 4: The offset voltage limits given are the maximum values required to drive the output above 4 V with VDD = 5 V, 2 V with VDD = 3 V, or below 400 mV with a 10-kΩ resistor between the output and VDD. They can be verified by applying the limit value to the input and checking for the appropriate output state.

switching characteristics, VDD = 3 V, TA = 25°C

PARAMETER |

TEST CONDITIONS |

|

TLV2352I |

|

UNIT |

||

|

|

|

|||||

MIN |

TYP |

MAX |

|||||

|

|

|

|

||||

|

|

|

|

|

|

|

|

Response time |

RL = 5.1 kΩ, CL = 15 pF§, See Note 5 |

100-mV input step with 5-mV overdrive |

|

640 |

|

ns |

|

§ CL includes probe and jig capacitance.

NOTE 5: The response time specified is the interval between the input step function and the instant when the output crosses VO = 1 V with VDD = 3 V or VO = 1.4 V with VDD = 5 V.

switching characteristics, VDD = 5 V, TA = 25°C

PARAMETER |

TEST CONDITIONS |

|

TLV2352I |

UNIT |

||

|

|

|||||

MIN |

TYP MAX |

|||||

|

|

|

|

|||

|

|

|

|

|

|

|

Response time |

RL = 5.1 kΩ, CL = 15 pF§, See Note 5 |

100-mV input step with 5-mV overdrive |

|

650 |

ns |

|

|

|

|

||||

TTL-level input step |

|

200 |

||||

|

|

|

|

|||

|

|

|

|

|

|

|

§ CL includes probe and jig capacitance.

NOTE 5: The response time specified is the interval between the input step function and the instant when the output crosses VO = 1 V with VDD = 3 V or VO = 1.4 V with VDD = 5 V.

6 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

Loading...

Loading...