Texas Instruments TLC7524IPWR, TLC7524IPW, TLC7524IN, TLC7524IFNR, TLC7524CDR Datasheet

...

TLC7524C, TLC7524E, TLC7524I 8-BIT MULTIPLYING DIGITAL-TO-ANALOG CONVERTERS

SLAS061C ± SEPTEMBER 1986 ± REVISED NOVEMBER 1998

D Easily Interfaced to Microprocessors |

D, N, OR PW PACKAGE |

D On-Chip Data Latches |

|

|

|

|

(TOP VIEW) |

|

||||

|

|

|

|

|

|

|

|

|

||

D Monotonic Over the Entire A/D Conversion |

OUT1 |

|

1 |

|

16 |

RFB |

|

|||

|

Range |

|

OUT2 |

|

2 |

|

15 |

REF |

|

|

D Segmented High-Order Bits Ensure |

|

GND |

|

3 |

|

14 |

VDD |

|

||

|

Low-Glitch Output |

|

|

DB7 |

|

4 |

|

13 |

WR |

|

D Interchangeable With Analog Devices |

|

DB6 |

|

5 |

|

12 |

CS |

|

||

|

AD7524, PMI PM-7524, and Micro Power |

|

DB5 |

|

6 |

|

11 |

DB0 |

|

|

|

Systems MP7524 |

|

|

DB4 |

|

7 |

|

10 |

DB1 |

|

D Fast Control Signaling for Digital |

|

DB3 |

|

8 |

|

9 |

DB2 |

|

||

|

|

|

|

|

|

|

|

|||

|

Signal-Processor Applications Including |

|

|

|

|

|

|

|

|

|

|

Interface With TMS320 |

|

|

|

FN PACKAGE |

|

||||

D |

CMOS Technology |

|

|

|

|

(TOP VIEW) |

|

|||

|

|

OUT2 |

OUT1 |

NC |

R |

REF |

|

|||

|

|

|

|

|

||||||

|

KEY PERFORMANCE SPECIFICATIONS |

|

|

|

|

|

FB |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Resolution |

8 Bits |

|

|

|

|

|

|

|

|

|

Linearity error |

1/2 LSB Max |

GND |

3 |

|

2 |

1 |

20 19 |

VDD |

|

|

Power dissipation at VDD = 5 V |

5 mW Max |

4 |

|

|

|

|

18 |

||

|

Setting time |

100 ns Max |

DB7 |

5 |

|

|

|

|

17 |

WR |

|

Propagation delay time |

80 ns Max |

NC |

6 |

|

|

|

|

16 |

NC |

description |

|

DB6 |

7 |

|

|

|

|

15 |

CS |

|

|

DB5 |

8 |

|

|

|

|

14 |

DB0 |

||

|

The TLC7524C, TLC7524E, and TLC7524I are |

|

9 |

|

10 11 12 13 |

|

||||

|

|

DB4 |

DB3 |

NC |

DB2 |

DB1 |

|

|||

|

CMOS, 8-bit, digital-to-analog converters (DACs) |

|

|

|||||||

|

|

|

|

|

|

|

|

|

||

|

designed for easy interface to most popular |

NC±No internal connection |

|

|||||||

|

microprocessors. |

|

|

|||||||

The devices are 8-bit, multiplying DACs with input latches and load cycles similar to the write cycles of a random access memory. Segmenting the high-order bits minimizes glitches during changes in the most significant bits, which produce the highest glitch impulse. The devices provide accuracy to 1/2 LSB without the need for thin-film resistors or laser trimming, while dissipating less than 5 mW typically.

Featuring operation from a 5-V to 15-V single supply, these devices interface easily to most microprocessor buses or output ports. The 2- or 4-quadrant multiplying makes these devices an ideal choice for many microprocessor-controlled gain-setting and signal-control applications.

The TLC7524C is characterized for operation from 0°C to 70°C. The TLC7524I is characterized for operation from ±25°C to 85°C. The TLC7524E is characterized for operation from ± 40°C to 85°C.

AVAILABLE OPTIONS

|

|

PACKAGE |

|

|

|

|

|

|

|

|

|

TA |

SMALL OUTLINE |

PLASTIC CHIP CARRIER |

PLASTIC DIP |

SMALL OUTLINE |

|

PLASTIC DIP |

|||||

|

(FN) |

(N) |

(PW) |

||

|

(D) |

||||

|

|

|

|

||

|

|

|

|

|

|

0°C to 70°C |

TLC7524CD |

TLC7524CFN |

TLC7524CN |

TLC7524CPW |

|

|

|

|

|

|

|

± 25°C to 85°C |

TLC7524ID |

TLC7524IFN |

TLC7524IN |

TLC7524IPW |

|

|

|

|

|

|

|

± 40°C to 85°C |

TLC7524ED |

TLC7524EFN |

TLC7524EN |

± |

|

|

|

|

|

|

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1998, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

TLC7524C, TLC7524E, TLC7524I

8-BIT MULTIPLYING DIGITAL-TO-ANALOG CONVERTERS

SLAS061C ± SEPTEMBER 1986 ± REVISED NOVEMBER 1998

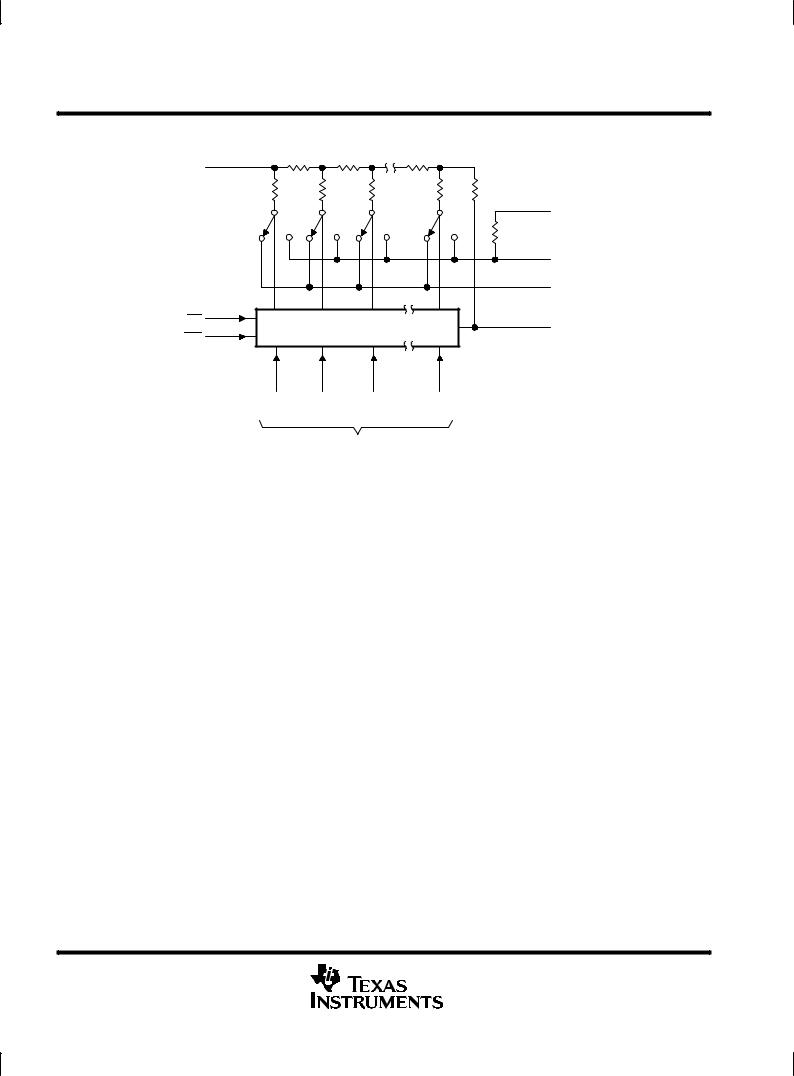

functional block diagram

15 |

R |

R |

|

R |

|

REF |

|

|

|

|

|

|

2R |

2R |

2R |

2R |

2R |

|

|

|

|

|

16 RFB |

|

S-1 |

S-2 |

S-3 |

S-8 |

R |

|

|

|

|

|

|

|

|

|

|

|

1 OUT1 |

|

|

|

|

|

2 OUT2 |

12 |

|

|

|

|

3 GND |

CS 13 |

|

Data Latches |

|

||

WR |

|

|

|

|

|

|

4 |

5 |

6 |

11 |

|

|

DB7 |

DB6 |

DB5 |

DB0 |

|

|

(MSB) |

|

|

(LSB) |

|

|

|

Data Inputs |

|

|

|

Terminal numbers shown are for the D or N package. |

|

||||

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

Supply voltage range, VDD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . ±0.3 V to 16.5 |

V |

Digital input voltage range, VI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

±0.3 V to VDD + 0.3 |

V |

Reference voltage, Vref . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . ± 25 |

V |

Peak digital input current, II . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . 10 μA |

|

Operating free-air temperature range, TA: TLC7524C . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . 0°C to 70°C |

|

TLC7524I . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . ±25°C to 85°C |

|

TLC7524E . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . ±40°C to 85°C |

|

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . ±65°C to 150°C |

|

Case temperature for 10 seconds, TC: FN package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . . 260°C |

|

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: D, N, or PW package |

. . . . . . . . . . . 260°C |

|

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TLC7524C, TLC7524E, TLC7524I 8-BIT MULTIPLYING DIGITAL-TO-ANALOG CONVERTERS

SLAS061C ± SEPTEMBER 1986 ± REVISED NOVEMBER 1998

recommended operating conditions

|

|

|

|

VDD = 5 V |

|

VDD = 15 V |

|

UNIT |

||

|

|

|

|

MIN |

NOM |

MAX |

MIN |

NOM |

MAX |

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

Supply voltage, VDD |

|

4.75 |

5 |

5.25 |

14.5 |

15 |

15.5 |

V |

||

Reference voltage, Vref |

|

|

± 10 |

|

|

± 10 |

|

V |

||

High-level input voltage, VIH |

|

2.4 |

|

|

13.5 |

|

|

V |

||

Low-level input voltage, VIL |

|

|

|

0.8 |

|

|

1.5 |

V |

||

CS setup time, tsu(CS) |

|

40 |

|

|

40 |

|

|

ns |

||

CS hold time, th(CS) |

|

0 |

|

|

0 |

|

|

ns |

||

Data bus input setup time, tsu(D) |

|

25 |

|

|

25 |

|

|

ns |

||

Data bus input hold time, th(D) |

|

10 |

|

|

10 |

|

|

ns |

||

Pulse duration, |

|

low, tw(WR) |

|

40 |

|

|

40 |

|

|

ns |

WR |

|

|

|

|

|

|||||

|

|

|

TLC7524C |

0 |

|

70 |

0 |

|

70 |

|

Operating free-air temperature, TA |

|

|

|

|

|

|

|

°C |

||

TLC7524I |

± 25 |

|

85 |

± 25 |

|

85 |

||||

|

|

|

TLC7524E |

± 40 |

|

85 |

± 40 |

|

85 |

|

|

|

|

|

|

|

|

|

|

|

|

electrical characteristics over recommended operating free-air temperature range, Vref = ±10 V,

OUT1 and OUT2 at GND (unless otherwise noted)

|

PARAMETER |

TEST CONDITIONS |

VDD = 5 V |

|

VDD = 15 V |

UNIT |

||||||||

|

MIN TYP |

MAX |

MIN TYP |

MAX |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IIH |

High-level input current |

VI = VDD |

|

|

|

|

|

10 |

|

10 |

μA |

|||

IIL |

Low-level input current |

VI = 0 |

|

|

|

|

|

± 10 |

|

± 10 |

μA |

|||

|

|

|

|

OUT1 |

DB0±DB7 at 0 V, |

WR, |

|

CS |

at 0 V, |

|

± 400 |

|

± 200 |

|

|

Output leakage |

Vref = ± 10 V |

|

|

|

|

|

|

|

|||||

IIkg |

|

|

|

|

|

|

|

|

|

nA |

||||

current |

|

DB0±DB7 at VDD, |

|

|

|

|

|

|

|

|

||||

OUT2 |

WR, CS at 0 V, |

|

± 400 |

|

± 200 |

|||||||||

|

|

|

|

|||||||||||

|

|

|

|

Vref = ± 10 V |

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IDD |

Supply current |

Quiescent |

DB0±DB7 at VIHmin or VILmax |

|

1 |

|

2 |

mA |

||||||

Standby |

DB0±DB7 at 0 V or VDD |

|

500 |

|

500 |

μA |

||||||||

|

|

|

|

|

|

|||||||||

kSVS |

Supply voltage sensitivity, |

VDD = ± 10% |

|

|

|

|

0.01 |

0.16 |

0.005 |

0.04 |

%FSR/% |

|||

gain/ VDD |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

Ci |

Input capacitance, |

VI = 0 |

|

|

|

|

|

5 |

|

5 |

pF |

|||

|

|

|

|

|

|

|

|

|

|

|||||

DB0±DB7, WR, CS |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

OUT1 |

DB0±DB7 at 0 V, |

|

, |

|

at 0 V |

|

30 |

|

30 |

|

|

|

|

|

|

WR |

CS |

|

|

|

|

|

|||

Co |

Output capacitance |

OUT2 |

|

120 |

|

120 |

pF |

|||||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|||||

OUT1 |

DB0±DB7 at VDD, |

|

, |

|

at 0 V |

|

120 |

|

120 |

|||||

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

WR |

CS |

|

|

|

|

|

|||

|

|

|

|

OUT2 |

|

30 |

|

30 |

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

Reference input impedance |

|

|

|

|

|

5 |

20 |

5 |

20 |

kΩ |

|||

|

(REF to GND) |

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

Loading...

Loading...