Texas instruments TMS320C28341, TMS320C28345, TMS320C28344, TMS320C28346, TMS320C28342 Data Manual

...

TMS320C28346, TMS320C28345, TMS320C28344 TMS320C28343, TMS320C28342, TMS320C28341

Delfino Microcontrollers

Data Manual

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Literature Number: SPRS516B

March 2009 –Revised July 2010

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

SPRS516B –MARCH 2009 –REVISED JULY 2010 www.ti.com

|

|

|

Contents |

|

1 |

TMS320C2834x ( Delfino™ ) MCUs ....................................................................................... |

11 |

||

|

1.1 |

Overview .................................................................................................................... |

11 |

|

|

1.2 |

Features |

.................................................................................................................... |

11 |

|

1.3 |

Getting Started ............................................................................................................. |

12 |

|

2 |

Introduction ...................................................................................................................... |

|

13 |

|

|

2.1 |

Pin Assignments ........................................................................................................... |

16 |

|

|

2.2 |

Signal Descriptions ........................................................................................................ |

24 |

|

3 |

Functional Overview .......................................................................................................... |

35 |

||

|

3.1 |

Memory Maps .............................................................................................................. |

36 |

|

|

3.2 |

Brief Descriptions .......................................................................................................... |

41 |

|

|

|

3.2.1 |

C28x CPU ....................................................................................................... |

41 |

|

|

3.2.2 |

Memory Bus (Harvard Bus Architecture) .................................................................... |

41 |

|

|

3.2.3 |

Peripheral Bus .................................................................................................. |

41 |

|

|

3.2.4 |

Real-Time JTAG and Analysis ................................................................................ |

42 |

|

|

3.2.5 |

External Interface (XINTF) .................................................................................... |

42 |

|

|

3.2.6 |

M0, M1 SARAMs ............................................................................................... |

42 |

|

|

3.2.7 |

L0, L1, L2, L3, L4, L5, L6, L7 , H0, H1, H2, H3, H4, H5 SARAMs ....................................... |

42 |

|

|

3.2.8 |

Boot ROM ....................................................................................................... |

43 |

|

|

3.2.9 |

Security .......................................................................................................... |

43 |

|

|

3.2.10 |

Peripheral Interrupt Expansion (PIE) Block ................................................................. |

44 |

|

|

3.2.11 |

External Interrupts (XINT1–XINT7, XNMI) .................................................................. |

44 |

|

|

3.2.12 |

Oscillator and PLL .............................................................................................. |

44 |

|

|

3.2.13 |

Watchdog ........................................................................................................ |

44 |

|

|

3.2.14 |

Peripheral Clocking ............................................................................................. |

44 |

|

|

3.2.15 |

Low-Power Modes .............................................................................................. |

44 |

|

|

3.2.16 |

Peripheral Frames 0, 1, 2, 3 (PFn) ........................................................................... |

45 |

|

|

3.2.17 |

General-Purpose Input/Output (GPIO) Multiplexer ......................................................... |

45 |

|

|

3.2.18 |

32-Bit CPU-Timers (0, 1, 2) ................................................................................... |

45 |

|

|

3.2.19 |

Control Peripherals ............................................................................................. |

46 |

|

|

3.2.20 |

Serial Port Peripherals ......................................................................................... |

46 |

|

3.3 |

Register Map ............................................................................................................... |

47 |

|

|

3.4 |

Device Emulation Registers .............................................................................................. |

48 |

|

|

3.5 |

Interrupts .................................................................................................................... |

49 |

|

|

|

3.5.1 |

External Interrupts .............................................................................................. |

53 |

|

3.6 |

System Control ............................................................................................................ |

54 |

|

|

|

3.6.1 |

OSC and PLL Block ............................................................................................ |

55 |

|

|

|

3.6.1.1 External Reference Oscillator Clock Option .................................................... |

57 |

|

|

|

3.6.1.2 PLL-Based Clock Module ......................................................................... |

58 |

|

|

|

3.6.1.3 Loss of Input Clock ................................................................................ |

59 |

|

|

3.6.2 |

Watchdog Block ................................................................................................. |

60 |

|

3.7 |

Low-Power Modes Block ................................................................................................. |

61 |

|

4 |

Peripherals ....................................................................................................................... |

|

62 |

|

|

4.1 |

DMA Overview ............................................................................................................. |

62 |

|

|

4.2 |

32-Bit CPU-Timers 0/1/2 ................................................................................................. |

64 |

|

|

4.3 |

Enhanced PWM Modules (ePWM1/2/3/4/5/6 /7/8/9) ................................................................. |

66 |

|

2 |

Contents |

Copyright © 2009–2010, Texas Instruments Incorporated |

|

|

|

TMS320C28346, TMS320C28345, TMS320C28344 |

||

|

|

|

TMS320C28343, TMS320C28342, TMS320C28341 |

||

www.ti.com |

|

|

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

||

|

4.4 |

High-Resolution PWM (HRPWM) ....................................................................................... |

|

70 |

|

|

4.5 |

Enhanced CAP Modules (eCAP1/2/3/4/5/6) ........................................................................... |

|

71 |

|

|

4.6 |

Enhanced QEP Modules (eQEP1/2 /3) ................................................................................. |

|

73 |

|

|

4.7 |

External ADC Interface ................................................................................................... |

|

75 |

|

|

4.8 |

Multichannel Buffered Serial Port (McBSP) Module .................................................................. |

|

76 |

|

|

4.9 |

Enhanced Controller Area Network (eCAN) Modules (eCAN-A and eCAN-B) |

.................................... 79 |

||

|

4.10 |

Serial Communications Interface (SCI) Modules (SCI-A, SCI-B, SCI-C) |

.......................................... |

85 |

|

|

4.11 |

Serial Peripheral Interface (SPI) Module (SPI-A , SPI-D) ............................................................ |

|

89 |

|

|

4.12 |

Inter-Integrated Circuit (I2C) ............................................................................................. |

|

92 |

|

|

4.13 |

GPIO MUX ................................................................................................................. |

|

93 |

|

|

4.14 |

External Interface (XINTF) .............................................................................................. |

|

100 |

|

5 |

Device Support ................................................................................................................ |

|

102 |

||

|

5.1 |

Device and Development Support Tool Nomenclature ............................................................. |

|

102 |

|

|

5.2 |

Documentation Support ................................................................................................. |

|

104 |

|

6 |

Electrical Specifications ................................................................................................... |

|

108 |

||

|

6.1 |

Absolute Maximum Ratings ............................................................................................. |

|

108 |

|

|

6.2 |

Recommended Operating Conditions ................................................................................. |

|

109 |

|

|

6.3 |

Electrical Characteristics ................................................................................................ |

|

109 |

|

|

6.4 |

Current Consumption .................................................................................................... |

|

110 |

|

|

|

6.4.1 |

Reducing Current Consumption ............................................................................. |

|

112 |

|

6.5 |

Thermal Design Considerations ........................................................................................ |

|

114 |

|

|

6.6 |

Emulator Connection Without Signal Buffering for the MCU ....................................................... |

|

114 |

|

|

6.7 |

Timing Parameter Symbology .......................................................................................... |

|

115 |

|

|

|

6.7.1 |

General Notes on Timing Parameters ...................................................................... |

|

115 |

|

|

6.7.2 |

Test Load Circuit .............................................................................................. |

|

115 |

|

|

6.7.3 |

Device Clock Table ........................................................................................... |

|

116 |

|

6.8 |

Clock Requirements and Characteristics ............................................................................. |

|

118 |

|

|

6.9 |

Power Sequencing ....................................................................................................... |

|

119 |

|

|

|

6.9.1 |

Power Management and Supervisory Circuit Solutions .................................................. |

|

120 |

|

6.10 |

General-Purpose Input/Output (GPIO) ................................................................................ |

|

123 |

|

|

|

6.10.1 |

GPIO - Output Timing ........................................................................................ |

|

123 |

|

|

6.10.2 |

GPIO - Input Timing .......................................................................................... |

|

124 |

|

|

6.10.3 |

Sampling Window Width for Input Signals ................................................................. |

|

125 |

|

|

6.10.4 |

Low-Power Mode Wakeup Timing .......................................................................... |

|

126 |

|

6.11 |

Enhanced Control Peripherals ......................................................................................... |

|

129 |

|

|

|

6.11.1 |

Enhanced Pulse Width Modulator (ePWM) Timing ....................................................... |

|

129 |

|

|

6.11.2 |

Trip-Zone Input Timing ....................................................................................... |

|

129 |

|

|

6.11.3 |

Enhanced Capture (eCAP) Timing ......................................................................... |

|

130 |

|

|

6.11.4 |

Enhanced Quadrature Encoder Pulse (eQEP) Timing ................................................... |

|

130 |

|

|

6.11.5 |

ADC Start-of-Conversion Timing ............................................................................ |

|

131 |

|

6.12 |

External Interrupt Timing ................................................................................................ |

|

131 |

|

|

6.13 |

I2C Electrical Specification and Timing ............................................................................... |

|

132 |

|

|

6.14 |

Serial Peripheral Interface (SPI) Timing .............................................................................. |

|

132 |

|

|

|

6.14.1 |

Master Mode Timing .......................................................................................... |

|

132 |

|

|

6.14.2 |

SPI Slave Mode Timing ...................................................................................... |

|

137 |

|

6.15 |

External Interface (XINTF) Timing ..................................................................................... |

|

140 |

|

|

|

6.15.1 |

USEREADY = 0 ............................................................................................... |

|

140 |

Copyright © 2009–2010, Texas Instruments Incorporated |

Contents |

3 |

TMS320C28346, TMS320C28345, TMS320C28344 |

|

|

TMS320C28343, TMS320C28342, TMS320C28341 |

|

|

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

www.ti.com |

|

|

6.15.2 Synchronous Mode (USEREADY = 1, READYMODE = 0) ............................................. |

141 |

|

6.15.3 Asynchronous Mode (USEREADY = 1, READYMODE = 1) ............................................ |

142 |

|

6.15.4 XINTF Signal Alignment to XCLKOUT ..................................................................... |

144 |

|

6.15.5 External Interface Read Timing ............................................................................. |

145 |

|

6.15.6 External Interface Write Timing ............................................................................. |

147 |

|

6.15.7 External Interface Ready-on-Read Timing With One External Wait State ............................ |

149 |

|

6.15.8 External Interface Ready-on-Write Timing With One External Wait State ............................. |

152 |

|

6.15.9 XHOLD and XHOLDA Timing ............................................................................... |

155 |

|

6.16 Multichannel Buffered Serial Port (McBSP) Timing ................................................................. |

157 |

|

6.16.1 McBSP Transmit and Receive Timing ...................................................................... |

157 |

|

6.16.2 McBSP as SPI Master or Slave Timing .................................................................... |

160 |

7 |

Revision History .............................................................................................................. |

164 |

8 |

Thermal/Mechanical Data .................................................................................................. |

165 |

4 |

Contents |

Copyright © 2009–2010, Texas Instruments Incorporated |

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

www.ti.com SPRS516B –MARCH 2009 –REVISED JULY 2010

List of Figures

2-1 |

C2834x 179-Ball ZHH MicroStar BGA™ |

Upper Left Quadrant (Bottom VIew) .......................................... |

17 |

2-2 |

C2834x 179-Ball ZHH MicroStar BGA™ |

Upper Right Quadrant (Bottom View)......................................... |

18 |

2-3 |

C2834x 179-Ball ZHH MicroStar BGA™ |

Lower Left Quadrant (Bottom View)........................................... |

19 |

2-4 |

C2834x 179-Ball ZHH MicroStar BGA™ |

Lower Right Quadrant (Bottom View)......................................... |

20 |

2-5 |

C2834x 256-Ball ZFE Plastic BGA Upper Left Quadrant (Bottom View) ................................................. |

21 |

|

2-6 |

C2834x 256-Ball ZFE Plastic BGA Upper Right Quadrant (Bottom View) ............................................... |

22 |

|

2-7 |

C2834x 256-Ball ZFE Plastic BGA Lower Left Quadrant (Bottom View) ................................................. |

23 |

|

2-8 |

C2834x 256-Ball ZFE Plastic BGA Lower Right Quadrant (Bottom View) ............................................... |

23 |

|

3-1 |

Functional Block Diagram ...................................................................................................... |

|

36 |

3-2 |

C28346/C28345 Memory Map ................................................................................................. |

|

38 |

3-3 |

C28344/C28343 Memory Map ................................................................................................. |

|

39 |

3-4 |

C28342, C28341 Memory Map ................................................................................................ |

|

40 |

3-5 |

External and PIE Interrupt Sources ............................................................................................ |

|

50 |

3-6 |

External Interrupts................................................................................................................ |

|

50 |

3-7 |

Multiplexing of Interrupts Using the PIE Block ............................................................................... |

51 |

|

3-8 |

Clock and Reset Domains ...................................................................................................... |

|

54 |

3-9 |

OSC and PLL Block Diagram................................................................................................... |

|

55 |

3-10 |

Using a 3.3-V External Oscillator............................................................................................... |

|

56 |

3-11 |

Using a 1. 8-V External Oscillator.............................................................................................. |

|

56 |

3-12 |

Using the Internal Oscillator .................................................................................................... |

|

56 |

3-13 |

Watchdog Module ................................................................................................................ |

|

60 |

4-1 |

DMA Functional Block Diagram ................................................................................................ |

|

63 |

4-2 |

CPU-Timers ....................................................................................................................... |

|

64 |

4-3 |

CPU-Timer Interrupt Signals and Output Signal ............................................................................. |

64 |

|

4-4 |

Generation of SOC Pulses to the External ADC Module ................................................................... |

66 |

|

4-5 |

ePWM Submodules Showing Critical Internal Signal Interconnections ................................................... |

69 |

|

4-6 |

eCAP Functional Block Diagram ............................................................................................... |

|

71 |

4-7 |

eQEP Functional Block Diagram ............................................................................................... |

|

73 |

4-8 |

External ADC Interface .......................................................................................................... |

|

75 |

4-9 |

McBSP Module .................................................................................................................. |

|

77 |

4-10 |

eCAN Block Diagram and Interface Circuit ................................................................................... |

80 |

|

4-11 |

eCAN-A Memory Map ........................................................................................................... |

|

82 |

4-12 |

eCAN-B Memory Map ........................................................................................................... |

|

83 |

4-13 |

Serial Communications Interface (SCI) Module Block Diagram............................................................ |

88 |

|

4-14 |

SPI Module Block Diagram (Slave Mode) .................................................................................... |

91 |

|

4-15 |

I2C Peripheral Module Interfaces .............................................................................................. |

|

92 |

4-16 |

GPIO MUX Block Diagram ...................................................................................................... |

|

94 |

4-17 |

Qualification Using Sampling Window......................................................................................... |

|

99 |

4-18 |

External Interface Block Diagram............................................................................................. |

|

100 |

4-19 |

Typical 16-bit Data Bus XINTF Connections................................................................................ |

101 |

|

4-20 |

Typical 32-bit Data Bus XINTF Connections................................................................................ |

101 |

|

5-1 |

Example of C2834x Device Nomenclature .................................................................................. |

103 |

|

6-1 |

Temperature Versus Leakage Current (Typical)............................................................................ |

112 |

|

6-2 |

Emulator Connection Without Signal Buffering for the MCU ............................................................. |

114 |

|

6-3 |

3.3-V Test Load Circuit......................................................................................................... |

|

115 |

6-4 |

Clock Timing..................................................................................................................... |

|

118 |

6-5 |

Power-on Reset ................................................................................................................. |

|

121 |

|

|

|

|

Copyright © 2009–2010, Texas Instruments Incorporated |

List of Figures |

5 |

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

www.ti.com |

||||

6-6 |

Warm Reset ..................................................................................................................... |

122 |

|||

6-7 |

Example of Effect of Writing Into PLLCR Register ......................................................................... |

123 |

|||

6-8 |

General-Purpose Output Timing .............................................................................................. |

124 |

|||

6-9 |

Sampling Mode ................................................................................................................. |

124 |

|||

6-10 |

General-Purpose Input Timing ................................................................................................ |

125 |

|||

6-11 |

IDLE Entry and Exit Timing.................................................................................................... |

126 |

|||

6-12 |

STANDBY Entry and Exit Timing Diagram .................................................................................. |

127 |

|||

6-13 |

HALT Wake-Up Using GPIOn................................................................................................. |

128 |

|||

6-14 |

PWM Hi-Z Characteristics ..................................................................................................... |

129 |

|||

6-15 |

|

or |

|

Timing |

131 |

ADCSOCAO |

ADCSOCBO |

||||

6-16 |

External Interrupt Timing....................................................................................................... |

131 |

|||

6-17 |

SPI Master Mode External Timing (Clock Phase = 0) ..................................................................... |

134 |

|||

6-18 |

SPI Master Mode External Timing (Clock Phase = 1) ..................................................................... |

136 |

|||

6-19 |

SPI Slave Mode External Timing (Clock Phase = 0)....................................................................... |

138 |

|||

6-20 |

SPI Slave Mode External Timing (Clock Phase = 1)....................................................................... |

139 |

|||

6-21 |

Relationship Between XTIMCLK and SYSCLKOUT ....................................................................... |

143 |

|||

6-22 |

Example Read Access ......................................................................................................... |

146 |

|||

6-23 |

Example Write Access ......................................................................................................... |

148 |

|||

6-24 |

Example Read With Synchronous XREADY Access ...................................................................... |

150 |

|||

6-25 |

Example Read With Asynchronous XREADY Access ..................................................................... |

151 |

|||

6-26 |

Write With Synchronous XREADY Access .................................................................................. |

153 |

|||

6-27 |

Write With Asynchronous XREADY Access ................................................................................ |

154 |

|||

6-28 |

External Interface Hold Waveform............................................................................................ |

156 |

|||

6-29 |

McBSP Receive Timing ........................................................................................................ |

159 |

|||

6-30 |

McBSP Transmit Timing ....................................................................................................... |

159 |

|||

6-31 |

McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 0 ................................................... |

160 |

|||

6-32 |

McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 0 ................................................... |

161 |

|||

6-33 |

McBSP Timing as SPI Master or Slave: CLKSTP = 10b, CLKXP = 1 ................................................... |

162 |

|||

6-34 |

McBSP Timing as SPI Master or Slave: CLKSTP = 11b, CLKXP = 1 ................................................... |

163 |

|||

6 |

List of Figures |

Copyright © 2009–2010, Texas Instruments Incorporated |

|

TMS320C28346, TMS320C28345, TMS320C28344 |

||

|

TMS320C28343, TMS320C28342, TMS320C28341 |

||

www.ti.com |

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

||

|

List of Tables |

|

|

2-1 |

C2834x Hardware Features .................................................................................................... |

|

14 |

2-2 |

Signal Descriptions............................................................................................................... |

|

24 |

3-1 |

Wait-states ........................................................................................................................ |

|

40 |

3-2 |

Boot Mode Selection............................................................................................................. |

|

43 |

3-3 |

Peripheral Frame 0 Registers .................................................................................................. |

|

47 |

3-4 |

Peripheral Frame 1 Registers .................................................................................................. |

|

47 |

3-5 |

Peripheral Frame 2 Registers .................................................................................................. |

|

48 |

3-6 |

Peripheral Frame 3 Registers .................................................................................................. |

|

48 |

3-7 |

Device Emulation Registers..................................................................................................... |

|

48 |

3-8 |

PIE Peripheral Interrupts ....................................................................................................... |

|

51 |

3-9 |

PIE Configuration and Control Registers...................................................................................... |

|

52 |

3-10 |

External Interrupt Registers ..................................................................................................... |

|

53 |

3-11 |

PLL, Clocking, Watchdog, and Low-Power Mode Registers ............................................................... |

|

55 |

3-12 |

PLL Settings ...................................................................................................................... |

|

58 |

3-13 |

CLKIN Divide Options ........................................................................................................... |

|

58 |

3-14 |

Possible PLL Configuration Modes ............................................................................................ |

|

59 |

3-15 |

Low-Power Modes ............................................................................................................... |

|

61 |

4-1 |

CPU-Timers 0, 1, 2 Configuration and Control Registers................................................................... |

|

65 |

4-2 |

ePWM1-4 Control and Status Registers ...................................................................................... |

|

67 |

4-3 |

ePWM5-9 Control and Status Registers ...................................................................................... |

|

68 |

4-4 |

eCAP Control and Status Registers ........................................................................................... |

|

72 |

4-5 |

eQEP Control and Status Registers ........................................................................................... |

|

74 |

4-6 |

External ADC Interface Registers ............................................................................................. |

|

75 |

4-7 |

McBSP Register Summary...................................................................................................... |

|

78 |

4-8 |

3.3-V eCAN Transceivers ...................................................................................................... |

|

81 |

4-9 |

CAN Register Map .............................................................................................................. |

|

84 |

4-10 |

SCI-A Registers .................................................................................................................. |

|

86 |

4-11 |

SCI-B Registers .................................................................................................................. |

|

86 |

4-12 |

SCI-C Registers ................................................................................................................. |

|

87 |

4-13 |

SPI-A Registers................................................................................................................... |

|

90 |

4-14 |

SPI-D Registers .................................................................................................................. |

|

90 |

4-15 |

I2C-A Registers................................................................................................................... |

|

93 |

4-16 |

GPIO Registers .................................................................................................................. |

|

95 |

4-17 |

GPIO-A Mux Peripheral Selection Matrix .................................................................................... |

|

96 |

4-18 |

GPIO-B Mux Peripheral Selection Matrix .................................................................................... |

|

97 |

4-19 |

GPIO-C Mux Peripheral Selection Matrix .................................................................................... |

|

98 |

4-20 |

XINTF Configuration and Control Register Mapping ....................................................................... |

|

101 |

5-1 |

TMS320x2834x Delfino Peripheral Selection Guide ....................................................................... |

|

104 |

6-1 |

TMS320C28346/C28344 Current Consumption by Power-Supply Pins at 300-MHz SYSCLKOUT................. |

110 |

|

6-2 |

TMS320C28345/C28343 Current Consumption by Power-Supply Pins at 200-MHz SYSCLKOUT................. |

111 |

|

6-3 |

Typical Current Consumption by Various Peripherals .................................................................... |

|

113 |

6-4 |

Clocking and Nomenclature (300-MHz Devices) ........................................................................... |

|

116 |

6-5 |

Clocking and Nomenclature (200-MHz Devices) ........................................................................... |

|

117 |

6-6 |

XCLKIN/X1 Timing Requirements – PLL Enabled ......................................................................... |

|

118 |

6-7 |

XCLKIN/X1 Timing Requirements – PLL Disabled ........................................................................ |

|

118 |

6-8 |

XCLKOUT Switching Characteristics (PLL Bypassed or Enabled) ...................................................... |

|

118 |

6-9 |

Power Management and Supervisory Circuit Solutions ................................................................... |

|

120 |

|

|

|

|

Copyright © 2009–2010, Texas Instruments Incorporated |

List of Tables |

7 |

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

www.ti.com |

||||||

6-10 |

Reset |

|

|

|

Timing Requirements |

122 |

|

(XRS) |

|||||||

6-11 |

General-Purpose Output Switching Characteristics ........................................................................ |

123 |

|||||

6-12 |

General-Purpose Input Timing Requirements .............................................................................. |

124 |

|||||

6-13 |

IDLE Mode Timing Requirements ........................................................................................... |

126 |

|||||

6-14 |

IDLE Mode Switching Characteristics ....................................................................................... |

126 |

|||||

6-15 |

STANDBY Mode Timing Requirements ..................................................................................... |

127 |

|||||

6-16 |

STANDBY Mode Switching Characteristics ................................................................................ |

127 |

|||||

6-17 |

HALT Mode Timing Requirements ........................................................................................... |

128 |

|||||

6-18 |

HALT Mode Switching Characteristics ...................................................................................... |

128 |

|||||

6-19 |

ePWM Timing Requirements ................................................................................................. |

129 |

|||||

6-20 |

ePWM Switching Characteristics ............................................................................................ |

129 |

|||||

6-21 |

Trip-Zone Input Timing Requirements ...................................................................................... |

129 |

|||||

6-22 |

High-Resolution PWM Characteristics at SYSCLKOUT = ( 150– 300 MHz) ........................................... |

130 |

|||||

6-23 |

Enhanced Capture (eCAP) Timing Requirement .......................................................................... |

130 |

|||||

6-24 |

eCAP Switching Characteristics ............................................................................................. |

130 |

|||||

6-25 |

Enhanced Quadrature Encoder Pulse (eQEP) Timing Requirements .................................................. |

130 |

|||||

6-26 |

eQEP Switching Characteristics ............................................................................................. |

130 |

|||||

6-27 |

External ADC Start-of-Conversion Switching Characteristics............................................................. |

131 |

|||||

6-28 |

External Interrupt Timing Requirements .................................................................................... |

131 |

|||||

6-29 |

External Interrupt Switching Characteristics ................................................................................ |

131 |

|||||

6-30 |

I2C Timing ...................................................................................................................... |

132 |

|||||

6-31 |

SPI Master Mode External Timing (Clock Phase = 0) .................................................................... |

133 |

|||||

6-32 |

SPI Master Mode External Timing (Clock Phase = 1) .................................................................... |

135 |

|||||

6-33 |

SPI Slave Mode External Timing (Clock Phase = 0) ...................................................................... |

137 |

|||||

6-34 |

SPI Slave Mode External Timing (Clock Phase = 1) ...................................................................... |

139 |

|||||

6-35 |

Relationship Between Parameters Configured in XTIMING and Duration of Pulse ................................... |

140 |

|||||

6-36 |

XINTF Clock Configurations for SYSCLKOUT = 300 MHz ............................................................... |

143 |

|||||

6-37 |

External Interface Read Timing Requirements ............................................................................. |

145 |

|||||

6-38 |

External Interface Read Switching Characteristics ......................................................................... |

145 |

|||||

6-39 |

External Interface Write Switching Characteristics ......................................................................... |

147 |

|||||

6-40 |

External Interface Read Switching Characteristics (Ready-on-Read, 1 Wait State) ................................... |

149 |

|||||

6-41 |

External Interface Read Timing Requirements (Ready-on-Read, 1 Wait State) ....................................... |

149 |

|||||

6-42 |

Synchronous XREADY Timing Requirements (Ready-on-Read, 1 Wait State) ....................................... |

149 |

|||||

6-43 |

Asynchronous XREADY Timing Requirements (Ready-on-Read, 1 Wait State)....................................... |

149 |

|||||

6-44 |

External Interface Write Switching Characteristics (Ready-on-Write, 1 Wait State) ................................... |

152 |

|||||

6-45 |

Synchronous XREADY Timing Requirements (Ready-on-Write, 1 Wait State) ....................................... |

152 |

|||||

6-46 |

Asynchronous XREADY Timing Requirements (Ready-on-Write, 1 Wait State) ...................................... |

152 |

|||||

6-47 |

|

|

|

|

|

|

155 |

XHOLD/XHOLDA Timing Requirements .................................................................................... |

|||||||

6-48 |

McBSP Timing Requirements ................................................................................................ |

157 |

|||||

6-49 |

McBSP Switching Characteristics ........................................................................................... |

158 |

|||||

6-50 |

McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 0) ................................ |

160 |

|||||

6-51 |

McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 0)............................ |

160 |

|||||

6-52 |

McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 0) ................................ |

161 |

|||||

6-53 |

McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 0)............................ |

161 |

|||||

6-54 |

McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 10b, CLKXP = 1) ................................ |

162 |

|||||

6-55 |

McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 10b, CLKXP = 1)............................ |

162 |

|||||

6-56 |

McBSP as SPI Master or Slave Timing Requirements (CLKSTP = 11b, CLKXP = 1) ................................ |

163 |

|||||

6-57 |

McBSP as SPI Master or Slave Switching Characteristics (CLKSTP = 11b, CLKXP = 1) ........................... |

163 |

|||||

8 |

List of Tables |

Copyright © 2009–2010, Texas Instruments Incorporated |

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

www.ti.com |

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

8-1 Thermal Model 179-Ball ZHH Results

8-2 Thermal Model 256-Ball ZFE Results

.......................................................................................

.......................................................................................

165

165

Copyright © 2009–2010, Texas Instruments Incorporated |

List of Tables |

9 |

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

www.ti.com |

10 |

List of Tables |

Copyright © 2009–2010, Texas Instruments Incorporated |

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

www.ti.com |

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

Delfino Microcontrollers

Check for Samples: TMS320C28346, TMS320C28345, TMS320C28344, TMS320C28343, TMS320C28342, TMS320C28341

1 TMS320C2834x ( Delfino™ ) MCUs

1.1Overview

The TMS320C2834x (C2834x) Delfino™ microcontroller (MCU) devices build on TI'sexisting F2833x high-performance floating-point microcontrollers. The C2834x delivers up to 300 MHz of floating-point performance, and has up to 516KB of on-chip RAM. Designed for real-time control applications, the C2834x is based on the C28x™ core, making it code-compatible with all C28x microcontrollers. The on-chip peripherals and low-latency core make the C2834x an excellent solution for performance-hungry real-time control applications.

1.2Features

•High-Performance Static CMOS Technology

–Up to 300 MHz (3.33-ns Cycle Time)

–1.1-V/1.2-V Core, 3.3-V I/O , 1.8-V PLL/Oscillator Design

•High-Performance 32-Bit CPU (TMS320C28x)

–IEEE-754 Single-Precision Floating-Point Unit (FPU)

–16 x 16 and 32 x 32 MAC Operations

–16 x 16 Dual MAC

–Harvard Bus Architecture

–Fast Interrupt Response and Processing

–Code-Efficient (in C/C++ and Assembly)

•Six-Channel DMA Controller (for McBSP, XINTF, and SARAM)

•16-Bit or 32-Bit External Interface (XINTF)

–Over 2M x 16 Address Reach

•On-Chip Memory

–Up to 258K x 16 SARAM

–8K x 16 Boot ROM

•Clock and System Control

–Dynamic PLL Ratio Changes Supported

–On-Chip Oscillator

–Watchdog Timer Module

•Peripheral Interrupt Expansion (PIE) Block That Supports All 64 Peripheral Interrupts

•Enhanced Control Peripherals

–Eighteen Enhanced Pulse Width Modulator (ePWM) Outputs

•Dedicated 16-Bit Time-Based Counter With Period and Frequency Control

•Single-Edge, Dual-Edge Symmetric, or Dual-Edge Asymmetric Outputs

•Dead-Band Generation

•PWM Chopping by High-Frequency Carrier

•Trip Zone Input

•Up to 9 HRPWM Outputs With 55-ps MEP Resolution at VDD = 1.1 V (65 ps at 1.2 V)

–Six 32-Bit Enhanced Capture (eCAP) Modules

•Configurable as 3 Capture Inputs or 3 Auxiliary Pulse Width Modulator Outputs

•Single-Shot Capture of up to Four Event Time-Stamps

–Three 32-Bit Quadrature Encoder Pulse (QEP) Modules

–Six 32-Bit Timers/Nine 16-Bit Timers

•Three 32-Bit CPU Timers

•Serial Port Peripherals

–Up to 2 CAN Modules

–Up to 3 SCI (UART) Modules

–Up to 2 McBSP Modules (Configurable as SPI)

–Up to 2 SPI Module s

–One Inter-Integrated-Circuit (I2C) Bus

•External ADC Interface

•Up to 88 Individually Programmable, Multiplexed GPIO Pins With Input Filtering

•Advanced Emulation Features

–Analysis and Breakpoint Functions

–Real-Time Debug via Hardware

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Delfino, MicroStar BGA, C28x, TMS320C54x, TMS320C55x, Code Composer Studio, TMS320C28x are trademarks of Texas Instruments. 1-Wire is a registered trademark of Maxim Integrated Products, Inc.

All other trademarks are the property of their respective owners.

PRODUCTION DATA information is |

current as of publication date. |

Copyright © 2009–2010, Texas Instruments Incorporated |

Products conform to specifications |

per the terms of the Texas |

|

Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

|

www.ti.com |

|

• 2834x Package Options: |

• Community Resources |

||

– |

MicroStar BGA™ (ZHH) |

– |

TI E2E Community |

– |

Plastic BGA (ZFE) |

– |

TI Embedded Processors Wiki |

1.3Getting Started

This section gives a brief overview of the steps to take when first developing for a C28x device. For more detail on each of these steps, see the following:

•Getting Started With TMS320C28x Digital Signal Controllers (literature number SPRAAM0).

•C2000 Getting Started Website (http://www.ti.com/c2000getstarted)

•TMS320F28x Development and Experimenter'sKits (http://www.ti.com/f28xkits)

12 |

TMS320C2834x ( Delfino™ ) MCUs |

Copyright © 2009–2010, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320C28346, TMS320C28345, TMS320C28344 TMS320C28343, TMS320C28342,

TMS320C28341

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

www.ti.com |

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

2 Introduction

The TMS320C28346, TMS320C28345, TMS320C28344, TMS320C28343, TMS320C28342, and TMS320C28341 devices, members of the Delfino™ MCU generation, are highly integrated, high-performance solutions for demanding control applications.

Throughout this document, the devices are abbreviated as C28346, C28345, C28344, C28343, C28342, and C28341, respectively. Table 2-1 provides a summary of features for each device.

Copyright © 2009–2010, Texas Instruments Incorporated |

Introduction |

13 |

Submit Documentation Feedback

Product Folder Link(s): TMS320C28346, TMS320C28345, TMS320C28344 TMS320C28343, TMS320C28342,

TMS320C28341

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

|

|

|

|

|

|

|

|

|

|

|

www.ti.com |

||

|

|

|

Table 2-1. C2834x Hardware Features |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

FEATURE |

TYPE(1) |

C28346 |

|

C28345 |

C28344 |

|

C28343 |

C28342 |

|

C28341 |

||||

|

|

(300 MHz) |

(200 MHz) |

(300 MHz) |

(200 MHz) |

(300 MHz) |

(200 MHz) |

|||||||

Package Type |

– |

256-Ball ZFE |

256-Ball ZFE |

|

179-Ball ZHH |

256-Ball ZFE |

256-Ball ZFE |

|

179-Ball ZHH |

256-Ball ZFE |

256-Ball ZFE |

|

179-Ball ZHH |

|

PBGA(2) |

PBGA(2) |

|

BGA |

PBGA(2) |

PBGA(2) |

|

BGA |

PBGA(2) |

PBGA(2) |

|

BGA |

|||

Instruction cycle |

– |

3.33 ns |

|

5 ns |

3.33 ns |

|

5 ns |

3.33 ns |

|

5 ns |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Floating-point unit |

– |

Yes |

|

Yes |

Yes |

|

Yes |

Yes |

|

Yes |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Single-access RAM (SARAM) (16-bit word) |

– |

258K |

|

258K |

130K |

|

130K |

98K |

|

98K |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Code security for on-chip SARAM blocks |

– |

No(3) |

|

No(3) |

No(3) |

|

No(3) |

No(3) |

|

No(3) |

||||

Boot ROM (8K x 16) |

– |

Yes |

|

Yes |

Yes |

|

Yes |

Yes |

|

Yes |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

16-/32-bit External Interface (XINTF) |

1 |

Yes |

|

Yes |

Yes |

|

Yes |

Yes |

|

Yes |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6-channel Direct Memory Access (DMA) |

0 |

Yes |

|

Yes |

Yes |

|

Yes |

Yes |

|

Yes |

||||

|

|

|

|

|

|

|

|

|

|

|

||||

PWM outputs |

0 |

ePWM1/2/3/ |

ePWM1/2/3/ |

ePWM1/2/3/ |

ePWM1/2/3/ |

ePWM1/2/3/ |

ePWM1/2/3/ |

|||||||

4/5/6/7/8/9 |

4/5/6/7/8/9 |

4/5/6/7/8/9 |

4/5/6/7/8/9 |

4/5/6 |

|

4/5/6 |

||||||||

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

ePWM1A/2A/ |

ePWM1A/2A/ |

ePWM1A/2A/ |

ePWM1A/2A/ |

ePWM1A/2A/ |

ePWM1A/2A/ |

|||||||

HRPWM channels |

0 |

3A/4A/5A/6A/ |

3A/4A/5A/6A/ |

3A/4A/5A/6A/ |

3A/4A/5A/6A/ |

|||||||||

3A/4A/5A/6A |

3A/4A/5A/6A |

|||||||||||||

|

|

7A/8A/9A |

7A/8A/9A |

7A/8A/9A |

7A/8A/9A |

|||||||||

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

32-bit Capture inputs or auxiliary PWM outputs |

0 |

6 |

|

6 |

6 |

|

6 |

4 |

|

4 |

||||

32-bit QEP channels (four inputs/channel) |

0 |

3 |

|

3 |

3 |

|

3 |

2 |

|

2 |

||||

Watchdog timer |

– |

Yes |

|

Yes |

Yes |

|

Yes |

Yes |

|

Yes |

||||

External ADC Interface |

– |

Yes |

|

Yes |

Yes |

|

Yes |

Yes |

|

Yes |

||||

32-bit CPU timers |

– |

3 |

|

3 |

3 |

|

3 |

3 |

|

3 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Multichannel Buffered Serial Port (McBSP)/SPI |

1 |

2 |

|

2 |

2 |

|

2 |

1 |

|

1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Serial Peripheral Interface (SPI) |

0 |

2 |

|

2 |

2 |

|

2 |

2 |

|

2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Serial Communications Interface (SCI) |

0 |

3 |

|

3 |

3 |

|

3 |

3 |

|

3 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Enhanced Controller Area Network (eCAN) |

0 |

2 |

|

2 |

2 |

|

2 |

2 |

|

2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Inter-Integrated Circuit (I2C) |

0 |

1 |

|

1 |

1 |

|

1 |

1 |

|

1 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

General-Purpose Input/Output (GPIO) pins |

– |

88 |

|

88 |

88 |

|

88 |

88 |

|

88 |

||||

(shared) |

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

External interrupts |

– |

8 |

|

8 |

8 |

|

8 |

8 |

|

8 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

(1)A type change represents a major functional feature difference in a peripheral module. Within a peripheral type, there may be minor differences between devices that do not affect the basic functionality of the module. These device-specific differences are listed in the TMS320x28xx, 28xxx DSP Peripheral Reference Guide (literature number SPRU566) and in the peripheral reference guides.

(2)TMX samples will come with the ZEP designator. The designator will change to ZFE after TMS.

(3)Custom secure versions of these devices are available. See Section 3.2.9, Security, for more details.

14 Introduction Copyright © 2009–2010, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Link(s): TMS320C28346, TMS320C28345, TMS320C28344 TMS320C28343, TMS320C28342,

TMS320C28341

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

www.ti.com SPRS516B –MARCH 2009 –REVISED JULY 2010

|

|

|

|

|

Table 2-1. C2834x Hardware Features |

(continued) |

|

|

|

|

|

|||||

|

FEATURE |

TYPE(1) |

C28346 |

C28345 |

|

C28344 |

|

C28343 |

|

C28342 |

|

C28341 |

||||

|

|

|

|

(300 MHz) |

(200 MHz) |

|

(300 MHz) |

|

(200 MHz) |

|

(300 MHz) |

|

(200 MHz) |

|||

|

|

T: –40°C to 105°C |

– |

ZFE |

ZFE |

|

ZHH |

ZFE |

|

ZFE |

|

ZHH |

ZFE |

ZFE |

|

ZHH |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Temperature |

|

S: –40°C to 125°C |

– |

ZFE |

ZFE |

|

– |

ZFE |

|

ZFE |

|

– |

ZFE |

ZFE |

|

– |

options |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Q: –40°C to 125°C |

– |

ZFE |

ZFE |

|

– |

ZFE |

|

ZFE |

|

– |

ZFE |

ZFE |

|

– |

|

|

|

|

|

|

|

|||||||||||

|

|

(Q100 qualification) |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Product status(1) |

|

|

– |

TMS |

TMS |

|

TMS |

|

TMS |

|

TMS |

|

TMS |

|||

(1)See Section 5.1 for descriptions of device stages.

Copyright © 2009–2010, Texas Instruments Incorporated |

Introduction |

15 |

|

Submit Documentation Feedback |

|

Product Folder Link(s): TMS320C28346, TMS320C28345, TMS320C28344 TMS320C28343, TMS320C28342,

TMS320C28341

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

www.ti.com |

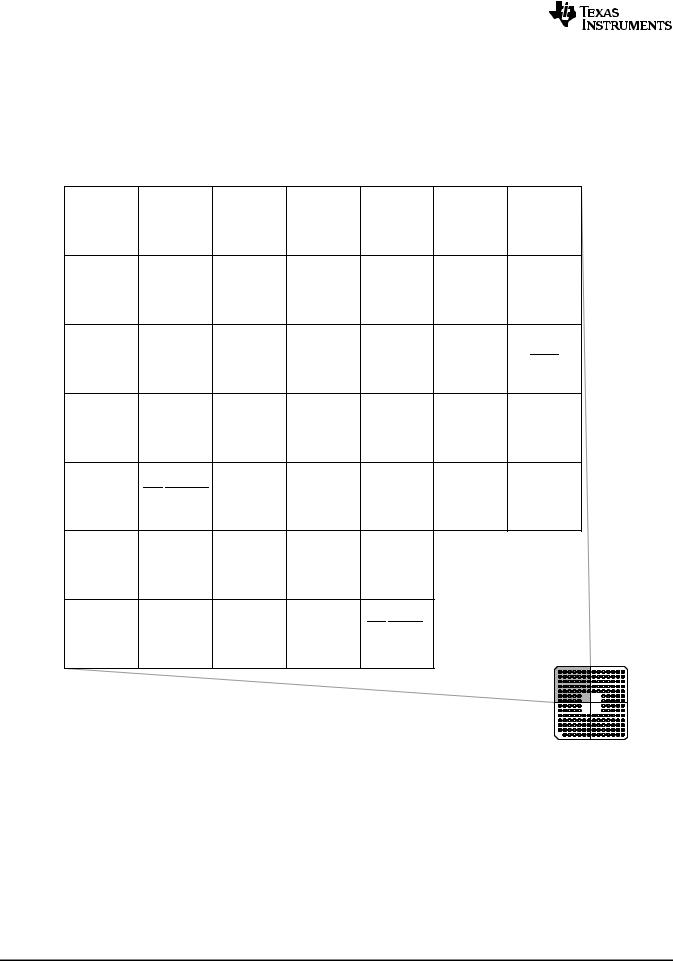

2.1Pin Assignments

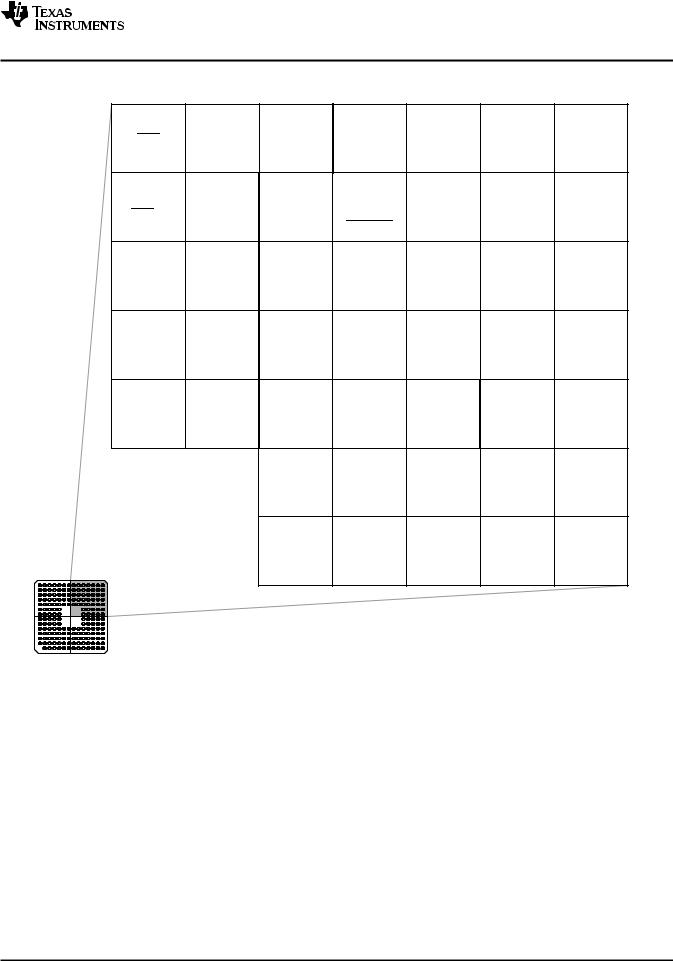

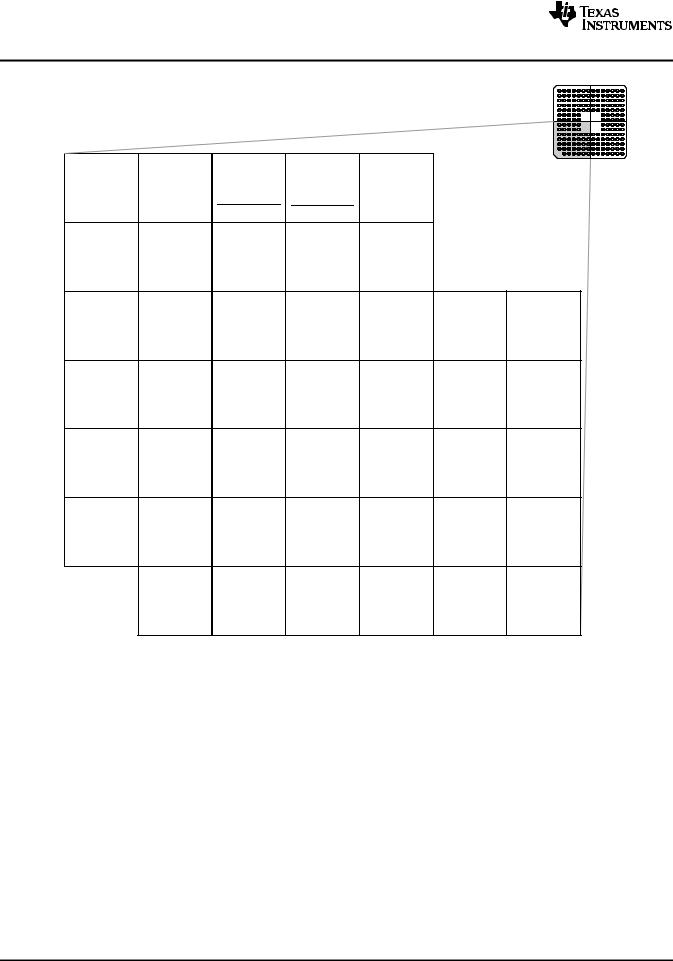

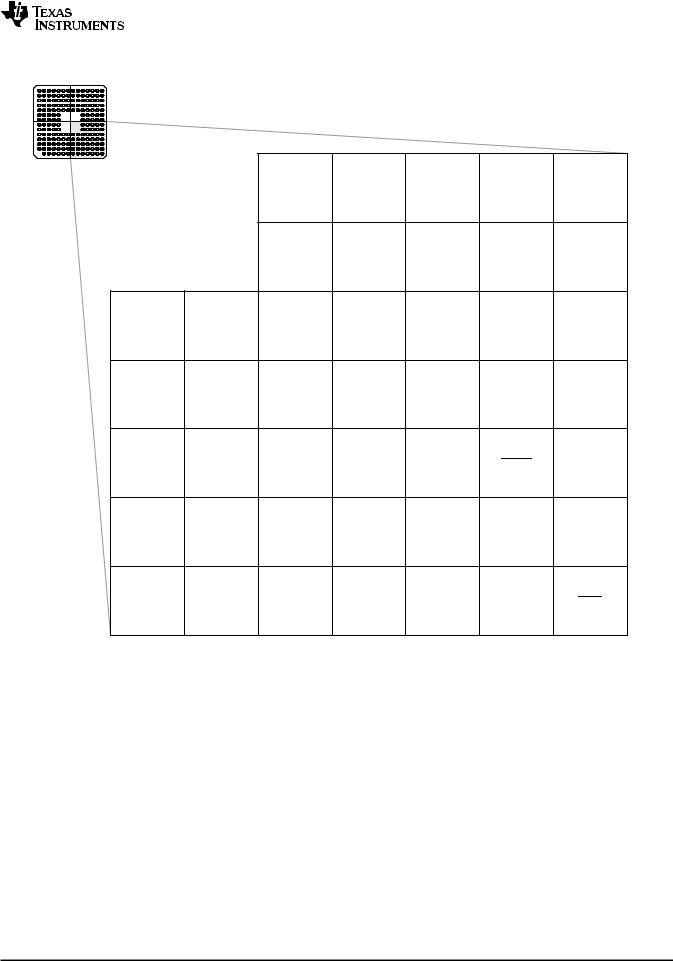

The 179-ball ZHH ball grid array (BGA) terminal assignments are shown in Figure 2-1 through Figure 2-4. The 256-ball ZFE plastic ball grid array (PBGA) terminal assignments are shown in Figure 2-5 through Figure 2-8. Table 2-2 describes the function(s) of each pin.

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

|

|

GPIO19/ |

GPIO23/ |

GPIO24/ |

GPIO32/ |

|

|

|

P |

EXTSOC2B |

EXTSOC3B |

SPISTEA/ |

EQEP1I/ |

ECAP1/ |

SDAA/ |

VDD |

P |

|

SCIRXDB/ |

MFSXA/ |

EQEP2A/ |

EPWMSYNCI/ |

||||||

|

|

|

CANTXA |

SCIRXDB |

MDXB |

ADCSOCAO |

|

|

|

|

|

|

|

GPIO22/ |

|

GPIO33/ |

|

|

|

|

|

|

|

|

|

|

|

||

N |

EXTSOC1A |

EXTSOC3A |

EXTADCCLK |

EQEP1S/ |

VDD |

SCLA/ |

TDO |

N |

|

MCLKXA/ |

|||||||||

|

|

|

|

|

EPWMSYNCO/ |

|

|

||

|

|

|

|

|

|

|

|

||

|

|

|

|

SCITXDB |

|

ADCSOCBO |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

GPIO21/ |

GPIO25/ |

GPIO27/ |

|

|

|

M |

VDD |

EXTSOC2A |

EXTSOC1B |

EQEP1B/ |

ECAP2/ |

ECAP4/ |

TRST |

M |

|

MDRA/ |

EQEP2B/ |

EQEP2S/ |

|||||||

|

|

|

|

CANRXB |

MDRB |

MFSXB |

|

|

|

|

GPIO18/ |

|

|

GPIO20/ |

|

|

|

|

|

L |

SPICLKA/ |

VDDIO |

VSS |

EQEP1A/ |

VSS |

TDI |

VSS |

L |

|

SCITXDB/ |

MDXA/ |

||||||||

|

CANRXA |

|

|

CANTXB |

|

|

|

|

|

|

|

GPIO15/ |

|

GPIO16/ |

|

GPIO26/ |

|

|

|

K |

VSS |

TZ4/XHOLDA/ |

VDD |

SPISIMOA/ |

VDDIO |

ECAP3/ |

VDDIO |

K |

|

SCIRXDB/ |

CANTXB/ |

EQEP2I/ |

|||||||

|

|

MFSXB |

|

TZ5 |

|

MCLKXB |

|

|

|

|

|

|

|

|

GPIO17/ |

6 |

7 |

|

|

|

|

|

|

|

|

|

|

||

J |

VDDIO |

VSS |

VDD |

VDD |

SPISOMIA/ |

J |

|

|

|

CANRXB/ |

|

|

|||||||

|

|

|

|

|

TZ6 |

|

|

|

|

|

|

GPIO12/ |

GPIO11/ |

GPIO13/ |

GPIO14/ |

|

|

|

|

H |

VSS |

TZ1/ |

EPWM6B/ |

TZ2/ |

TZ3/XHOLD/ |

H |

|

|

|

CANTXB/ |

SCIRXDB/ |

CANRXB/ |

SCITXDB/ |

|

|

||||

|

|

MDXB |

ECAP4 |

MDRB |

MCLKXB |

|

|

|

|

|

1 |

2 |

3 |

4 |

5 |

|

|

|

Figure 2-1. C2834x 179-Ball ZHH MicroStar BGA™ Upper Left Quadrant (Bottom VIew)

16 |

Introduction |

Copyright © 2009–2010, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320C28346, TMS320C28345, TMS320C28344 TMS320C28343, TMS320C28342,

TMS320C28341

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

www.ti.com SPRS516B –MARCH 2009 –REVISED JULY 2010

|

8 |

9 |

10 |

11 |

12 |

13 |

14 |

|

|

|

|

|

GPIO49/ |

|

GPIO54/ |

GPIO56/ |

GPIO58/ |

|

|

P |

XRS |

TCK |

ECAP6/ |

VDDIO |

SPISIMOA/ |

SPICLKA/ |

MCLKRA/ |

P |

|

XD30/ |

XD25/ |

XD23/ |

XD21/ |

||||||

|

|

|

SPISOMID |

|

EQEP3A |

EQEP3S |

EPWM7A |

|

|

|

|

|

GPIO50/ |

GPIO51/ |

GPIO55/ |

GPIO57/ |

|

|

|

|

|

|

EQEP1A/ |

EQEP1B/ |

SPISOMIA/ |

SPISTEA/ |

|

|

|

N |

XRSIO |

EMU0 |

XD29/ |

XD28/ |

XD24/ |

XD22/ |

VDD |

N |

|

|

|

|

SPICLKD |

SPISTED |

EQEP3B |

EQEP3I |

|

|

|

|

|

|

GPIO48/ |

GPIO52/ |

|

GPIO59/ |

GPIO60/ |

|

|

|

|

|

ECAP5/ |

|

MFSRA/ |

MCLKRB/ |

|

||

M |

TMS |

VSS |

EQEP1S/ |

VSS |

M |

||||

XD31/ |

XD20/ |

XD19/ |

|||||||

|

|

|

XD27 |

|

|

||||

|

|

|

SPISIMOD |

|

EPWM7B |

EPWM8A |

|

||

|

|

|

|

|

|

||||

|

|

|

|

GPIO53/ |

GPIO61/ |

GPIO62/ |

|

|

|

|

VSS |

|

VDD |

MFSRB/ |

SCIRXDC/ |

VDDIO |

|

||

L |

EMU1 |

EQEP1I/ |

L |

||||||

|

|

|

|

XD18/ |

XD17/ |

|

|

||

|

|

|

|

XD26 |

|

|

|||

|

|

|

|

EPWM8B |

EPWM9A |

|

|

||

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

GPIO63/ |

|

|

|

K |

VDDIO |

VDD |

VSS |

VDD |

GPIO64/ |

SCITXDC/ |

GPIO65/ |

K |

|

XD15 |

XD16/ |

XD14 |

|||||||

|

|

|

|

|

|

EPWM9B |

|

|

|

|

8 |

9 |

|

|

|

|

|

|

|

|

|

J |

VSS |

GPIO66/ |

GPIO67/ |

GPIO68/ |

VDDIO |

J |

|

|

|

XD13 |

XD12 |

XD11 |

|||||

|

|

|

VSS |

VDD |

GPIO70/ |

GPIO69/ |

VDD |

|

|

|

|

H |

XD9 |

XD10 |

H |

||||

|

|

|

10 |

11 |

12 |

13 |

14 |

|

Figure 2-2. C2834x 179-Ball ZHH MicroStar BGA™ Upper Right Quadrant (Bottom View)

Copyright © 2009–2010, Texas Instruments Incorporated |

Introduction |

17 |

Submit Documentation Feedback

Product Folder Link(s): TMS320C28346, TMS320C28345, TMS320C28344 TMS320C28343, TMS320C28342,

TMS320C28341

TMS320C28346, TMS320C28345, TMS320C28344 |

|

|

|

|

|||||

TMS320C28343, TMS320C28342, TMS320C28341 |

|

|

|

|

|||||

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

|

|

|

|

|

www.ti.com |

|||

|

1 |

2 |

3 |

4 |

5 |

|

|

|

|

|

|

GPIO9/ |

GPIO10/ |

GPIO8/ |

|

|

|

|

|

G |

VDD |

EPWM5B/ |

EPWM6A/ |

EPWM5A/ |

VSS |

G |

|

|

|

|

SCITXDB/ |

CANRXB/ |

CANTXB/ |

|

|

|

|||

|

|

|

|

|

|

||||

|

|

ECAP3 |

ADCSOCBO |

ADCSOCAO |

|

|

|

|

|

|

|

GPIO7/ |

GPIO6/ |

|

|

|

|

|

|

F |

VDDIO |

EPWM4B/ |

EPWM4A/ |

VSS |

GPIO2/ |

F |

|

|

|

MCLKRA/ |

EPWMSYNCI/ |

EPWM2A |

|

|

|||||

|

|

ECAP2 |

EPWMSYNCO |

|

|

6 |

7 |

|

|

|

|

|

GPIO5/ |

GPIO3/ |

|

|

|

|

|

E |

VDD |

GPIO4/ |

EPWM3B/ |

EPWM2B/ |

VDD |

GPIO80/ |

GPIO46/ |

E |

|

EPWM3A |

MFSRA/ |

ECAP5/ |

XA8 |

XA6 |

|||||

|

|

|

ECAP1 |

MCLKRB |

|

|

|

|

|

D |

VDD |

VSS |

VDDIO |

GPIO85/ |

GPIO84/ |

GPIO47/ |

VDDIO |

D |

|

XA13 |

XA12 |

XA7 |

|||||||

|

GPIO1/ |

GPIO30/ |

GPIO29/ |

|

|

|

|

|

|

|

EPWM1B/ |

VDD |

GPIO81/ |

VDD |

VDD18 |

|

|||

C |

CANRXA/ |

SCITXDA/ |

C |

||||||

ECAP6/ |

XA9 |

||||||||

|

XA18 |

XA19 |

|

|

|

|

|||

|

MFSRB |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||

|

GPIO0/ |

GPIO31/ |

GPIO87/ |

VDDIO |

GPIO83/ |

VDDIO |

VDD |

|

|

B |

CANTXA/ |

B |

|||||||

EPWM1A |

XA15 |

|

XA11 |

|

|

||||

|

XA17 |

|

|

|

|

||||

|

|

|

|

|

|

|

|

||

A |

|

GPIO39/ |

GPIO86/ |

VSS |

GPIO82/ |

VSS |

VSS |

A |

|

|

XA16 |

XA14 |

XA10 |

||||||

|

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

|

|

Figure 2-3. C2834x 179-Ball ZHH MicroStar BGA™ |

Lower Left Quadrant (Bottom View) |

|||||||

18 |

Introduction |

Copyright © 2009–2010, Texas Instruments Incorporated |

Submit Documentation Feedback

Product Folder Link(s): TMS320C28346, TMS320C28345, TMS320C28344 TMS320C28343, TMS320C28342,

TMS320C28341

TMS320C28346, TMS320C28345, TMS320C28344

TMS320C28343, TMS320C28342, TMS320C28341

www.ti.com |

SPRS516B –MARCH 2009 –REVISED JULY 2010 |

|

|

|

|

|

|

|

|

10 |

11 |

12 |

13 |

14 |

|

|

|

|

G |

VDD |

VSS |

GPIO71/ |

GPIO72/ |

VSS |

G |

|

|

|

|

XD8 |

XD7 |

|

|||

|

|

|

F |

GPIO78/ |

VDDIO |

GPIO75/ |

GPIO74/ |

GPIO73/ |

F |

|

|

|

XD1 |

XD4 |

XD5 |

XD6 |

|||

|

8 |

9 |

|

|

|

|

|

|

|

E |

VDD18 |

VSS |

|

GPIO40/ |

GPIO77/ |

VDD |

GPIO76/ |

VSS |

E |

|

XA0 |

XD2 |

XD3 |

||||||

|

|

|

|

GPIO41/ |

GPIO37/ |

|

|

|

|

D |

VSS |

XCLKIN |

|

ECAP2/ |

VDD |

VSS |

VDDIO |

D |

|

|

XA1 |

||||||||

|

|

|

|

XZCS7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

X1 |

VDDIO |

|

VDD |

VDD |

GPIO38/ |

XWE1 |

GPIO79/ |

|

C |

|

XWE0 |

XD0 |

C |

|||||

|

|

GPIO45/ |

|

GPIO42/ |

|

GPIO36/ |

GPIO35/ |

|

|

|

VSSK |

|

VSS |

SCIRXDA/ |

SCITXDA/ |

XCLKOUT |

|

||

B |

XA5 |

|

XA2 |

B |

|||||

|

|

|

|

XZCS0 |

XR/W |

|

|

||

|

|

|

|

|

|

|

|

||

A |

X2 |

GPIO44/ |

|

GPIO43/ |

|

GPIO28/ |

GPIO34/ |

|

A |

|

VDDIO |