Texas Instruments TMDS 351 INSTALLATION INSTRUCTIONS

TMDS351

www.ti.com |

SLLS840 – MAY 2007 |

|

2.5 Gbps 3-TO-1 DVI/HDMI SWITCH

FEATURES

∙Compatible with HDMI 1.3a

∙Supports 2.5 Gbps Signaling Rate for 480i/p, 720i/p, and 1080i/p Resolutions up to 12-Bit Color Depth

∙Integrated Receiver Termination

∙Selectable Receiver Equalization to Accommodate to Different Input Cable Lengths

∙Intra-Pair Skew < 40 ps

∙Inter-Pair Skew < 65 ps

∙HBM ESD Protection Exceeds 8 kV to TMDS Inputs

∙3.3-V Fixed Supply to TMDS I/Os

∙5-V Fixed Supply to HPD, DDC, and Source Selection Circuits

∙64-Pin TQFP Package

∙ROHS Compatible and 260°C Reflow Rated

APPLICATIONS

∙Digital TV

∙Digital Projector

DESCRIPTION

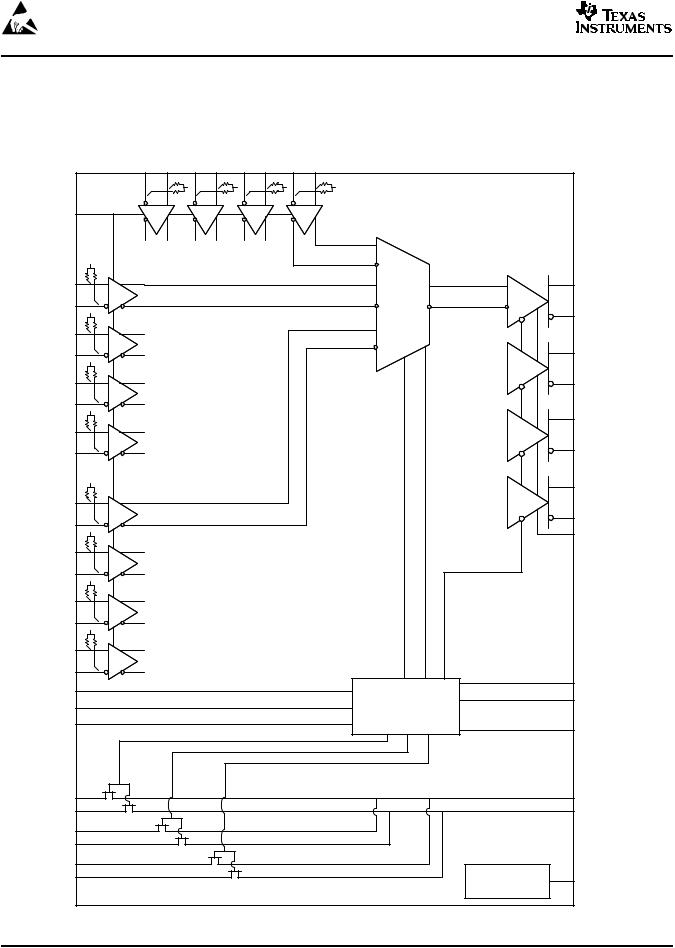

The TMDS351 is a 3-port digital video interface (DVI) or high-definition multimedia interface (HDMI) switch that allows up to 3 DVI or HDMI ports to be switched to a single display terminal. Four TMDS channels, one hot plug detector, and a digital display control (DDC) interface are supported on each port. Each TMDS channel supports signaling rates up to 2.5 Gbps to allow 1080p resolution in 12-bit color depth.

When S1 is high and S2 is low, all input terminations are disconnected, TMDS inputs are high impedance with standard TMDS terminations, all internal MOSFETs are turned off to disable the DDC links, and all HPD outputs are connected to the HPD_SINK. This allows the initiation of the HDMI physical address discovery process.

www.DataSheet4U.com

Termination resistors (50-Ω), pulled up to VCC, are integrated at each TMDS receiver input. External terminations are not required. A precision resistor is connected externally from the VSADJ pin to ground for setting the differential output voltage to be compliant with the TMDS standard.

The TMDS351 provides two levels of receiver input equalization for different ranges of cable lengths. Each TMDS receiver owns frequency responsive equalization circuits. When EQ sets low, the receiver supports the input connection in short range HDMI cables. When EQ sets high, the receiver supports the input connection in long range HDMI cables. The TMDS351 supports power saving operation. When a system is under standby mode and there is no digital audio/visual content from a connected source, the 3.3-V supply voltage, VCC, can be powered off to minimize power consumption from the TMDS inputs, outputs, and internal switching circuits. The HPD, DDC, and source selection circuits are powered up by the 5-V supply voltage, VDD, to maintain the system hot plug detect response, the DDC link from the selected source to the sink under system standby operation. The device is characterized for operation from 0°C to 70°C.

|

|

Typical Application |

DVD Player |

Game |

Digital TV |

|

|

|

|

Console |

|

STB |

|

TMDS351 |

|

|

|

|

|

3-to-1 |

|

|

PHY SX |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. |

Copyright © 2007, Texas Instruments Incorporated |

Products conform to specifications per the terms of the Texas |

|

Instruments standard warranty. Production processing does not |

|

necessarily include testing of all parameters. |

|

TMDS351

www.ti.com

SLLS840 – MAY 2007

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

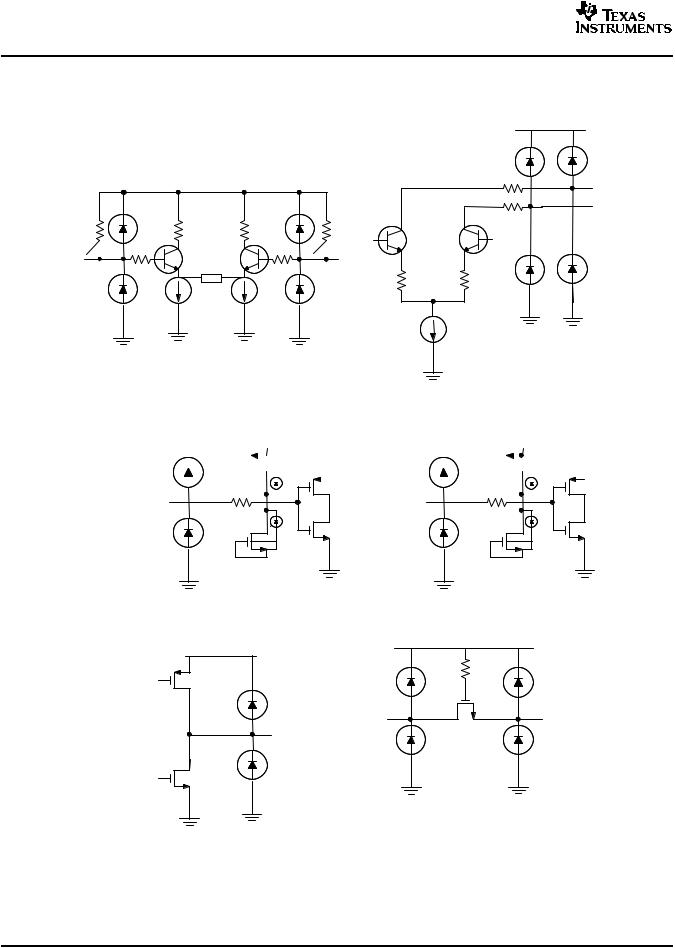

FUNCTIONAL BLOCK DIAGRAM

|

|

B11 |

A11 |

B12 |

A12 |

B13 |

A13 |

B14 |

A14 |

|

|

|

|

|

R |

|

R |

|

R |

|

R |

|

|

|

|

|

INT |

V |

INT |

V |

INT |

V |

INT |

V |

|

|

|

|

R |

cc |

R |

cc |

R |

cc |

R |

cc |

|

|

|

|

|

|

|

|

|

||||

|

|

|

INT |

|

INT |

|

INT |

|

INT |

|

|

EQ |

|

|

Rx TMD S |

|

Rx TMD S |

|

Rx TMD S |

|

Rx TMD S |

|

|

|

|

|

|

|

|

|

|

||||

|

Vcc |

|

|

|

|

|

|

|

|

|

|

|

RINT |

RINT |

|

|

|

|

|

|

|

|

|

A24 |

|

TMDS |

|

|

|

|

|

|

|

|

Y4 |

|

|

|

|

|

|

|

|

|

TMDS |

|

|

B24 |

|

Rx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Driver |

|

||

Vcc |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

Z4 |

|

|

RINT |

RINT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

A23 |

|

TMDS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B23 |

|

Rx |

|

|

|

|

|

|

|

|

Y3 |

Vcc |

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

TMDS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RINT |

RINT |

. |

|

|

|

|

|

|

Driver |

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

||

A22 |

|

TMDS |

|

|

|

|

|

|

|

|

Z3 |

|

|

. |

|

|

|

|

|

|

|

|

|

B22 |

|

Rx |

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

|

||

Vcc |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

Y2 |

A21 |

RINT |

RINT |

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

|

TMDS |

|

|

|

|

TMDS |

|

|

|

|

|

|

|

Driver |

|

B21 |

|

Rx |

|

|

|

|

|

|

|

. |

Z2 |

|

|

|

|

|

|

|

|

|

|

||

|

Vcc |

|

|

|

|

|

|

|

|

|

Y1 |

|

RINT |

RINT |

|

|

|

|

|

|

|

|

|

A34 |

|

|

|

|

|

|

|

TMDS |

|

||

|

|

|

|

|

|

|

|

|

|

||

|

TMDS |

|

|

|

|

|

|

|

Driver |

|

|

|

|

|

|

|

|

|

|

|

|

Z1 |

|

B34 |

|

Rx |

|

|

|

|

|

|

|

|

|

Vcc |

|

|

|

|

|

|

|

|

|

VSADJ |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

RINT |

RINT |

|

|

|

|

|

|

|

|

|

A33 |

|

|

|

|

|

|

|

|

|

|

|

|

|

TMDS |

|

|

|

|

|

|

|

|

|

B33 |

|

Rx |

|

|

|

|

|

|

|

|

|

Vcc |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

RINT |

RINT |

. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

A32 |

|

|

|

|

|

|

|

|

|

|

|

|

|

TMDS |

. |

|

|

|

|

|

|

|

|

B32 |

|

Rx |

|

|

|

|

|

|

|

|

|

Vcc |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

. |

|

|

|

|

|

|

|

|

|

RINT |

RINT |

|

|

|

|

|

|

|

|

|

A31 |

|

|

|

|

|

|

|

|

|

|

|

|

|

TMDS |

|

|

|

|

|

|

|

|

|

B31 |

|

Rx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HPD1 |

|

|

|

|

|

|

|

|

|

|

S1 |

|

|

|

|

|

|

|

|

|

Control |

|

|

HPD2 |

|

|

|

|

|

|

|

|

|

S2 |

|

|

|

|

|

|

|

|

|

|

Logic |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HPD3 |

|

|

|

|

|

|

|

|

|

|

HPD_SINK |

|

|

|

|

|

|

|

|

|

|

|

|

SCL1 |

|

|

|

|

|

|

|

|

|

|

SCL_SINK |

SDA1 |

|

|

|

|

|

|

|

|

|

|

SDA_SINK |

|

|

|

|

|

|

|

|

|

|

|

|

SCL2 |

|

|

|

|

|

|

|

|

|

|

|

SDA2 |

|

|

|

|

|

|

|

|

|

|

|

SCL3 |

|

|

|

|

|

|

|

|

|

|

|

SDA3 |

|

|

|

|

|

|

|

|

|

HPD/DDC |

VDD |

|

|

|

|

|

|

|

|

|

|

Power Supply |

|

|

|

|

|

|

|

|

|

|

|

|

2 |

Submit Documentation Feedback |

www.ti.com

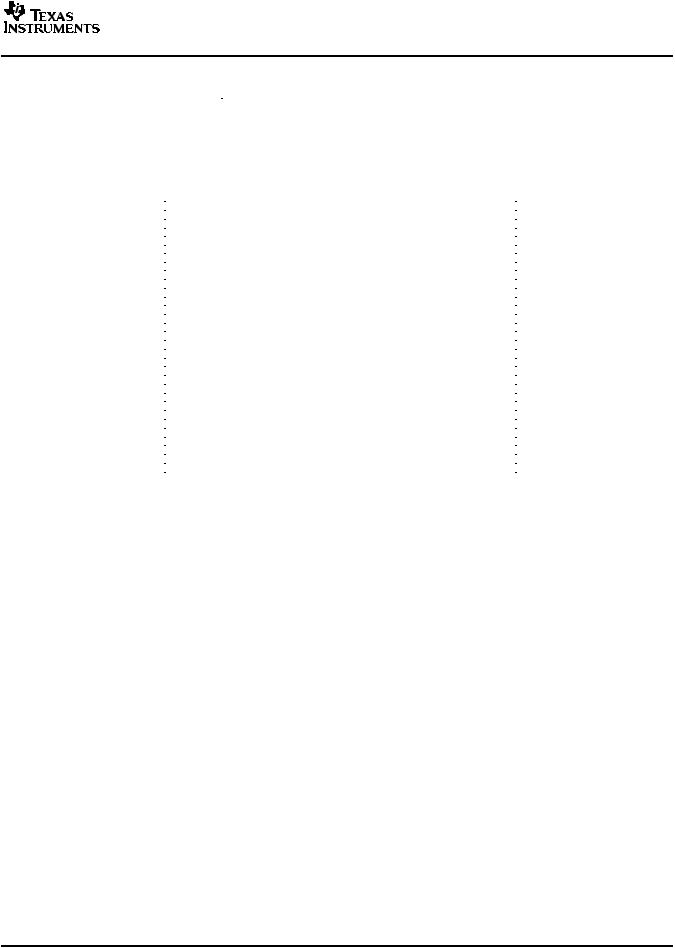

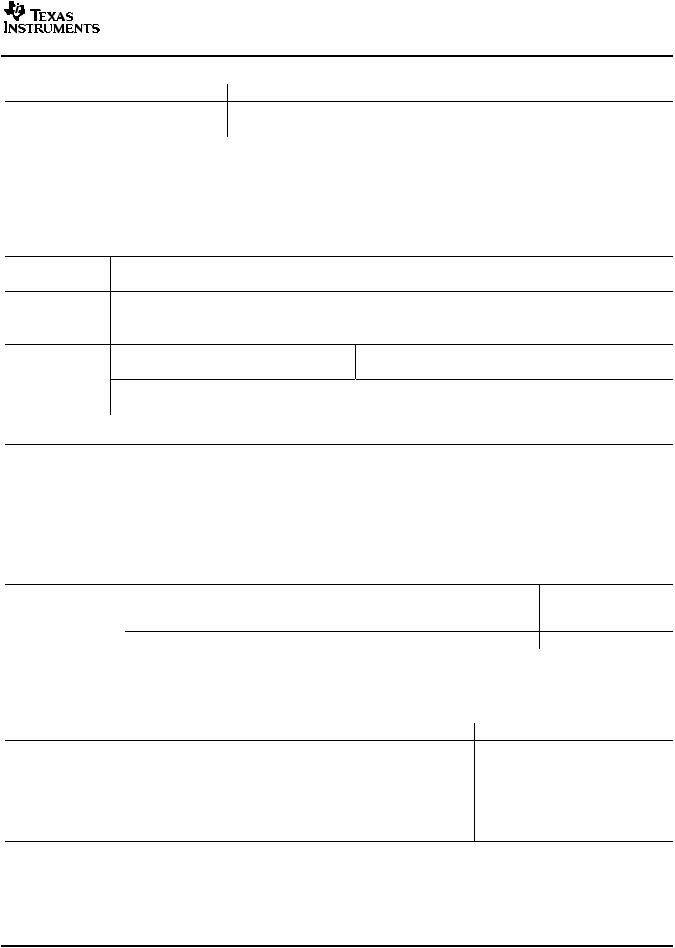

PFC PACKAGE (TOP VIEW)

|

|

|

|

|

HPD3 |

A24 |

B24 |

Vcc |

A23 |

B23 |

GND |

A22 |

B22 |

Vcc |

A21 |

B21 |

SCL2 |

|

SDA2 |

|

HPD2 |

|

VDD |

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

64 |

|

63 |

|

62 |

|

61 |

|

60 |

|

59 |

58 |

57 |

56 |

55 |

|

54 |

53 |

52 |

51 |

50 |

49 |

|

|

|

|

|

|||||

|

|

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDA3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

48 |

|

|

|

A14 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

SCL3 |

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

47 |

|

|

|

B14 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

GND |

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

46 |

|

|

|

Vcc |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

B31 |

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

45 |

|

|

|

A13 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

A31 |

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

44 |

|

|

|

B13 |

|||

Vcc |

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

43 |

|

|

|

GND |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

B32 |

|

|

7 |

|

|

|

|

|

|

|

|

|

|

|

TMDS351 |

|

|

|

|

|

|

|

42 |

|

|

|

A12 |

|||||||

A32 |

|

|

8 |

|

|

|

|

|

|

|

|

|

|

|

64-pin TQFP |

|

|

|

|

|

|

|

41 |

|

|

|

B12 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

GND |

|

|

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

40 |

|

|

|

Vcc |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

A11 |

|

B33 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

39 |

|

|

|

|||||

|

|

|

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B11 |

|

A33 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

38 |

|

|

|

|||||

|

|

|

12 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SCL1 |

|

Vcc |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

37 |

|

|

|

|||||

|

|

|

13 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDA1 |

|

B34 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

36 |

|

|

|

|||||

|

|

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HPD1 |

|

A34 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

35 |

|

|

|

|||||

|

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EQ |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

GND |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

34 |

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

VSADJ |

|

|

16 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

33 |

|

|

|

S2 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

17 |

|

18 |

|

19 |

|

20 |

|

21 |

|

22 |

23 |

24 |

25 |

26 |

|

27 |

28 |

29 |

30 |

31 |

32 |

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Y4 |

Z4 |

Vcc |

Y3 |

Z3 |

GND |

Y2 |

Z2 |

Vcc |

Y1 |

Z1 |

GND |

SCL_SINK |

SDA_SINK |

HPD_SINK |

S1 |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Submit Documentation Feedback

TMDS351

SLLS840 – MAY 2007

3

TMDS351

www.ti.com

SLLS840 – MAY 2007

|

|

|

TERMINAL FUNCTIONS |

|

TERMINAL |

I/O |

DESCRIPTION |

||

NAME |

NO. |

|||

|

|

|||

A11, A12, A13, A14 |

39, 42, 45, 48 |

I |

Source port 1 TMDS positive inputs |

|

A21, A22, A23, A24 |

54, 57, 60, 63 |

I |

Source port 2 TMDS positive inputs |

|

A31, A32, A33, A34 |

5, 8, 11, 14 |

I |

Source port 3 TMDS positive inputs |

|

B11, B12, B13, B14 |

38, 41, 44, 47 |

I |

Source port 1 TMDS negative inputs |

|

B21, B22, B23, B24 |

53, 56, 59, 62 |

I |

Source port 2 TMDS negative inputs |

|

B31, B32, B33, B34 |

4, 7, 10, 13 |

I |

Source port 3 TMDS negative inputs |

|

GND |

3, 9, 15, 22, 28, |

|

Ground |

|

43, 58 |

|

|||

|

|

|

||

|

|

|

TMDS Input equalization selector (control pin) |

|

EQ |

34 |

I |

EQ = Low – HDMI 1.3 compliant cable |

|

|

|

|

EQ = High – 10m 28 AWG HDMI cable |

|

HPD1 |

35 |

O |

Source port 1 hot plug detector output (status pin) |

|

HPD2 |

50 |

O |

Source port 2 hot plug detector output (status pin) |

|

HPD3 |

64 |

O |

Source port 3 hot plug detector output (status pin) |

|

HPD_SINK |

31 |

I |

Sink port hot plug detector input (status pin) |

|

SCL1 |

37 |

I/O |

Source port 1 DDC I2C clock line |

|

SCL2 |

52 |

I/O |

Source port 2 DDC I2C clock line |

|

SCL3 |

2 |

I/O |

Source port 3 DDC I2C clock line |

|

SCL_SINK |

29 |

I/O |

Sink port DDC I2C clock line |

|

SDA1 |

36 |

I/O |

Source port 1 DDC I2C data line |

|

SDA2 |

51 |

I/O |

Source port 2 DDC I2C data line |

|

SDA3 |

1 |

I/O |

Source port 3 DDC I2C data line |

|

SDA_SINK |

30 |

I/O |

Sink port DDC I2C data line |

|

S1, S2 |

32. 33 |

I |

Source selector |

|

VCC |

6, 12, 19, 25, 40, |

|

Power supply |

|

46, 55, 61 |

|

|||

VDD |

49 |

|

HPD/DDC Power supply |

|

VSADJ |

16 |

I |

TMDS compliant voltage swing control (control pin) |

|

Y1, Y2, Y3, Y4 |

26,23,20,17 |

O |

Sink port TMDS positive outputs |

|

Z1, Z2, Z3, Z4 |

27,24,21,18 |

O |

Sink port TMDS negative outputs |

|

4 |

Submit Documentation Feedback |

TMDS351

www.ti.com

|

|

|

|

|

|

SLLS840 – MAY 2007 |

|

|

|

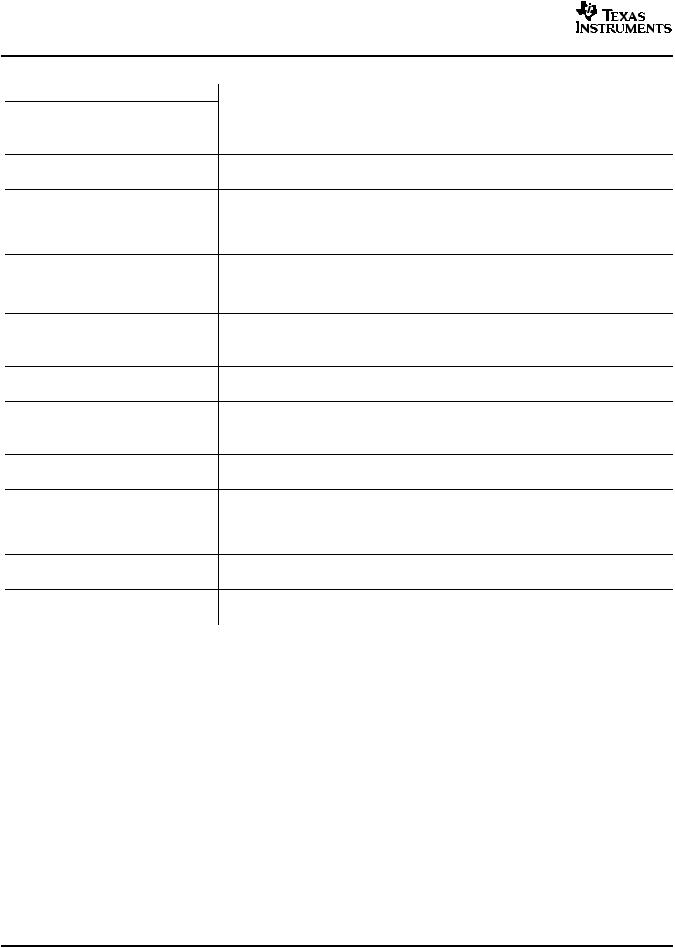

Table 1. Source Selection Lookup(1) |

|

||||

CONTROL PINS |

I/O SELECTED |

|

HOT PLUG DETECT STATUS |

||||

S1 |

S2 |

Y/Z |

SCL_SINK |

HPD1 |

HPD2 |

HPD3 |

|

SDA_SINK |

|||||||

|

|

|

|

|

|

||

|

|

A1/B1 |

SCL1 |

|

|

|

|

H |

H |

Terminations of A2/B2 |

SDA1 |

HPD_SINK |

L |

L |

|

and A3/B3 are |

|

||||||

|

|

|

|

|

|

||

|

|

disconnected |

|

|

|

|

|

|

|

A2/B2 |

SCL2 |

|

|

|

|

H |

L |

Terminations of A1/B1 |

SDA2 |

L |

HPD_SINK |

L |

|

and A3/B3 are |

|

||||||

|

|

|

|

|

|

||

|

|

disconnected |

|

|

|

|

|

|

|

A3/B3 |

SCL3 |

|

|

|

|

L |

L |

Terminations of A1/B1 |

SDA3 |

L |

L |

HPD_SINK |

|

and A2/B2 are |

|

||||||

|

|

|

|

|

|

||

|

|

disconnected |

|

|

|

|

|

L |

H |

None (Z) |

None (Z) |

HPD_SINK |

HPD_SINK |

HPD_SINK |

|

|

|

All terminations are |

Are pulled HIGH by |

|

|

|

|

|

|

disconnected |

external pull-up |

|

|

|

|

|

|

|

termination |

|

|

|

|

(1)H: Logic high; L: Logic low; X: Don'tcare; Z: High impedance

Submit Documentation Feedback |

5 |

TMDS351

www.ti.com

SLLS840 – MAY 2007

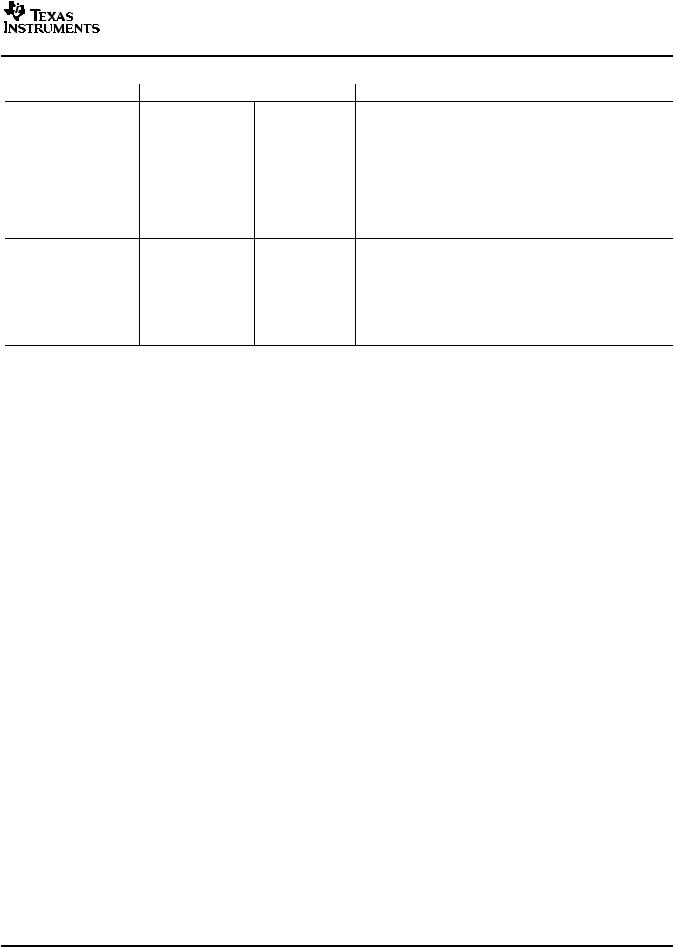

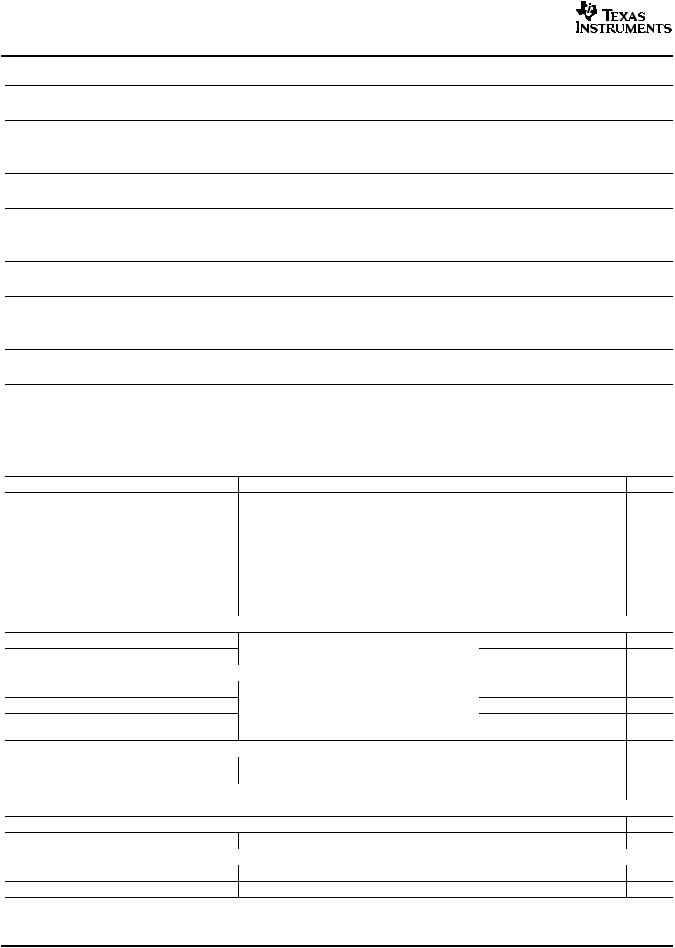

EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

TMDS Input Stage |

TMDS Output Stage |

|

VCC |

VCC |

Y |

|

Z |

50 Ω |

50 Ω |

A |

B |

10 mA

Control Input Stage |

|

|

Status and Source Selector |

||||||||||||||||||||

VCC |

|

|

VDD |

||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

EQ |

HPD_SINK |

|

S1 |

|

S2 |

DDC pass gate

HPD output stage

VDD

VDD

HPD1 |

SCL/SCA |

SCL/SCA |

|

Source |

Sink |

||

|

|||

HPD2 |

|

|

|

HPD3 |

|

|

6 |

Submit Documentation Feedback |

TMDS351

www.ti.com

|

|

SLLS840 – MAY 2007 |

|

ORDERING INFORMATION(1) |

|

PART NUMBER |

PART MARKING |

PACKAGE |

TMDS351PAG |

TMDS351 |

64-PIN TQFP |

TMDS351PAGR |

TMDS351 |

64-PIN TQFP Tape/Reel |

(1)For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)(1)

|

|

UNIT |

Supply voltage |

VCC |

–0.5 V to 4 V |

range(2) |

VDD |

–0.5 V to 6 V |

|

||

|

Anm(3), Bnm |

2.5 V to 4 V |

Voltage range |

Ym, Zm, VSADJ, EQ |

–0.5V to 4 V |

|

SCLn, SCL_SINK, SDAn, SDA_SINK, HPDn, HPD_SINK, S1, S2 |

–0.5 V to 6 V |

|

Anm, Bnm |

±8000 V |

|

Human body model(4) |

±4000 V |

Electrostatic |

All pins |

|

discharge |

Charged-device model(5) (all pins) |

±1500 V |

|

Machine model (6) (all pins) |

± 200 V |

Continuous power dissipation

See Dissipation Rating

Table

(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2)All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

(3)n = 1, 2, 3; m = 1, 2, 3, 4

(4)Tested in accordance with JEDEC Standard 22, Test Method A114-B

(5)Tested in accordance with JEDEC Standard 22, Test Method C101-A

(6)Tested in accordance with JEDEC Standard 22, Test Method A115-A

DISSIPATION RATINGS

|

PCB JEDEC |

|

DERATING FACTOR (1) |

T = 70°C |

|

PACKAGE |

|

TA ≤ 25°C |

ABOVE TA = 25°C |

A |

|

STANDARD |

POWER RATING |

||||

|

|

||||

64-TQFP PAG |

Low-K |

1111 mW |

11.19 mW/°C |

611 mW |

|

High-K |

1492 mW |

14.92 |

820 mW |

||

|

(1)This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

THERMAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|

PARAMETER |

TEST CONDITIONS |

MIN |

TYP |

MAX(1) |

UNIT |

RθJB |

Junction-to-board thermal |

|

|

33.4 |

|

°C/W |

|

resistance |

|

|

|

|

|

RθJC |

Junction- to-case thermal |

|

|

15.6 |

|

°C/W |

|

resistance |

|

|

|

|

|

|

|

VIH = VCC, VIL = VCC - 0.6 V, RT = 50 Ω, AVCC = 3.3V, |

|

|

|

|

PD |

Device power dissipation |

Am/Bm(2:4) = 2.5-Gbps HDMI data pattern, |

|

590 |

750 |

mW |

|

|

Am/Bm(1) = 250-MHz clock |

|

|

|

|

(1)The maximum rating is simulation under 3.6-V VCC, 5.5-V VDD, and 600 mV VID.

Submit Documentation Feedback |

7 |

TMDS351

www.ti.com

SLLS840 – MAY 2007

RECOMMENDED OPERATING CONDITIONS

|

|

MIN |

NOM |

MAX |

UNIT |

VCC |

Supply voltage |

3 |

3.3 |

3.6 |

V |

VDD |

Standby supply voltage |

4.5 |

5 |

5.5 |

V |

TA |

Operating free-air temperature |

0 |

|

70 |

°C |

TMDS DIFFERENTIAL PINS |

|

|

|

|

|

VIC |

Input common mode voltage |

VCC–0.4 |

|

VCC+0.01 |

V |

VID |

Receiver peak-to-peak differential input voltage |

150 |

|

1560 |

mVp-p |

RVSADJ |

Resistor for TMDS compliant voltage swing range |

3.66 |

4.02 |

4.47 |

kΩ |

AVCC |

TMDS output termination voltage, see Figure 1 |

3 |

3.3 |

3.6 |

V |

RT |

Termination resistance, see Figure 1 |

45 |

50 |

55 |

Ω |

|

Signaling rate |

0 |

|

2.5 |

Gbps |

CONTROL PINS |

|

|

|

|

|

VIH |

LVTTL High-level input voltage |

2 |

|

VCC |

V |

VIL |

LVTTL Low-level input voltage |

GND |

|

0.8 |

V |

DDC I/O PINS |

|

|

|

|

|

VI(DDC) |

DDC Input voltage |

GND |

|

VDD |

V |

STATUS and SOURCE SELECTOR PINS |

|

|

|

|

|

VIH |

LVTTL High-level input voltage |

2 |

|

VDD |

V |

VIL |

LVTTL Low-level input voltage |

GND |

|

0.8 |

V |

ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

|

PARAMETER |

|

ICC |

Supply current |

|

IDD |

Power supply current, 5-V |

|

TMDS DIFFERENTIAL PINS |

||

VOH |

Single-ended high-level output voltage |

|

VOL |

Single-ended low-level output voltage |

|

Vswing |

Single-ended output swing voltage |

|

VOD(O) |

Overshoot of output differential voltage |

|

VOD(U) |

Undershoot of output differential voltage |

|

VOC(SS) |

Change in steady-state common-mode |

|

output voltage between logic states |

||

|

||

I(OS) |

Short circuit output current |

|

VI(open) |

Single-ended input voltage under high |

|

impedance input or open input |

||

|

||

RINT |

Input termination resistance |

|

CONTROL PINS |

||

IIH |

High-level digital input current(2) |

|

IIL |

Low-level digital input current(2) |

|

TEST CONDITIONS |

|

VIH = VCC, VIL = VCC – 0.6 V, |

S1/S2 = |

RT = 50 Ω, AVCC = 3.3 V |

Low/Low, |

Am/Bm(2:4) = 2.5 Gbps HDMI data |

Low/High, |

pattern |

High/High |

Am/Bm(1) = 250 MHz clock |

S1/S2 = |

|

|

|

High/Low |

VIH = VCC, VIL = VCC – 0.6 V,

RT = 50 Ω, AVCC = 3.3 V

Am/Bm(2:4) = 2.5 Gbps HDMI data pattern

Am/Bm(1) = 250 MHz clock

See Figure 2, AVCC = 3.3 V,

See Figure 2, AVCC = 3.3 V,

RT = 50 Ω

See Figure 3

See Figure 3

II = 10 µA

VIN = 2.9 V

VIN = 2.9 V

VIH = 2 V or VCC

VIH = 2 V or VCC

VIL = GND or 0.8 V

DDC I/O PINS |

|

|

Ilkg |

Input leakage current |

VI = 0.1 VDD to 0.9 VDD to isolated DDC inputs |

CIO |

Input/output capacitance |

VI(pp) = 1 V, 100 kHz |

MIN |

TYP(1) |

MAX |

UNIT |

|

176 |

200 |

|

|

|

|

mA |

|

8 |

20 |

|

|

2 |

5 |

mA |

AVCC–10 |

|

AVCC+10 |

mV |

AVCC–600 |

|

AVCC–400 |

mV |

400 |

|

600 |

mV |

|

|

15% |

2× Vswing |

|

|

25% |

2× Vswing |

|

|

5 |

mV |

-12 |

|

12 |

mA |

VCC–10 |

|

VCC+10 |

mV |

45 |

50 |

55 |

Ω |

-10 |

|

10 |

µA |

-10 |

|

10 |

µA |

-10 |

|

10 |

µA |

|

|

10 |

pF |

(1)All typical values are at 25°C and with a 3.3-V supply.

(2)IIH and IIL specifications are not applicable to the VSADJ pin.

8 |

Submit Documentation Feedback |

Loading...

Loading...