Texas Instruments TLV5628CN, TLV5628CDWR, TLV5628CDW, TLV5628IN, TLV5628IDWR Datasheet

...

TLV5628C, TLV5628I OCTAL 8-BIT DIGITAL-TO-ANALOG CONVERTERS

SLAS108A ± JANUARY 1995 ± REVISED NOVEMBER 1995

DEight 8-Bit Voltage Output DACs

D3-V Single Supply Operation

DSerial Interface

DHigh-Impedance Reference Inputs

DProgrammable for 1 or 2 Times Output Range

DSimultaneous Update Facility

DInternal Power-On Reset

DLow Power Consumption

DHalf-Buffered Output

DW OR N PACKAGE

(TOP VIEW)

DACB |

|

1 |

16 |

|

DACC |

|

|

||||

DACA |

|

2 |

15 |

|

DACD |

|

|

||||

GND |

|

3 |

14 |

|

REF1 |

|

|

||||

DATA |

|

4 |

13 |

|

LDAC |

|

|

||||

CLK |

|

5 |

12 |

|

LOAD |

|

|

||||

VDD |

|

6 |

11 |

|

REF2 |

|

|

||||

|

|

|

|

DACH |

|

DACE |

|

7 |

10 |

|

|

DACF |

|

8 |

9 |

|

DACG |

|

|

||||

|

|

|

|

|

|

applications

DProgrammable Voltage Sources

DDigitally Controlled Amplifiers/Attenuators

DMobile Communications

DAutomatic Test Equipment

DProcess Monitoring and Control

DSignal Synthesis

description

The TLV5628C and TLV5628I are octal 8-bit voltage output digital-to-analog converters (DACs) with buffered reference inputs (high impedance). The DACs produce an output voltage that varies between one or two times the reference voltages and GND, and the DACs are monotonic. The device is simple to use, running from a single supply of 3 to 3.6 V. A power-on reset function is incorporated to ensure repeatable start-up conditions.

Digital control of the TLV5628C and TLV5628I is over a simple 3-wire serial bus that is CMOS compatible and easily interfaced to all popular microprocessor and microcontroller devices. The 12-bit command word comprises 8 bits of data, 3 DAC select bits and a range bit, the latter allowing selection between the times 1 or times 2 output range. The DAC registers are double buffered, allowing a complete set of new values to be written to the device, then all DAC outputs are updated simultaneously through control of the LDAC terminal. The digital inputs feature Schmitt triggers for high noise immunity.

The 16-terminal small-outline D package allows digital control of analog functions in space-critical applications. The TLV5628C is characterized for operation from 0°C to 70°C. The TLV5628I is characterized for operation from ±40°C to 85°C. The TLV5628C and TLV5628I do not require external trimming.

AVAILABLE OPTIONS

PACKAGE

TA |

SMALL OUTLINE |

PLASTIC DIP |

|

(DW) |

(N) |

||

|

|||

|

|

|

|

0°C to 70°C |

TLV5628CDW |

TLV5628CN |

|

|

|

|

|

± 40°C to 85°C |

TLV5628IDW |

TLV5628IN |

|

|

|

|

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1995, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

TLV5628C, TLV5628I

OCTAL 8-BIT DIGITAL-TO-ANALOG CONVERTERS

SLAS108A ± JANUARY 1995 ± REVISED NOVEMBER 1995

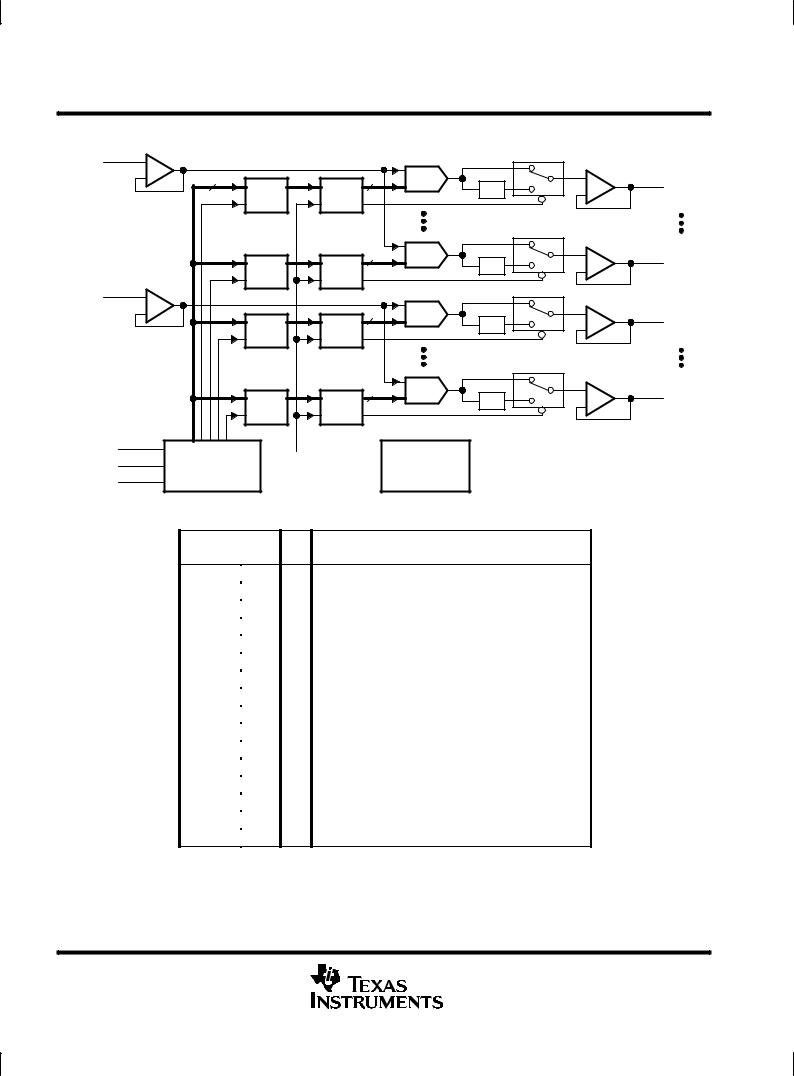

functional block diagram

REF1 |

+ |

|

|

|

|

|

|

|

± |

|

|

|

DAC |

+ |

DACA |

|

9 |

Latch |

Latch |

8 |

× 2 |

± |

|

|

|

||||||

|

|

|

|

|

DAC |

+ |

DACD |

|

|

Latch |

Latch |

8 |

× 2 |

± |

|

|

|

|

|||||

REF2 |

+ |

|

|

|

|

|

|

|

± |

|

|

|

DAC |

+ |

DACE |

|

|

Latch |

Latch |

8 |

× 2 |

± |

|

|

|

|

|||||

|

|

|

|

|

DAC |

+ |

DACH |

|

|

Latch |

Latch |

8 |

× 2 |

± |

|

|

|

|

|

||||

CLK |

Serial |

|

|

|

Power-On |

|

|

DATA |

LDAC |

|

|

|

|

||

Interface |

|

|

|

Reset |

|

|

|

LOAD |

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

Terminal Functions |

|

|

||

|

TERMINAL |

|

|

DESCRIPTION |

|

|

|

|

NAME |

I/O |

|

|

|

|

|

|

NO. |

|

|

|

|

|

|

CLK |

5 |

I |

Serial-interface clock, data enters on the negative edge |

DACA |

2 |

O |

DACA analog output |

|

|

|

|

DACB |

1 |

O |

DACB analog output |

|

|

|

|

DACC |

16 |

O |

DACC analog output |

|

|

|

|

DACD |

15 |

O |

DACD analog output |

|

|

|

|

DACE |

7 |

O |

DACE analog output |

|

|

|

|

DACF |

8 |

O |

DACF analog output |

|

|

|

|

DACG |

9 |

O |

DACG analog output |

|

|

|

|

DACH |

10 |

O |

DACH analog output |

|

|

|

|

DATA |

4 |

I |

Serial-interface digital data input |

|

|

|

|

GND |

3 |

I |

Ground return and reference terminal |

|

|

|

|

LDAC |

13 |

I |

DAC-update latch control |

|

|

|

|

LOAD |

12 |

I |

Serial-interface load control |

|

|

|

|

REF1 |

14 |

I |

Reference voltage input to DACA |

|

|

|

|

REF2 |

11 |

I |

Reference voltage input to DACB |

|

|

|

|

VDD |

6 |

I |

Positive supply voltage |

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TLV5628C, TLV5628I

OCTAL 8-BIT DIGITAL-TO-ANALOG CONVERTERS

SLAS108A ± JANUARY 1995 ± REVISED NOVEMBER 1995

detailed description

The TLV5628 is implemented using eight resistor-string DACs. The core of each DAC is a single resistor with 256 taps, corresponding to the 256 possible codes listed in Table 1. One end of each resistor string is connected to the GND terminal and the other end is fed from the output of the reference input buffer. Monotonicity is maintained by use of the resistor strings. Linearity depends upon the matching of the resistor elements and upon the performance of the output buffer. Because the inputs are buffered, the DACs always present a high-impedance load to the reference sources. There are two input reference terminals; REF1 is used for DACA through DACD and REF2 is used by DACE through DACH.

Each DAC output is buffered by a configurable-gain output amplifier, which can be programmed to times 1 or times 2 gain.

On power-up, the DACs are reset to CODE 0.

Each output voltage is given by: |

|

|

VO(DACA|B|C|D|E|F|G|H) + REF |

CODE |

(1 )RNG bit value) |

256 |

where CODE is in the range of 0 to 255 and the range (RNG) bit is a 0 or 1 within the serial-control word.

data interface

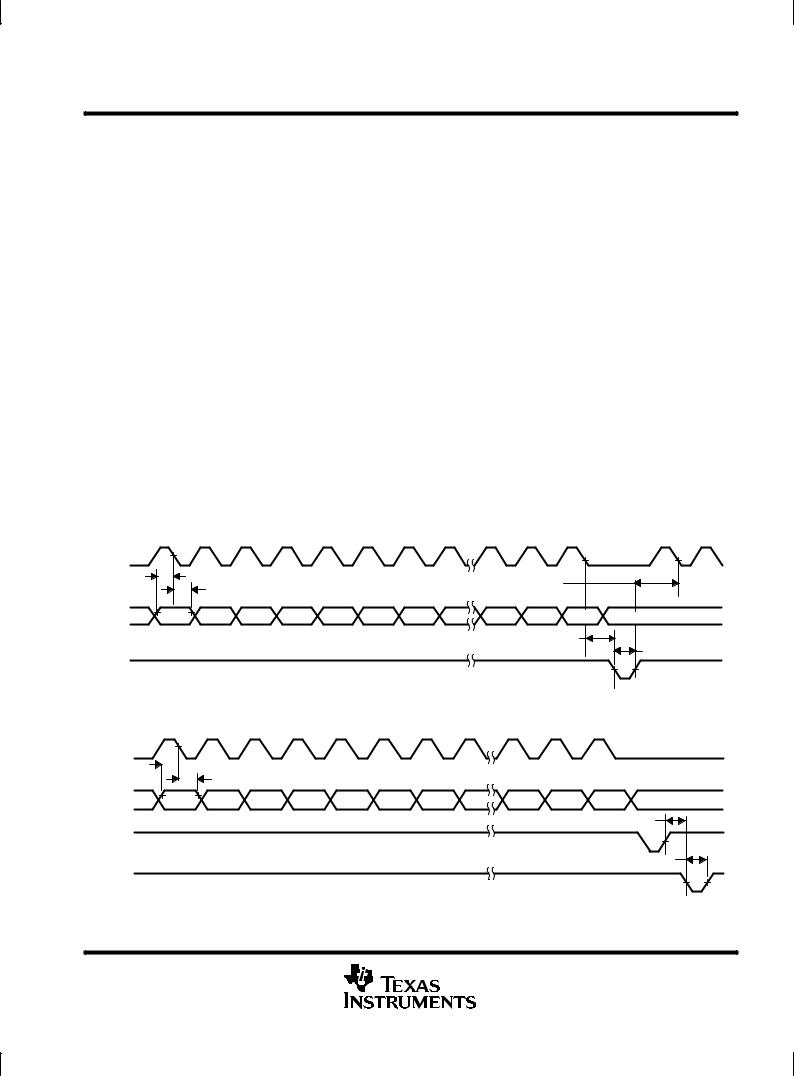

With LOAD high, data is clocked into the DATA terminal on each falling edge of CLK. Once all data bits have been clocked in, LOAD is pulsed low to transfer the data from the serial-input register to the selected DAC as shown in Figure 1. When LDAC is low, the selected DAC output voltage is updated and LOAD goes low. When LDAC is high during serial programming, the new value is stored within the device and can be transferred to the DAC output at a later time by pulsing LDAC low as shown in Figure 2. Data is entered MSB first. Data transfers using two 8 clock cycle periods are shown in Figures 3 and 4.

CLK

DATA

LOAD

CLK

DATA

LOAD

LDAC

tsu(DATA-CLK) |

tsu(LOAD-CLK) |

|

tv(DATA-CLK) |

||

|

A2 |

A1 |

A0 |

RNG |

D7 |

D6 |

D5 |

D4 |

D2 |

D1 |

D0 |

|

|

|

|

|

|

|

|

tsu(CLK-LOAD) |

||

tw(LOAD)

DAC Update

Figure 1. LOAD-Controlled Update (LDAC = Low)

tsu(DATA-CLK) tv(DATA-CLK)

tsu(DATA-CLK) tv(DATA-CLK)

A2 |

A1 |

A0 |

RNG |

D7 |

D6 |

D5 |

D4 |

D2 |

D1 |

D0 |

|

|

|

|

|

|

|

|

|

tsu(LOAD ± LDAC) |

|

|

|

|

|

|

|

|

|

|

|

tw(LDAC) |

DAC Update

Figure 2. LDAC-Controlled Update

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

4

75265 TEXAS DALLAS, •655303 BOX OFFICE POST

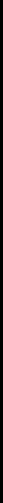

CLK Low

CLK

DATA |

A1 |

A0 |

RNG |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

LOAD

LDAC

Figure 3. Load Controlled Update Using 8-Bit Serial Word (LDAC = Low)

CLK Low

CLK

DATA |

A1 |

A0 |

RNG |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

LOAD

LDAC

Figure 4. LDAC Controlled Update Using 8-Bit Serial Word

1995 NOVEMBER REVISED ± 1995 JANUARY ± SLAS108A

ANALOG-TO-DIGITAL BIT-8 OCTAL |

TLV5628I TLV5628C, |

7±11±94 Date: Release Template |

CONVERTERS |

|

|

TLV5628C, TLV5628I

OCTAL 8-BIT DIGITAL-TO-ANALOG CONVERTERS

SLAS108A ± JANUARY 1995 ± REVISED NOVEMBER 1995

data interface (continued)

Table 2 lists the A2, A1, and A0 bits and the selection of the updated DACs. The RNG bit controls the DAC output range. When RNG = low, the output range is between the applied reference voltage and GND, and when RNG = high, the range is between twice the applied reference voltage and GND.

Table 1. Ideal Output Transfer

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

OUTPUT VOLTAGE |

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

GND |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

(1/256) × REF (1+RNG) |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

(127/256) × REF (1+RNG) |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

(128/256) × REF (1+RNG) |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

• |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

(255/256) × REF (1+RNG) |

|

|

|

|

|

|

|

|

|

Table 2. Serial Input Decode

A2 |

A1 |

A0 |

DAC UPDATED |

|

|

|

|

0 |

0 |

0 |

DACA |

|

|

|

|

0 |

0 |

1 |

DACB |

|

|

|

|

0 |

1 |

0 |

DACC |

|

|

|

|

0 |

1 |

1 |

DACD |

|

|

|

|

1 |

0 |

0 |

DACE |

|

|

|

|

1 |

0 |

1 |

DACF |

|

|

|

|

1 |

1 |

0 |

DACG |

|

|

|

|

1 |

1 |

1 |

DACH |

|

|

|

|

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

5 |

Loading...

Loading...