Texas Instruments TLC0820AIN, TLC0820AIFN, TLC0820AIDWR, TLC0820AIDW, TLC0820ACN Datasheet

...

TLC0820AC, TLC0820AI Advanced LinCMOS HIGH-SPEED 8-BIT ANALOG-TO-DIGITAL

CONVERTERS USING MODIFIED FLASH TECHNIQUES

SLAS064A ± SEPTEMBER 1986 ± REVISED JUNE 1994

DAdvanced LinCMOS Silicon-Gate

Technology

D8-Bit Resolution

DDifferential Reference Inputs

DParallel Microprocessor Interface

DConversion and Access Time Over

Temperature Range

Read Mode . . . 2.5 μs Max

DNo External Clock or Oscillator Components Required

DOn-Chip Track and Hold

DSingle 5-V Supply

DTLC0820A Is Direct Replacement for National Semiconductor ADC0820C/CC and Analog Devices AD7820K/B/T

DB, DW, OR N PACKAGE

(TOP VIEW)

ANLG IN |

|

1 |

20 |

|

|

VCC |

||||||

|

|

|

||||||||||

|

|

|

||||||||||

(LSB) D0 |

|

2 |

19 |

|

|

NC |

||||||

|

|

|

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

3 |

18 |

|

|

OFLW |

|

|||

|

|

|

D2 |

|

4 |

17 |

|

|

D7 (MSB) |

|||

|

|

|

|

|

|

|||||||

|

|

|

D3 |

|

5 |

16 |

|

|

D6 |

|||

|

|

|

|

|

|

|||||||

WR/RDY |

|

6 |

15 |

|

|

D5 |

||||||

|

|

|

||||||||||

MODE |

|

7 |

14 |

|

|

D4 |

||||||

|

|

|

||||||||||

|

|

|

RD |

|

|

8 |

13 |

|

|

CS |

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

INT |

|

|

9 |

12 |

|

|

REF+ |

|||

|

|

|

|

|

|

|||||||

|

GND |

10 |

11 |

|

|

REF± |

||||||

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

FN PACKAGE (TOP VIEW)

description

The |

TLC0820AC and the |

TLC0820AI are |

|

|

|

|

|

|

|

|

D1 |

(LSB)D0 |

ANLGIN |

CC |

NC |

|

|

|

|

|||||

Advanced LinCMOS 8-bit analog-to-digital |

|

|

|

|

|

|

|

|

V |

|

|

|

|

|||||||||||

converters each consisting of two 4-bit flash |

|

|

|

|

|

|

|

3 |

|

2 |

|

1 |

|

20 19 |

|

|

|

|

|

|||||

converters, a 4-bit digital-to-analog converter, a |

|

|

D2 |

|

|

|

4 |

|

|

|

|

|

|

|

|

18 |

|

OFLW |

||||||

summing (error) amplifier, control logic, and a |

|

|

D3 |

|

|

5 |

|

|

|

|

|

|

|

|

17 |

|

D7 (MSB) |

|||||||

result latch circuit. The modified flash technique |

WR/RDY |

|

|

6 |

|

|

|

|

|

|

|

|

16 |

|

D6 |

|||||||||

allows low-power integrated circuitry to complete |

MODE |

|

|

|

7 |

|

|

|

|

|

|

|

|

15 |

|

D5 |

||||||||

|

μ |

|

|

|

RD |

|

|

|

|

8 |

|

|

|

|

|

|

|

|

14 |

|

D4 |

|||

an 8-bit conversion in 1.18 s over temperature. |

|

|

|

|

|

|

|

9 |

|

10 11 12 13 |

|

|

|

|

||||||||||

The on-chip track-and-hold circuit has a 100-ns |

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

sample window and allows these devices to |

|

|

|

|

|

|

|

|

INT |

|

|

REF ± |

|

|

CS |

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

convert continuous analog signals having slew |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

GND |

REF+ |

|

|

|

|

|||||||||||

rates |

of up to 100 mV/μs |

without external |

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

sampling components. TTL-compatible 3-state output drivers and two modes of operation allow

interfacing to a variety of microprocessors. Detailed information on interfacing to most popular microprocessors is readily available from the factory.

AVAILABLE OPTIONS

|

TOTAL |

|

PACKAGE |

|

||

|

|

|

|

|

||

|

|

PLASTIC |

PLASTIC |

|

||

TA |

UNADJUSTED |

SSOP |

PLASTIC DIP |

|||

SMALL OUTLINE |

CHIP CARRIER |

|||||

|

ERROR |

(DB) |

(N) |

|||

|

(DW) |

(FN) |

||||

|

|

|

|

|||

|

|

|

|

|

|

|

0°C to 70°C |

± 1 LSB |

TLC0820ACDB |

TLC0820ACDW |

TLC0820ACFN |

TLC0820ACN |

|

|

|

|

|

|

|

|

± 40°C to 85°C |

± 1 LSB |

Ð |

TLC0820AIDW |

TLC0820AIFN |

TLC0820AIN |

|

|

|

|

|

|

|

|

Advanced LinCMOS is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1994, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

2±1 |

TLC0820AC, TLC0820AI

Advanced LinCMOS HIGH-SPEED 8-BIT ANALOG-TO-DIGITAL

CONVERTERS USING MODIFIED FLASH TECHNIQUES

SLAS064A ± SEPTEMBER 1986 ± REVISED JUNE 1994

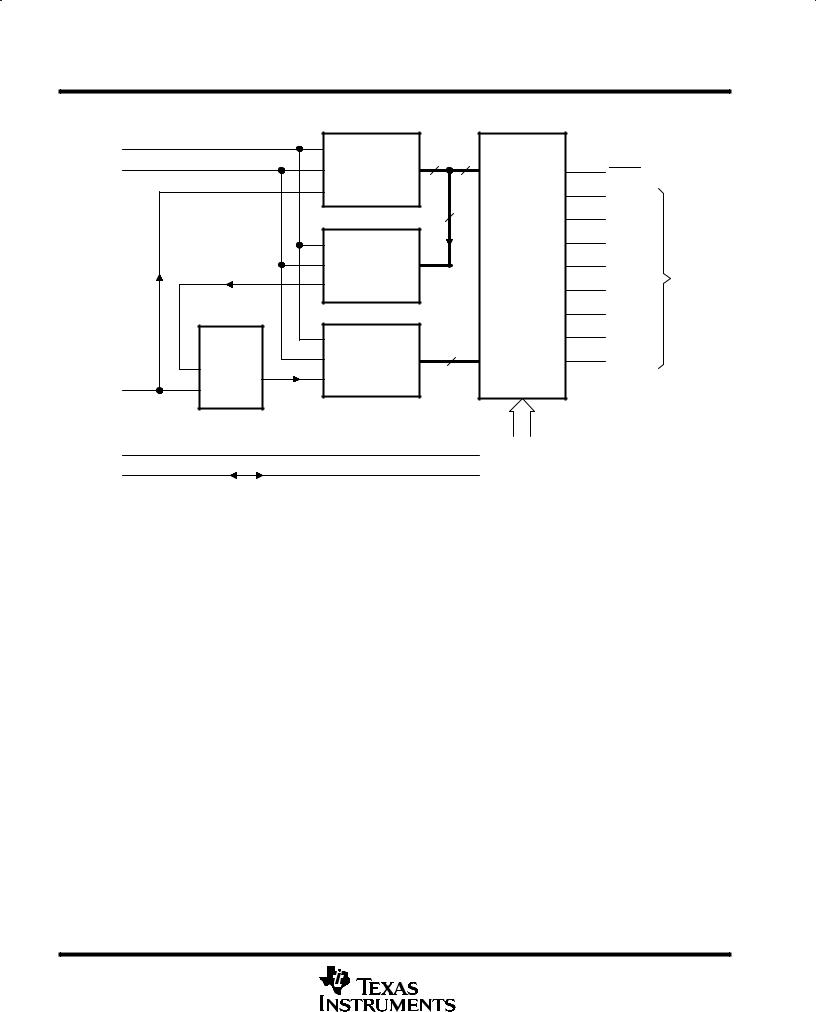

functional block diagram

REF+ |

12 |

4-Bit Flash |

|

|

|

|

|

11 |

4 |

4 |

|

|

|

||

REF ± |

Analog-to-Digital |

18 |

OFLW |

||||

|

Converter |

|

|

|

|||

|

|

|

|

2 |

|

|

|

|

|

(4 MSBs) |

|

|

D0 |

(LSB) |

|

|

|

|

|

|

|

||

|

|

|

|

4 |

3 |

D1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

Output |

4 |

D2 |

|

|

|

4-Bit |

|

5 |

|

||

|

|

Digital-to-Analog |

|

Latch |

D3 |

|

|

|

|

Converter |

|

and |

|

Digital |

|

|

|

|

14 |

|

|||

|

|

|

|

3-State |

D4 |

Outputs |

|

|

|

|

|

Buffers |

|

|

|

|

|

|

|

15 |

|

|

|

|

|

|

|

|

D5 |

|

|

|

|

|

|

|

|

|

|

|

Summing |

4-Bit Flash |

|

|

16 |

D6 |

|

|

|

|

|

|

|||

|

Amplifier |

Analog-to-Digital |

|

4 |

17 |

D7 |

(MSB) |

|

± 1 |

Converter |

|

|

|

||

|

(4 LSBs) |

|

|

|

|

|

|

ANLG IN |

1 |

|

|

|

|

|

|

|

|

|

|

|

|

||

+ 1 |

|

|

|

|

|

|

|

7 |

|

|

|

|

|||||||

|

MODE |

|

|

|

|

||||||

|

|

6 |

|

|

|

|

|||||

WR/RDY |

Timing |

9 |

|

|

|||||||

|

|

|

|

13 |

and |

|

|

INT |

|||

|

|

|

|

|

|

||||||

|

|||||||||||

|

|

|

|

CS |

|

Control |

|

|

|

||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

8 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|||

|

|

|

RD |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

2±2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TLC0820AC, TLC0820AI |

||||||||

|

|

|

|

|

|

|

|

|

|

Advanced LinCMOS HIGH-SPEED 8-BIT ANALOG-TO-DIGITAL |

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CONVERTERS USING MODIFIED FLASH TECHNIQUES |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SLAS064A ± SEPTEMBER 1986 ± REVISED JUNE 1994 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Terminal Functions |

|||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TERMINAL |

I/O |

|

|

|

|

|

|

|

|

|

|

|

|

|

DESCRIPTION |

|

|||||||||||||||

|

NAME |

NO. |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ANLG IN |

1 |

I |

Analog input |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

13 |

I |

Chip select. |

|

must be low in order for |

|

|

or |

|

to be recognized by the ADC. |

|

|||||||||||||||||

|

CS |

|

|

|

|

|

CS |

RD |

WR |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

D0 |

2 |

O |

Digital, 3-state output data, bit 1 (LSB) |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

D1 |

3 |

O |

Digital, 3-state output data, bit 2 |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

D2 |

4 |

O |

Digital, 3-state output data, bit 3 |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

D3 |

5 |

O |

Digital, 3-state output data, bit 4 |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

D4 |

14 |

O |

Digital, 3-state output data, bit 5 |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

D5 |

15 |

O |

Digital, 3-state output data, bit 6 |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

D6 |

16 |

O |

Digital, 3-state output data, bit 7 |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

D7 |

17 |

O |

Digital, 3-state output data, bit 8 (MSB) |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

GND |

10 |

|

Ground |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

9 |

O |

Interrupt. In the write-read mode, the interrupt output |

|

going low indicates that the internal count-down delay |

|

||||||||||||||||||||||

|

INT |

|

|

|

(INT) |

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

time, td(int), is complete and the data result is in the output latch. The delay |

time td(int) is typically 800 ns starting |

|

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

after the rising edge of WR (see operating characteristics and Figure 3). If |

|

|

|

|

|

|

|

|

|

||||||||||||||||

|

|

|

|

|

|

|

|

|

RD goes low prior to the end of td(int), |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

INT goes low at the end of td(RIL) and the conversion results are available sooner (see Figure 2). INT is reset by |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

the rising edge of either RD or CS. |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

MODE |

7 |

I |

Mode select. MODE is internally tied to GND through a 50-μA current source, which acts like a pulldown resistor. |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

When MODE is low, the read mode is selected. When MODE is high, the write-read mode is selected. |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

NC |

19 |

|

No internal connection |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

18 |

O |

Overflow. Normally |

|

|

|

is a logical high. However, if the analog input is higher than Vref+, |

|

|

will be low at |

|

|||||||||||||||||

|

OFLW |

|

OFLW |

OFLW |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

the end of conversion. It can be used to cascade two or more devices to improve resolution (9 or 10 bits). |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

8 |

I |

Read. In the write-read mode with |

|

low, the 3-state data outputs D0 through D7 are activated when |

|

goes |

|

||||||||||||||||||||

|

RD |

|

|

CS |

RD |

|

||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

low. RD can also be used to increase the conversion speed by reading data prior to the end of the internal |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

count-down delay time. As a result, the data transferred to the output latch is latched after the falling edge of RD. |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

In the read mode with |

CS |

low, the conversion starts with RD going low. RD also enables the 3-state data outputs |

|

||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

on completion of the conversion. RDY going into the high-impedance state and INT going low indicate completion |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

of the conversion. |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

REF ± |

11 |

I |

Reference voltage. REF ± is placed on the bottom of the resistor ladder. |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

REF + |

12 |

I |

Reference voltage. REF + is placed on the top of the resistor ladder. |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||||||||

|

VCC |

20 |

|

Power supply voltage |

|

|||||||||||||||||||||||||||||

|

|

|

|

|

|

|

6 |

I/O |

Write ready. In the write-read mode with |

|

|

low, the conversion is started on the falling edge of the |

|

|

input signal. |

|

||||||||||||||||||

|

WR/RDY |

CS |

WR |

|

||||||||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

The result of the conversion is strobed into the output latch after the internal count-down delay time, td(int), provided |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

that the RD input does not go low prior to this time. The delay time td(int) is approximately 800 ns. In the read mode, |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

RDY (an open-drain output) goes low after the falling edge of CS and goes into the high-impedance state when |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

the conversion is strobed into the output latch. It is used to simplify the interface to a microprocessor system. |

|

||||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

2±3 |

TLC0820AC, TLC0820AI

Advanced LinCMOS HIGH-SPEED 8-BIT ANALOG-TO-DIGITAL

CONVERTERS USING MODIFIED FLASH TECHNIQUES

SLAS064A ± SEPTEMBER 1986 ± REVISED JUNE 1994

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)²

Supply voltage, VCC (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10 V Input voltage range, all inputs (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±0.2 V to VCC +0.2 V Output voltage range, all outputs (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±0.2 V to VCC +0.2 V Operating free-air temperature range: TLC0820AC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 0°C to 70°C

TLC0820AI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±40°C to 85°C Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ±65°C to 150°C Case temperature for 10 seconds: FN package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 260°C Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: DB, DW or N package . . . . . . . . . . . 260°C

²Stresses beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. NOTE 1: All voltages are with respect to network GND.

recommended operating conditions

|

|

|

|

|

|

|

|

|

MIN |

NOM |

MAX |

UNIT |

|

|

|

|

|

|

|

|

|

|

|

|

|

Supply voltage, VCC |

|

|

|

|

|

|

|

|

4.5 |

5 |

8 |

V |

Analog input voltage |

|

|

|

|

|

|

|

|

± 0.1 |

|

VCC + 0.1 |

V |

Positive reference voltage, Vref + |

|

|

|

|

|

|

|

|

Vref ± |

|

VCC |

V |

Negative reference voltage, Vref ± |

|

|

|

|

|

|

|

|

GND |

|

Vref+ |

V |

High-level input voltage, VIH |

VCC = 4.75 V to 5.25 V |

|

CS, |

|

WR/RDY, RD |

2 |

|

|

V |

|||

|

|

|

|

|||||||||

MODE |

3.5 |

|

|

|||||||||

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

0.8 |

|

Low-level input voltage, VIL |

VCC = 4.75 V to 5.25 V |

|

CS, |

|

WR/RDY, RD |

|

|

V |

||||

|

|

|

|

|||||||||

MODE |

|

|

1.5 |

|||||||||

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

Pulse duration, write in write-read mode, tw(W) (see Figures 2, 3, and 4) |

0.5 |

|

50 |

μs |

||||||||

Operating free-air temperature, TA |

TLC0820AC |

0 |

|

70 |

°C |

|||||||

|

|

|

|

|

|

|

|

|

|

|

||

TLC0820AI |

± 40 |

|

85 |

|||||||||

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

2±4 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

Loading...

Loading...