Texas Instruments TLC1541IN, TLC1541IFN, TLC1541IDWR, TLC1541IDW, TLC1541CN Datasheet

...

|

|

|

|

|

|

|

|

|

|

TLC1541 |

|

|

|

10-BIT ANALOG-TO-DIGITAL CONVERTER |

|||||||||

|

|

WITH SERIAL CONTROL AND 11 INPUTS |

|||||||||

|

|

SLAS073C ± DECEMBER 1995 ± REVISED AUGUST 1996 |

|||||||||

|

|

|

|

|

|

|

|

||||

D 10-Bit Resolution A/D Converter |

DW OR N PACKAGE |

||||||||||

D Microprocessor Peripheral or Standalone |

|

|

(TOP VIEW) |

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

||

|

Operation |

INPUT A0 |

|

|

|

|

|

V |

|

|

|

|

|

1 |

20 |

|

|

CC |

|||||

D On-Chip 12-Channel Analog Multiplexer |

|

|

|

||||||||

INPUT A1 |

|

|

|

|

|

|

|||||

|

2 |

19 |

|

|

SYSTEM CLOCK |

||||||

D Built-In Self-Test Mode |

|

|

|

||||||||

INPUT A2 |

|

3 |

18 |

|

|

I/O CLOCK |

|||||

|

|

|

|||||||||

|

Software-Controllable Sample-and-Hold |

|

|

|

|||||||

D |

INPUT A3 |

|

4 |

17 |

|

|

ADDRESS INPUT |

||||

|

|

|

|||||||||

|

Function |

INPUT A4 |

|

5 |

16 |

|

|

DATA OUT |

|||

|

|

|

|

||||||||

D Total Unadjusted Error . . . ± 1 LSB Max |

INPUT A5 |

|

6 |

15 |

|

|

CS |

|

|||

|

|

|

|

|

|||||||

D Pinout and Control Signals Compatible |

INPUT A6 |

|

7 |

14 |

|

|

REF+ |

||||

|

|

|

|||||||||

INPUT A7 |

|

8 |

13 |

|

|

REF± |

|||||

|

With TLC540 and TLC549 Families of 8-Bit |

|

|

|

|||||||

|

INPUT A8 |

9 |

12 |

|

|

INPUT A10 |

|||||

|

A/D Converters |

|

|

||||||||

|

GND |

10 |

11 |

|

|

INPUT A9 |

|||||

D |

CMOS Technology |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

||

PARAMETER |

VALUE |

|

|

Channel Acquisition Sample Time |

5.5 ms |

Conversion Time (Max) |

21 ms |

Samples Per Second (Max) |

32 × 103 |

Power Dissipation (Max) |

6 mW |

|

|

description

The TLC1541 is a CMOS A/D converter built around a 10-bit switched-capacitor successiveapproximation A/D converter. The device is designed for serial interface to a microprocessor or peripheral using a 3-state output with up to four control inputs (including independent SYSTEM CLOCK, I/O CLOCK, chip select [CS], and ADDRESS INPUT). A 2.1-MHz system clock for the TLC1541, with a design that includes simultaneous read/write operation, allows highspeed data transfers and sample rates up to 32 258 samples per second. In addition to the high-speed converter and versatile control logic, there is an on-chip, 12-channel analog multiplexer that can be used to sample any one of 11 inputs or an internal self-test voltage and a sample-and- hold function that operates automatically.

|

FN PACKAGE |

|

||||

|

|

(TOP VIEW) |

|

|||

|

INPUTA2 |

INPUTA1 |

INPUTA0 |

V |

SYSTEMCLOCK |

|

|

|

|

|

CC |

|

|

INPUT A3 |

3 |

2 |

1 |

20 19 |

I/O CLOCK |

|

4 |

|

|

|

18 |

||

INPUT A4 |

5 |

|

|

|

17 |

ADDRESS INPUT |

INPUT A5 |

6 |

|

|

|

16 |

DATA OUT |

INPUT A6 |

7 |

|

|

|

15 |

CS |

INPUT A7 |

8 |

|

|

|

14 |

REF+ |

|

9 |

10 11 12 13 |

|

|||

|

INPUT A8 |

GND |

INPUT A9 |

INPUT A10 |

REF± |

|

AVAILABLE OPTIONS

|

|

PACKAGE |

|

|

|

|

|

|

|

TA |

SMALL |

PLASTIC CHIP |

PLASTIC |

|

OUTLINE |

CARRIER |

DIP |

||

|

||||

|

(DW) |

(FN) |

(N) |

|

|

|

|

|

|

0°C to 70°C |

TLC1541CDW |

TLC1541CFN |

TLC1541CN |

|

|

|

|

|

|

± 40°C to 85°C |

TLC1541IDW |

TLC1541IFN |

TLC1541IN |

|

|

|

|

|

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1996, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

TLC1541

10-BIT ANALOG-TO-DIGITAL CONVERTER WITH SERIAL CONTROL AND 11 INPUTS

SLAS073C ± DECEMBER 1995 ± REVISED AUGUST 1996

description (continued)

The converters incorporated in the TLC1541 feature differential high-impedance reference inputs that facilitate ratiometric conversion, scaling, and analog circuitry isolation from logic and supply noises. A totally switched-capacitor design allows low-error conversion in 21 μs over the full operating temperature range.

The TLC1541 is available in DW, FN, and N packages. The C-suffix versions are characterized for operation from 0°C to 70°C. The I-suffix versions are characterized for operation from ±40°C to 85°C.

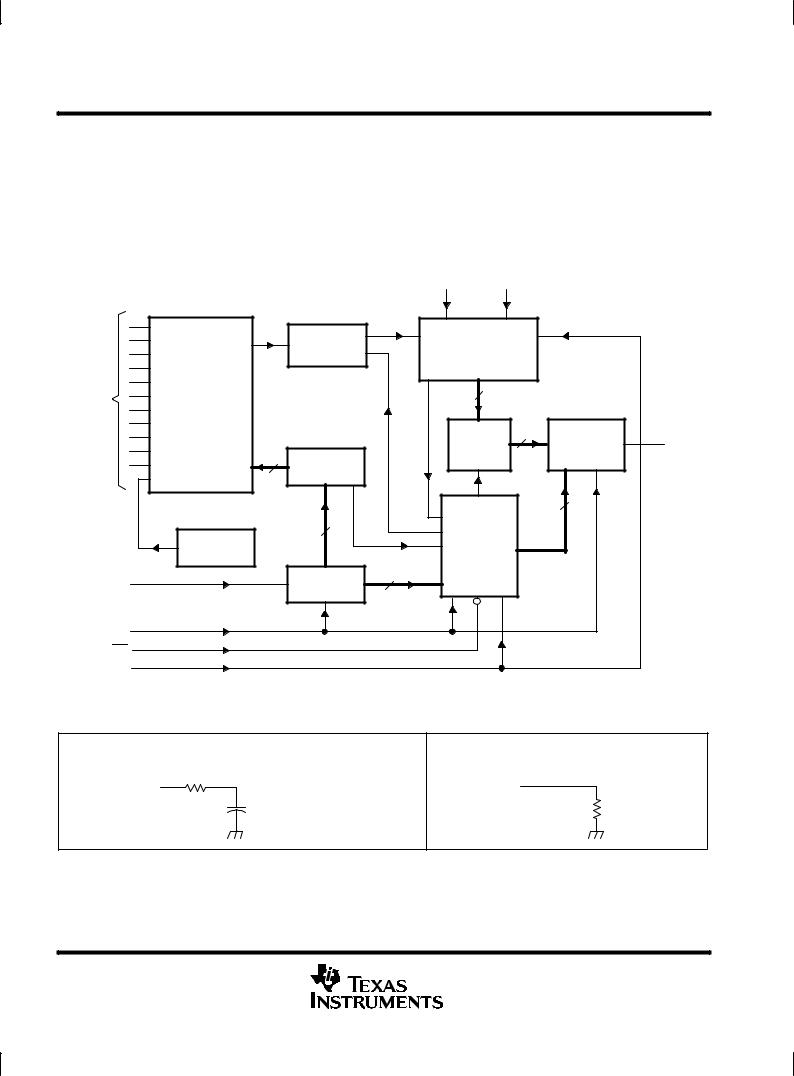

functional block diagram |

|

|

|

|

|

|

|

||

|

|

|

|

REF+ |

REF± |

|

|

|

|

|

|

|

|

14 |

13 |

|

|

|

|

|

1 |

|

|

|

10-Bit |

|

|

|

|

|

2 |

|

Sample and |

|

|

|

|

|

|

|

3 |

|

Switched-Capacitors |

|

|

|

|||

|

|

Hold |

|

|

|

||||

|

|

Analog-to-Digital |

|

|

|

||||

|

4 |

|

|

|

|

||||

|

|

|

|

|

|

||||

|

|

|

Converter |

|

|

|

|

||

|

5 |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

ANALOG |

6 |

12-Channel |

|

|

10 |

|

|

|

|

INPUTS |

7 |

Analog |

|

|

|

|

|

|

|

|

8 |

Multiplexer |

|

|

|

|

|

|

|

|

9 |

|

|

Output |

10 |

10-to-1 Data |

16 |

DATA |

|

|

11 |

|

|

|

Data |

|

Selector and |

||

|

4 |

|

|

|

|

OUT |

|||

|

12 |

Input Address |

Register |

|

Driver |

|

|||

|

|

|

|

||||||

|

|

|

Register |

|

|

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

Self-Test |

4 |

Control Logic |

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

and I/O |

|

|

|

|

||

|

|

Reference |

|

|

|

|

|

||

|

|

|

Counters |

|

|

|

|

||

|

|

|

|

|

|

|

|

||

ADDRESS |

17 |

|

Input |

2 |

|

|

|

|

|

INPUT |

|

|

Multiplexer |

|

|

|

|

|

|

I/O CLOCK |

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

CS |

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SYSTEM |

19 |

|

|

|

|

|

|

|

|

CLOCK |

|

|

|

|

|

|

|

|

|

typical equivalent inputs

INPUT CIRCUIT IMPEDANCE DURING SAMPLING MODE

1 kΩ TYP

INPUT

A0 ± A10 Ci = 60 pF TYP (equivalent input capacitance)

INPUT CIRCUIT IMPEDANCE DURING HOLD MODE

INPUT A0 ± A10

5 MΩ TYP

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TLC1541 10-BIT ANALOG-TO-DIGITAL CONVERTER WITH SERIAL CONTROL AND 11 INPUTS

SLAS073C ± DECEMBER 1995 ± REVISED AUGUST 1996

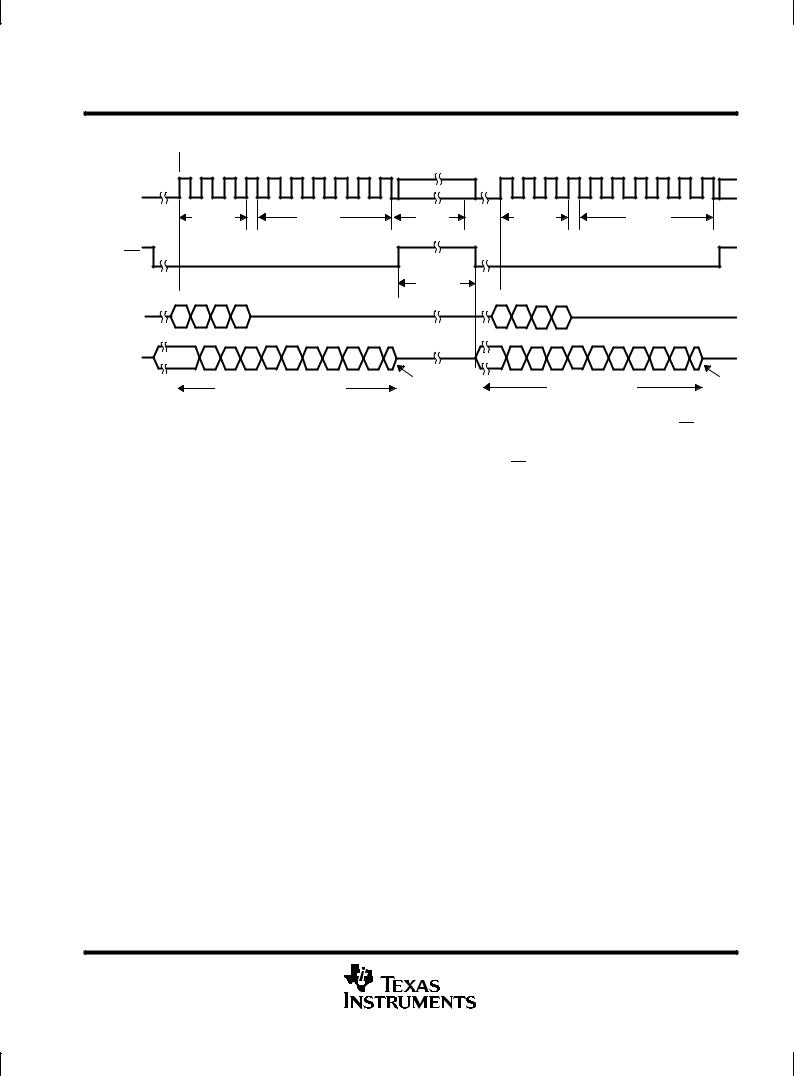

operating sequence

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

8 |

9 |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O |

|

|

|

|

|

|

|

|

|

|

|

Don't |

Care |

|

|

|

|

|

|

|

|

|

|

CLOCK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Access |

|

|

|

|

Sample |

|

tconv |

Access |

|

|

|

|

Sample |

|

|||||||

|

|

Cycle B |

|

|

|

|

Cycle B |

|

Cycle C |

|

|

|

|

Cycle C |

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

See Note A |

|

|

|

|

|

|

|

|

|

|

|

CS |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

See Note C |

|

|

|

|

|

|

twH(CS) |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

MSB |

|

|

|

LSB |

|

|

Don't Care |

|

MSB |

|

|

LSB |

|

|

|

|

Don't Care |

|||||

ADDRESS |

B3 |

B2 |

B1 |

B0 |

|

|

|

C3 |

C2 |

C1 |

C0 |

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

INPUT |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

HI-Z State |

|

|

|

|

|

|

|

|

HI-Z |

||

DATA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

State |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

A9 |

A8 |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

B9 |

B8 |

B7 |

B6 |

B5 |

B4 |

B3 |

B2 |

B1 |

B0 |

||||

OUT |

|||||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Previous Conversion Data A |

|

A9 |

|

|

Conversion Data B |

|

B9 |

||||||||||||

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

MSB |

|

|

|

|

|

|

|

|

|

LSB MSB |

MSB |

|

|

|

|

|

|

|

|

LSB MSB |

||

|

(see Note B) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

NOTES: A. The conversion cycle, which requires 44 system clock periods, initiates on the tenth falling edge of the I/O clock after CS goes low for the channel whose address exists in memory at that time. When CS is kept low during conversion, the I/O clock must remain low for at least 44 system clock cycles to allow the conversion to complete.

B.The most significant bit (MSB) is automatically placed on the DATA OUT bus after CS is brought low. The remaining nine bits (A8±A0) clock out on the first nine I/O clock falling edges.

C.To minimize errors caused by noise at the CS input, the internal circuitry waits for three system clock cycles (or less) after a chip-select falling edge is detected before responding to control input signals. Therefore, no attempt should be made to clock-in address data until the minimum chip-select setup time elapses.

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)²

Supply voltage, VCC (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . |

. . . . . . . . . 6.5 |

V |

Input voltage range, VI (any input) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

±0.3 V to VCC + 0.3 |

V |

|

Output voltage range, VO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

±0.3 V to VCC + 0.3 |

V |

|

Peak input current (any input) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . |

. . . . . . ± 10 mA |

|

Peak total input current (all inputs) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . |

. . . . . . ± 30 mA |

|

Operating free-air temperature range, TA: C suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . |

. . 0°C to 70°C |

|

I suffix . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . |

±40°C to 85°C |

|

Storage temperature range, Tstg . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . |

±65°C to 150°C |

|

Case temperature for 10 seconds, TC: FN package . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . |

. . . . . . . 260°C |

|

Lead temperature 1,6 mm (1/16 inch) from the case for 10 seconds: DW or N package . . . . |

. . . . . . . 260°C |

||

²Stresses beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not

implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to digital ground with REF ± and GND wired together (unless otherwise noted).

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

TLC1541

10-BIT ANALOG-TO-DIGITAL CONVERTER WITH SERIAL CONTROL AND 11 INPUTS

SLAS073C ± DECEMBER 1995 ± REVISED AUGUST 1996

recommended operating conditions

|

|

|

|

|

|

|

MIN |

NOM |

MAX |

UNIT |

|

|

|

|

|

|

|

|

|

|

|

Supply voltage, VCC |

4.75 |

5 |

5.5 |

V |

||||||

Positive reference voltage, Vref + (see Note 2) |

2.5 |

VCC |

VCC + 0.1 |

V |

||||||

Negative reference voltage, Vref ± (see Note 2) |

± 0.1 |

0 |

2.5 |

V |

||||||

Differential reference voltage, Vref + ± Vref ± (see Note 2) |

1 |

VCC |

VCC + 0.2 |

V |

||||||

Analog input voltage (see Note 2) |

0 |

|

VCC |

V |

||||||

High-level control input voltage, VIH |

2 |

|

|

V |

||||||

Low-level control input voltage, VIL |

|

|

0.8 |

V |

||||||

Input/output clock frequency, fclock(I/O) |

0 |

|

1.1 |

MHz |

||||||

System clock frequency, fclock(SYS) |

fclock(I/O) |

|

2.1 |

MHz |

||||||

Setup time, address bits before I/O CLOCK↑, tsu(A) |

400 |

|

|

ns |

||||||

Hold time, address bits after I/O CLOCK↑, th(A) |

0 |

|

|

ns |

||||||

|

|

|

|

|

|

|

|

|

|

System |

Setup time, CS low before clocking in first address bit, tsu(CS) |

|

|

|

|||||||

3 |

|

|

clock |

|||||||

(see Note 3 and Operating Sequence) |

|

|

||||||||

|

|

|

cycles |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

System |

Pulse duration, |

CS |

high during conversion, twH(CS) (see Operating Sequence) |

44 |

|

|

clock |

||||

|

|

|

|

|

|

|

|

|

|

cycles |

|

|

|

|

|

|

|

||||

Pulse duration, SYSTEM CLOCK high, twH(SYS) |

210 |

|

|

ns |

||||||

Pulse duration, SYSTEM CLOCK low, twL(SYS) |

190 |

|

|

ns |

||||||

Pulse duration, I/O CLOCK high, twH(I/O) |

404 |

|

|

ns |

||||||

Pulse duration, I/O CLOCK low, twL(I/O) |

404 |

|

|

ns |

||||||

|

|

|

|

|

System |

fclock(SYS) ≤ 1048 kHz |

|

|

30 |

ns |

Clock transition time (see Note 4) |

fclock(SYS) > 1048 kHz |

|

|

20 |

||||||

|

|

|

|

|||||||

I/O |

fclock(I/O) ≤ 525 kHz |

|

|

100 |

ns |

|||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

fclock(I/O) > 525 kHz |

|

|

40 |

||

|

|

|

|

|

|

|

|

|

||

Operating free-air temperature, TA |

C suffix |

0 |

|

70 |

°C |

|||||

|

|

|

|

|

||||||

I suffix |

± 40 |

|

85 |

|||||||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

NOTES: 2. Analog input voltages greater than that applied to REF + convert as all ones (1111111111), while input voltages less than that applied to REF ± convert as all zeros (0000000000). For proper operation, REF + voltage must be at least 1 V higher than REF ± voltage. Also, the total unadjusted error may increase as this differential reference voltage falls below 4.75 V.

3.To minimize errors caused by noise at the chip select input, the internal circuitry waits for three system clock cycles (or less) after a chip select falling edge is detected before responding to control input signals. Therefore, no attempt should be made to clock in an address until the minimum chip select setup time elapses.

4.The amount of time required for the clock input signal to fall from VIH min to VIL max or to rise from VIL max to VIH min. In the vicinity of normal room temperature, the devices function with input clock transition time as slow as 2 ms for remote data acquisition applications where the sensor and the A/D converter are placed several feet away from the controlling microprocessor.

4 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

Loading...

Loading...