Texas Instruments TL074ACN, TL074ACNS, TL074ACDR, TL074ACJ, TL074ACD Datasheet

...

TL071, TL071A, TL071B, TL072

TL072A, TL072B, TL074, TL074A, TL074B

LOW-NOISE JFET-INPUT OPERATIONAL AMPLIFIERS

|

|

|

SLOS080D ± SEPTEMBER 1978 ± REVISED AUGUST 1996 |

||

|

|

|

|

|

|

D |

Low Power Consumption |

D |

Low Noise |

||

D Wide Common-Mode and Differential |

|

Vn = 18 nV/√ |

Hz |

Typ at f = 1 kHz |

|

|

Voltage Ranges |

D High Input Impedance . . . JFET Input Stage |

|||

D Low Input Bias and Offset Currents |

D |

Internal Frequency Compensation |

|||

D |

Output Short-Circuit Protection |

D |

Latch-Up-Free Operation |

||

D Low Total Harmonic Distortion |

D High Slew Rate . . . 13 V/ μs Typ |

||||

|

0.003% Typ |

D Common-Mode Input Voltage Range |

|||

|

|

|

Includes VCC + |

||

description

The JFET-input operational amplifiers in the TL07_ series are designed as low-noise versions of the TL08_ series amplifiers with low input bias and offset currents and fast slew rate. The low harmonic distortion and low noise make the TL07_ series ideally suited for high-fidelity and audio preamplifier applications. Each amplifier features JFET inputs (for high input impedance) coupled with bipolar output stages integrated on a single monolithic chip.

The C-suffix devices are characterized for operation from 0°C to 70°C. The I-suffix devices are characterized for operation from ±40°C to 85°C. The M-suffix devices are characterized for operation over the full military temperature range of ±55°C to 125°C.

AVAILABLE OPTIONS

|

|

|

|

|

PACKAGE |

|

|

|

||

|

VIOmax |

|

|

|

|

|

|

|

|

|

TA |

SMALL |

CHIP |

CERAMIC |

CERAMIC |

PLASTIC |

PLASTIC |

TSSOP |

FLAT |

||

AT 25°C |

OUTLINE |

CARRIER |

DIP |

DIP |

DIP |

DIP |

PACKAGE |

PACKAGE |

||

|

|

(D)² |

(FK) |

(J) |

(JG) |

(N) |

(P) |

(PW) |

(W) |

|

|

10 mV |

TL071CD |

|

|

|

|

TL071CP |

TL071CPWLE |

|

|

|

6 mV |

TL071ACD |

Ð |

Ð |

Ð |

Ð |

TL071ACP |

Ð |

Ð |

|

|

3 mV |

TL071BCD |

|

|

|

|

TL071BCP |

Ð |

|

|

|

|

|

|

|

|

|

|

|

|

|

0°C to |

10 mV |

TL072CD |

|

|

|

|

TL072CP |

TL072CPWLE |

|

|

6 mV |

TL072ACD |

Ð |

Ð |

Ð |

Ð |

TL072ACP |

Ð |

Ð |

||

70°C |

||||||||||

3 mV |

TL072BCD |

|

|

|

|

TL072BCP |

Ð |

|

||

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

10 mV |

TL074CD |

|

|

|

TL074CN |

|

TL074CPWLE |

|

|

|

6 mV |

TL074ACD |

Ð |

Ð |

Ð |

TL074ACN |

Ð |

Ð |

Ð |

|

|

3 mV |

TL074BCD |

|

|

|

TL074BCN |

|

Ð |

|

|

|

|

|

|

|

|

|

|

|

|

|

±40°C to |

|

TL071ID |

|

|

|

Ð |

TL071IP |

|

|

|

6 mV |

TL072ID |

Ð |

Ð |

Ð |

Ð |

TL072IP |

Ð |

Ð |

||

85°C |

||||||||||

|

TL074ID |

|

|

|

TL074IN |

Ð |

|

|

||

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

±55°C to |

6 mV |

|

TL071MFK |

Ð |

TL071MJG |

Ð |

Ð |

|

Ð |

|

6 mV |

Ð |

TL072MFK |

Ð |

TL072MJG |

Ð |

TL072MP |

Ð |

Ð |

||

125°C |

||||||||||

9 mV |

|

TL074MFK |

TL074MJ |

Ð |

TL074MN |

Ð |

|

TL074MW |

||

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

²The D package is available taped and reeled. Add the suffix R to the device type (e.g., TL071CDR). The PW package is only available left-ended taped and reeled (e.g., TL072CPWLE).

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1996, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

TL071, TL071A, TL071B, TL072

TL072A, TL072B, TL074, TL074A, TL074B LOW-NOISE JFET-INPUT OPERATIONAL AMPLIFIERS

SLOS080D ± SEPTEMBER 1978 ± REVISED AUGUST 1996

TL071, TL071A, TL071B |

TL072, TL072A, TL072B |

D, JG, P, OR PW PACKAGE |

D, JG, P, OR PW PACKAGE |

(TOP VIEW) |

(TOP VIEW) |

OFFSET N1 |

1 |

8 |

NC |

1OUT |

|

1 |

8 |

|

VCC + |

|

|

||||||||

IN± |

|

|

VCC + |

1IN± |

|

|

|

|

|

2 |

7 |

|

2 |

7 |

|

2OUT |

|||

IN+ |

3 |

6 |

OUT |

1IN+ |

|

3 |

6 |

|

2IN± |

|

|

||||||||

VCC ± |

4 |

5 |

OFFSET N2 |

VCC ± |

|

4 |

5 |

|

2IN+ |

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TL071 |

|

|

|

|

|

|

TL072 |

|

|

||

|

FK PACKAGE |

|

|

|

FK PACKAGE |

|

||||||||

|

|

(TOP VIEW) |

|

|

|

NC |

(TOP VIEW) |

|

||||||

|

|

N1 |

|

|

|

|

|

|

1OUT |

NC |

V |

NC |

|

|

|

|

OFFSET |

|

|

|

|

|

|

|

|

|

CC+ |

|

|

|

NC |

NC |

NC |

NC |

|

NC |

|

3 |

2 |

1 |

20 19 |

NC |

||

|

|

|

|

|

|

|

4 |

|

|

|

|

18 |

||

NC |

3 |

2 |

1 |

20 19 |

NC |

1IN ± |

5 |

|

|

|

|

17 |

2OUT |

|

4 |

|

|

|

18 |

NC |

6 |

|

|

|

|

16 |

NC |

||

IN ± |

5 |

|

|

|

17 |

VCC + |

1IN + |

7 |

|

|

|

|

15 |

2IN ± |

NC |

6 |

|

|

|

16 |

NC |

NC |

8 |

|

|

|

|

14 |

NC |

IN + |

7 |

|

|

|

15 |

OUT |

|

|

9 |

10 11 12 13 |

|

|||

NC |

8 |

±CC |

NC |

N2 |

14 |

NC |

|

|

NC |

± |

NC |

2IN+ |

NC |

|

|

NC |

NC |

|

|

|

V |

|

|||||||

|

9 |

10 11 12 13 |

|

|

|

|

CC |

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

V |

|

OFFSET |

|

|

|

|

|

|

|

|

|

|

TL074, TL074A, TL074B D, J, N, OR PW PACKAGE TL074 . . . W PACKAGE (TOP VIEW)

1OUT |

|

1 |

14 |

|

4OUT |

|

|

||||

1IN ± |

|

2 |

13 |

|

4IN ± |

|

|

||||

1IN + |

|

3 |

12 |

|

4IN + |

|

|

||||

VCC + |

|

4 |

11 |

|

VCC ± |

|

|

||||

|

|

||||

2IN + |

|

5 |

10 |

|

3IN + |

2IN ± |

|

6 |

9 |

|

3IN ± |

|

|

||||

2OUT |

|

7 |

8 |

|

3OUT |

|

|

||||

|

|

|

|

|

|

TL074

FK PACKAGE (TOP VIEW)

|

1IN ± |

1OUT |

NC |

4OUT |

4IN ± |

|

1IN+ |

3 |

2 |

1 |

20 19 |

4IN+ |

|

4 |

|

|

|

18 |

||

NC |

5 |

|

|

|

17 |

NC |

VCC+ |

6 |

|

|

|

16 |

VCC ± |

NC |

7 |

|

|

|

15 |

NC |

2IN+ |

8 |

|

|

|

14 |

3IN+ |

|

9 10 11 12 13 |

|

||||

|

2IN± |

2OUT |

NC |

3OUT |

3IN± |

|

NC ± No internal connection

symbols

TL071

OFFSET N1 |

|

|

|

|

|

|

|

TL072 (each amplifier) |

|||

|

|

|

|

|

|

|

TL074 (each amplifier) |

||||

|

|

|

|

|

|

|

|

||||

IN + |

|

|

+ |

|

|

OUT |

IN + |

|

|

OUT |

|

|

|

|

|

|

+ |

|

|||||

|

|

|

|

||||||||

|

|

|

|

|

|||||||

IN ± |

|

|

± |

|

|

IN ± |

|

± |

|

||

|

|

|

|

||||||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

||||

OFFSET N2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TL071, TL071A, TL071B, TL072

TL072A, TL072B, TL074, TL074A, TL074B

LOW-NOISE JFET-INPUT OPERATIONAL AMPLIFIERS

SLOS080D ± SEPTEMBER 1978 ± REVISED AUGUST 1996

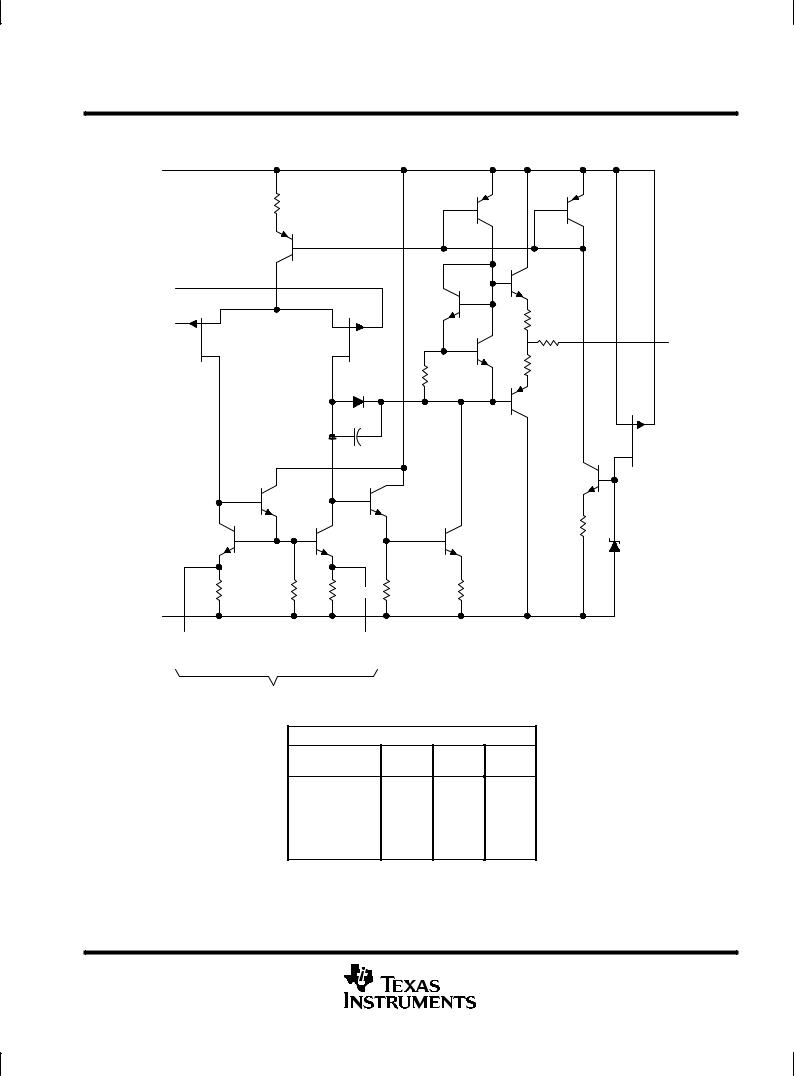

schematic (each amplifier)

VCC +

IN + |

|

|

IN ± |

64 Ω |

Ω |

|

128 |

OUT 64 Ω

OUT 64 Ω

C1

18 pF

1080 Ω |

1080Î Ω |

VCC ± |

|

|

|

|

OFFSET |

|

OFFSET |

|

|

ÁÁÁÁ |

|

NULL |

|

|

NULL |

|

|

|

|

(N1) |

ÁÁÁ(N2) |

|

|

|

|

TL071 Only |

|

|

|

All component values shown are nominal. |

|

|

|

|

|

|

COMPONENT COUNT² |

|

|

|

COMPONENT |

TL072 |

TL074 |

|

|

TYPE |

TL071 |

||

|

|

|

|

|

|

Resistors |

11 |

22 |

44 |

|

Transistors |

14 |

28 |

56 |

|

JFET |

2 |

4 |

6 |

|

Diodes |

1 |

2 |

4 |

|

Capacitors |

1 |

2 |

4 |

|

epi-FET |

1 |

2 |

4 |

² Includes bias and trim circuitry

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

TL071, TL071A, TL071B, TL072

TL072A, TL072B, TL074, TL074A, TL074B

LOW-NOISE JFET-INPUT OPERATIONAL AMPLIFIERS

SLOS080D ± SEPTEMBER 1978 ± REVISED AUGUST 1996

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)²

Supply voltage, VCC + (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . |

. . . . . . . . . . 18 |

V |

Supply voltage, VCC ± (see Note 1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . . . . . . . ±18 V |

|

Differential input voltage, VID (see Note 2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . . . . . . . ± 30 |

V |

Input voltage, VI (see Notes 1 and 3) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . . . . . . . ±15 |

V |

Duration of output short circuit (see Note 4) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . . . . unlimited |

|

Continuous total power dissipation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

See Dissipation Rating Table |

||

Operating free-air temperature range, TA: C suffix . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . 0°C to 70°C |

|

I suffix . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

±40°C to 85°C |

|

M suffix . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . |

±55°C to 125°C |

|

Storage temperature range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . |

±65°C to 150°C |

|

Case temperature for 60 seconds: FK package . . . . . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . |

. . . . . . . 260°C |

|

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: J, JG, or W package . . . . . |

. . . . . . . 300°C |

||

Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: D, N, P, or PW package . . |

. . . . . . . 260°C |

||

²Stresses beyond those listed under ªabsolute maximum ratingsº may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under ªrecommended operating conditionsº is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values, except differential voltages, are with respect to the midpoint between VCC+ and VCC ±.

2.Differential voltages are at IN+ with respect to IN ±.

3.The magnitude of the input voltage must never exceed the magnitude of the supply voltage or 15 V, whichever is less.

4.The output may be shorted to ground or to either supply. Temperature and /or supply voltages must be limited to ensure that the dissipation rating is not exceeded.

DISSIPATION RATING TABLE

PACKAGE |

TA ≤ 25°C |

DERATING |

DERATE |

TA = 70°C |

TA = 85°C |

TA = 125°C |

|

POWER RATING |

FACTOR |

ABOVE TA |

POWER RATING |

POWER RATING |

POWER RATING |

||

|

|||||||

D (8 pin) |

680 mW |

5.8 mW/°C |

33°C |

465 mW |

378 mW |

N/A |

|

D (14 pin) |

680 mW |

7.6 mW/°C |

60°C |

604 mW |

490 mW |

N/A |

|

FK |

680 mW |

11.0 mW/°C |

88°C |

680 mW |

680 mW |

273 mW |

|

J |

680 mW |

11.0 mW/°C |

88°C |

680 mW |

680 mW |

273 mW |

|

JG |

680 mW |

8.4 mW/°C |

69°C |

672 mW |

546 mW |

210 mW |

|

N |

680 mW |

9.2 mW/°C |

76°C |

680 mW |

597 mW |

N/A |

|

P |

680 mW |

8.0 mW/°C |

65°C |

640 mW |

520 mW |

N/A |

|

PW (8 pin) |

525 mW |

4.2 mW/°C |

70°C |

525 mW |

N/A |

N/A |

|

PW (14 pin) |

700 mW |

5.6 mW/°C |

70°C |

700 mW |

N/A |

N/A |

|

W |

680 mW |

8.0 mW/°C |

65°C |

640 mW |

520 mW |

200 mW |

|

|

|

|

|

|

|

|

4 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

electrical characteristics, VCC± = ±15 V (unless otherwise noted)

|

|

|

|

|

|

|

|

|

|

TL071C |

|

|

TL071AC |

|

|

TL071BC |

|

|

TL071I |

|

|

|

|

PARAMETER |

|

TEST CONDITIONS² |

T ³ |

|

TL072C |

|

|

TL072AC |

|

|

TL072BC |

|

|

TL072I |

|

UNIT |

|||

|

|

|

|

TL074C |

|

|

TL074AC |

|

|

TL074BC |

|

|

TL074I |

|

|||||||

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIO |

|

Input offset voltage |

VO = 0, |

RS = 50 Ω |

25°C |

|

3 |

10 |

|

3 |

6 |

|

2 |

3 |

|

3 |

6 |

mV |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

Full range |

|

|

13 |

|

|

7.5 |

|

|

5 |

|

|

8 |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Temperature |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

αVIO |

|

coefficient of input |

VO = 0, |

RS = 50 Ω |

Full range |

|

18 |

|

|

18 |

|

|

18 |

|

|

18 |

|

μV/°C |

||

|

|

|

offset voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IIO |

|

Input offset current |

VO = 0 |

|

25°C |

|

5 |

100 |

|

5 |

100 |

|

5 |

100 |

|

5 |

100 |

pA |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

Full range |

|

|

10 |

|

|

2 |

|

|

2 |

|

|

2 |

nA |

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

Input bias current§ |

V |

O |

= 0 |

|

25°C |

|

65 |

200 |

|

65 |

200 |

|

65 |

200 |

|

65 |

200 |

pA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

IB |

|

|

|

|

|

Full range |

|

|

7 |

|

|

7 |

|

|

7 |

|

|

20 |

nA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

POST |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Common-mode |

|

|

|

|

25°C |

±11 |

±12 |

|

±11 |

±12 |

|

±11 |

±12 |

|

±11 |

±12 |

|

|

|

OFFICE |

VICR |

|

input voltage range |

|

|

|

|

to |

|

to |

|

to |

|

to |

|

V |

|||||

|

|

|

|

|

|

|

|

|

15 |

|

|

15 |

|

|

15 |

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

BOX |

|

|

Maximum peak |

RL = 10 kΩ |

|

25°C |

±12 |

±13.5 |

|

±12 |

±13.5 |

|

±12 |

±13.5 |

|

±12 |

±13.5 |

|

|

||

VOM |

|

output voltage |

RL ≥ 10 kΩ |

|

|

±12 |

|

|

±12 |

|

|

±12 |

|

|

±12 |

|

|

V |

|||

655303 |

|

|

Full range |

|

|

|

|

|

|

|

|

||||||||||

|

|

|

swing |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

• |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Large-signal |

|

|

|

|

25°C |

25 |

200 |

|

50 |

200 |

|

50 |

200 |

|

50 |

200 |

|

|

|

DALLAS, |

AVD |

|

VO = ±10 V, |

RL ≥ 2 kΩ |

|

|

|

|

V/mV |

||||||||||||

|

amplification |

Full range |

15 |

|

|

25 |

|

|

25 |

|

|

25 |

|

|

|||||||

TEXAS |

|

differential voltage |

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

B1 |

|

bandwidth |

|

|

|

|

25°C |

|

3 |

|

|

3 |

|

|

3 |

|

|

3 |

|

MHz |

|

|

|

|

Unity-gain |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

75265 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ri |

|

Input resistance |

|

|

|

|

25°C |

|

1012 |

|

|

1012 |

|

|

1012 |

|

|

1012 |

|

Ω |

|

|

CMRR |

|

Common-mode |

VIC = VICRmin, |

25°C |

70 |

100 |

|

75 |

100 |

|

75 |

100 |

|

75 |

100 |

|

dB |

|||

|

|

rejection ratio |

VO = 0, |

RS = 50 Ω |

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

Supply-voltage |

VCC = ± 9 V to ± 15 V, |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

kSVR |

|

rejection ratio |

25°C |

70 |

100 |

|

80 |

100 |

|

80 |

100 |

|

80 |

100 |

|

dB |

||||

|

|

VO = 0, |

RS = 50 Ω |

|

|

|

|

||||||||||||||

|

|

|

( VCC ± / VIO) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ICC |

|

Supply current |

VO = 0, |

No load |

25°C |

|

1.4 |

2.5 |

|

1.4 |

2.5 |

|

1.4 |

2.5 |

|

1.4 |

2.5 |

mA |

||

|

|

(each amplifier) |

|

|

|

|

|||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VO1/ VO2 |

Crosstalk |

AVD = 100 |

|

25°C |

|

120 |

|

|

120 |

|

|

120 |

|

|

120 |

|

dB |

|||

|

attenuation |

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

² All characteristics are measured under open-loop conditions with zero common-mode voltage unless otherwise specified. ³ Full range is TA = 0°C to 70°C for TL07_C,TL07_AC, TL07_BC and is TA = ± 40°C to 85°C for TL07_I.

§Input bias currents of a FET-input operational amplifier are normal junction reverse currents, which are temperature sensitive as shown in Figure 4. Pulse techniques must be used that maintain the junction temperature as close to the ambient temperature as possible.

5

TL072 TL071B, TL071A, TL071, TL074B TL074A, TL074, TL072B, TL072A, AMPLIFIERS OPERATIONAL INPUT-JFET NOISE-LOW 1996 AUGUST REVISED ± 1978 SEPTEMBER ± SLOS080D

TL071, TL071A, TL071B, TL072

TL072A, TL072B, TL074, TL074A, TL074B

LOW-NOISE JFET-INPUT OPERATIONAL AMPLIFIERS

SLOS080D ± SEPTEMBER 1978 ± REVISED AUGUST 1996

electrical characteristics, VCC ± = ± 15 V (unless otherwise noted)

|

|

|

|

|

|

|

|

|

TL071M |

|

|

TL074M |

|

|

|

|

PARAMETER |

|

TEST CONDITIONS² |

T ³ |

|

TL072M |

|

|

|

UNIT |

|||

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

A |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

MIN |

TYP |

MAX |

MIN |

TYP |

MAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

VIO |

Input offset voltage |

VO = 0, |

RS = 50 Ω |

25°C |

|

3 |

6 |

|

3 |

9 |

mV |

|||

|

|

|

|

|

|

|

||||||||

Full range |

|

|

9 |

|

|

15 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

αVIO |

Temperature coefficient of |

VO = 0, |

RS = 50 Ω |

Full range |

|

18 |

|

|

18 |

|

μV/°C |

|||

input offset voltage |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

IIO |

Input offset current |

VO = 0 |

|

25°C |

|

5 |

100 |

|

5 |

100 |

pA |

|||

|

|

|

|

|

|

|

|

|

||||||

|

Full range |

|

|

20 |

|

|

20 |

nA |

||||||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

I |

|

Input bias current³ |

V |

O |

= 0 |

|

25°C |

|

65 |

200 |

|

65 |

200 |

pA |

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|||||

IB |

|

|

|

|

|

|

|

50 |

|

|

50 |

nA |

||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

Common-mode input |

|

|

|

|

|

|

±12 |

|

|

±12 |

|

|

VICR |

|

|

|

|

25°C |

±11 |

to |

|

±11 |

to |

|

V |

||

voltage range |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

15 |

|

|

15 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

Maximum peak output |

RL = 10 kΩ |

|

25°C |

±12 |

±13.5 |

|

±12 |

±13.5 |

|

|

||

VOM |

RL ≥ 10 kΩ |

|

|

±12 |

|

|

±12 |

|

|

V |

||||

voltage swing |

|

Full range |

|

|

|

|

||||||||

|

|

RL ≥ 2 kΩ |

|

±10 |

|

|

±10 |

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|||||

AVD |

Large-signal differential |

VO = ±10 V, |

RL ≥ 2 kΩ |

25°C |

35 |

200 |

|

35 |

200 |

|

V/mV |

|||

voltage amplification |

|

15 |

|

|

15 |

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|||

B1 |

Unity-gain bandwidth |

TA = 25°C |

|

|

|

3 |

|

|

3 |

|

MHz |

|||

r |

i |

Input resistance |

T |

|

= 25°C |

|

|

|

1012 |

|

|

1012 |

|

Ω |

|

|

A |

|

|

|

|

|

|

|

|

|

|

||

CMRR |

Common-mode rejection |

VIC = VICRmin, |

25°C |

80 |

86 |

|

80 |

86 |

|

dB |

||||

ratio |

VO = 0, |

RS = 50 Ω |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|||||

kSVR |

Supply-voltage rejection |

VCC = ± 9 V to ± 15 V, |

25°C |

80 |

86 |

|

80 |

86 |

|

dB |

||||

ratio ( VCC ± / VIO) |

VO = 0, |

RS = 50 Ω |

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|||||

ICC |

Supply current (each |

VO = 0, |

No load |

25°C |

|

1.4 |

2.5 |

|

1.4 |

2.5 |

mA |

|||

amplifier) |

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

VO1/ VO2 |

Crosstalk attenuation |

AVD = 100 |

|

25°C |

|

120 |

|

|

120 |

|

dB |

|||

²Input bias currents of a FET-input operational amplifier are normal junction reverse currents, which are temperature sensitive as shown in Figure 4. Pulse techniques must be used that will maintain the junction temperature as close to the ambient temperature as possible.

³All characteristics are measured under open-loop conditions with zero common-mode voltage unless otherwise specified. Full range is TA = ± 55°C to 125°C.

6 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

Loading...

Loading...