Texas Instruments TIBPAL22V10AMWB, TIBPAL22V10AMJTB, TIBPAL22V10AMJT, TIBPAL22V10ACNT, TIBPAL22V10AMFKB Datasheet

...

TIBPAL22V10C, TIBPAL22V10AC, TIBPAL22V10AM HIGH-PERFORMANCE IMPACT PROGRAMMABLE ARRAY LOGIC CIRCUITS

|

SRPS024 ± D2943, OCTOBER 1986 ± REVISED MARCH 1992 |

|||||||

• Second-Generation PLD Architecture |

|

C SUFFIX . . . NT PACKAGE |

|

|||||

|

M SUFFIX . . . JT PACKAGE |

|

||||||

• Choice of Operating Speeds |

|

|

||||||

|

|

(TOP VIEW) |

|

|||||

TIBPAL22V10AC . . . 25 ns Max |

|

CLK/I |

|

1 |

|

24 |

VCC |

|

TIBPAL22V10AM . . . 30 ns Max |

|

|

|

|

||||

TIBPAL22V10C . . . 35 ns Max |

|

I |

|

2 |

|

23 |

I/O/Q |

|

• Increased Logic Power ± Up to 22 Inputs |

|

I |

|

3 |

|

22 |

I/O/Q |

|

|

I |

|

4 |

|

21 |

I/O/Q |

|

|

and 10 Outputs |

|

|

|

|

||||

|

I |

|

5 |

|

20 |

I/O/Q |

|

|

• Increased Product Terms ± Average of 12 |

|

|

|

|

||||

|

I |

|

6 |

|

19 |

I/O/Q |

|

|

Per Output |

|

I |

|

7 |

|

18 |

I/O/Q |

|

|

I |

|

8 |

|

17 |

I/O/Q |

|

|

• Variable Product Term Distribution |

|

|

|

|

||||

|

I |

|

9 |

|

16 |

I/O/Q |

|

|

Allows More Complex Functions to Be |

|

|

|

|

||||

|

I |

|

10 |

|

15 |

I/O/Q |

|

|

Implemented |

|

I |

|

11 |

|

14 |

I/O/Q |

|

• Each Output Is User Programmable for |

|

GND |

|

12 |

|

13 |

I |

|

Registered or Combinational Operation, |

|

|

|

|

|

|

|

|

Polarity, and Output Enable Control |

|

C SUFFIX . . . FN PACKAGE |

|

|||||

• TTL-Level Preload for Improved Testability |

|

M SUFFIX . . . FK PACKAGE |

|

|||||

|

|

(TOP VIEW) |

|

|||||

• Extra Terms Provide Logical Synchronous |

|

|

|

|||||

|

I |

I |

CLK/I |

NC |

V |

I/O/Q I/O/Q |

|

|

Set and Asynchronous Reset Capability |

|

|

|

|

|

CC |

|

|

|

|

|

|

|

|

|

|

|

• Fast Programming, High Programming |

|

4 |

3 |

2 |

1 |

28 |

27 26 |

|

Yield, and Unsurpassed Reliability Ensured |

|

|

||||||

I |

5 |

|

|

|

|

25 |

I/O/Q |

|

Using Ti-W Fuses |

I |

6 |

|

|

|

|

24 |

I/O/Q |

• AC and DC Testing Done at the Factory |

I |

7 |

|

|

|

|

23 |

I/O/Q |

NC |

8 |

|

|

|

|

22 |

NC |

|

Utilizing Special Designed-In Test Features |

|

|

|

|

||||

I |

9 |

|

|

|

|

21 |

I/O/Q |

|

• Dependable Texas Instruments Quality and |

|

|

|

|

||||

I |

10 |

|

|

|

|

20 |

I/O/Q |

|

Reliability |

I |

11 |

|

|

|

|

19 |

I/O/Q |

• Package Options Include Both Plastic and |

|

12 13 14 |

15 16 17 18 |

|

||||

|

I |

I |

GND |

NC |

I |

I/O/Q I/O/Q |

|

|

Ceramic Chip Carriers in Addition to Plastic |

|

|

||||||

|

|

|

|

|

|

|

|

|

and Ceramic DIPs |

NC ± No internal connection |

|

||||||

• Functionally Equivalent to AMDs |

|

|||||||

Pin assignments in operating mode |

|

|||||||

AMPAL22V10 and AMPAL22V10A |

|

|

|

|

|

|

|

|

description

The TIBPAL22V10 and TIBPAL22V10A are programmable array logic devices featuring high speed and functional equivalency when compared to presently available devices. They are implemented with the familiar sum-of-products (AND-OR) logic structure featuring the new concept ªProgrammable Output Logic Macrocellº. These IMPACT circuits combine the latest Advanced Low-Power Schottky technology with proven titanium-tungsten fuses to provide reliable, high-performance substitutes for conventional TTL logic.

These devices contain up to 22 inputs and 10 outputs. They incorporate the unique capability of defining and programming the architecture of each output on an individual basis. Outputs may be registered or nonregistered and inverting or noninverting as shown in the output logic macrocell diagram. The ten potential outputs are enabled through the use of individual product terms.

These devices are covered by U.S. Patent 4,410,987.

IMPACT is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright 1992, Texas Instruments Incorporated

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

1 |

TIBPAL22V10C, TIBPAL22V10AC, TIBPAL22V10AM

HIGH-PERFORMANCE IMPACT PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS024 ± D2943, OCTOBER 1986 ± REVISED MARCH 1992

description (continued)

Further advantages can be seen in the introduction of variable product term distribution. This technique allocates from 8 to 16 logical product terms to each output for an average of 12 product terms per output. This variable allocation of terms allows far more complex functions to be implemented than in previously available devices.

Circuit design is enhanced by the addition of a synchronous set and an asynchronous reset product term. These functions are common to all registers. When the synchronous set product term is a logic 1, the output registers are loaded with a logic 1 on the next low-to-high clock transition. When the asynchronous reset product term is a logic 1, the output registers are loaded with a logic 0. The output logic level after set or reset depends on the polarity selected during programming. Output registers can be preloaded to any desired state during testing. Preloading permits full logical verification during product testing.

With features such as programmable output logic macrocells and variable product term distribution, the TIBPAL22V10 and TIBPAL22V10A offer quick design and development of custom LSI functions with complexities of 500 to 800 equivalent gates. Since each of the ten output pins may be individually configured as inputs on either a temporary or permanent basis, functions requiring up to 21 inputs and a single output or down to 12 inputs and 10 outputs are possible.

A power-up clear function is supplied that forces all registered outputs to a predetermined state after power is applied to the device. Registered outputs selected as active-low power up with their outputs high. Registered outputs selected as active-high power up with their outputs low.

A single security fuse is provided on each device to discourage unauthorized copying of fuse patterns. Once blown, the verification circuitry is disabled and all other fuses will appear to be open.

The TIBPAL22V10C and TIBPAL22V10AC are characterized for operation from 0°C to 75°C. The TIBPAL22V10AM is characterized for operation over the full military temperature range of ±55°C to125°C.

2 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

TIBPAL22V10C, TIBPAL22V10AC, TIBPAL22V10AM HIGH-PERFORMANCE IMPACT PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS024 ± D2943, OCTOBER 1986 ± REVISED MARCH 1992

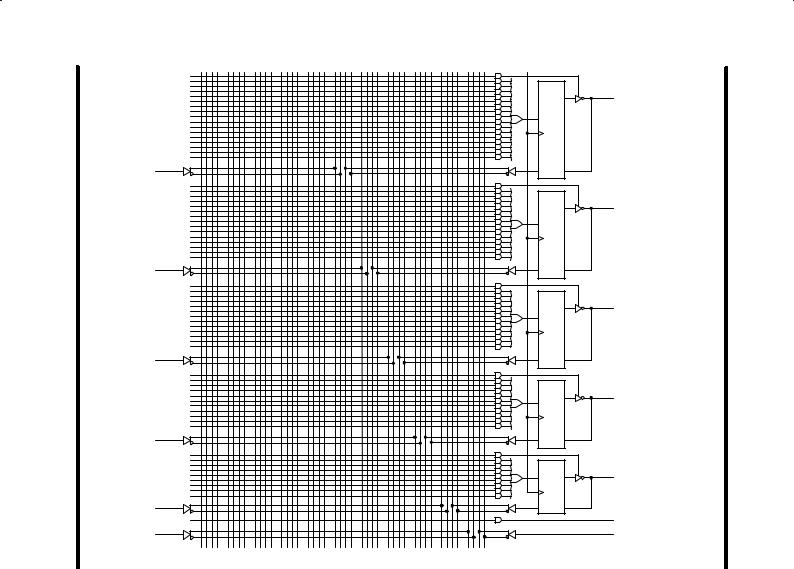

functional block diagram (positive logic)

|

& |

Set |

|

|

|

|

44 x 132 |

Reset |

|

8 |

1 |

|

10 |

|

CLK/I |

22 |

|

12 |

|

|

|

14 |

|

|

16 |

|

|

16 |

|

11 |

22 |

|

I |

14 |

|

10 |

|

|

|

12 |

|

|

10 |

|

|

8 |

|

10

10

C1

1S

R

Output |

I/O/Q |

Logic |

|

Macrocell |

EN |

|

I/O/Q |

|

EN |

|

I/O/Q |

|

EN |

|

I/O/Q |

|

EN |

|

I/O/Q |

|

EN |

|

I/O/Q |

|

EN |

|

I/O/Q |

|

EN |

|

I/O/Q |

|

EN |

|

I/O/Q |

|

EN |

|

I/O/Q |

|

EN |

|

10 |

denotes fused inputs

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

3 |

4

75265 TEXAS DALLAS,• 655303 BOX OFFICE POST

logic symbol (positive logic)

CLK/I |

1 |

|

|

|

|

Increments |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

First |

0 |

4 |

8 |

12 |

16 |

20 |

24 |

28 |

32 |

36 |

40 |

|

0 |

|

|

|

|

|

|

|

|

|

|

Asynchronous Reset |

|

Fuse |

|

|

|

|

|

|

|

|

|

|

(to all registers) |

|

Numbers |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Macro- |

23 |

|

|

|

|

|

|

|

|

|

|

|

cell |

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O/Q |

|

396 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

P = 5808 |

|

|

|

|

|

|

|

|

|

|

|

|

R = 5809 |

|

|

440 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Macro- |

22 |

|

|

|

|

|

|

|

|

|

|

|

cell |

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O/Q |

|

880 |

|

|

|

|

|

|

|

|

|

|

|

I |

2 |

|

|

|

|

|

|

|

|

|

P = 5810 |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

R = 5811 |

|

|

|

924 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Macro- |

21 |

|

|

|

|

|

|

|

|

|

|

|

cell |

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O/Q |

|

1452 |

|

|

|

|

|

|

|

|

|

|

|

I |

3 |

|

|

|

|

|

|

|

|

|

P = 5812 |

|

|

|

|

|

|

|

|

|

|

|

R = 5813 |

|

|

|

1496 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Macro- |

20 |

|

|

|

|

|

|

|

|

|

|

|

cell |

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O/Q |

|

2112 |

|

|

|

|

|

|

|

|

|

|

|

I |

4 |

|

|

|

|

|

|

|

|

|

P = 5814 |

|

|

|

|

|

|

|

|

|

|

|

R = 5815 |

|

|

|

2156 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Macro- |

19 |

|

|

|

|

|

|

|

|

|

|

|

cell |

|

|

|

|

|

|

|

|

|

|

|

|

|

I/O/Q |

|

2860 |

|

|

|

|

|

|

|

|

|

|

|

I |

5 |

|

|

|

|

|

|

|

|

|

P = 5816 |

|

|

|

|

|

|

|

|

|

|

|

R = 5817 |

|

|

D2943, ± SRPS024 |

PERFORMANCE-HIGH |

TIBPAL22V10C, |

1992 MARCH REVISEDOCTOBER± 1986 |

PROGRAMMABLE IMPACT |

TIBPAL22V10AM TIBPAL22V10AC, |

|

CIRCUITS LOGIC ARRAY |

|

75265 TEXAS DALLAS,• 655303 BOX OFFICE POST

5

|

2904 |

|

|

Macro- |

18 |

|

cell |

|

|

|

I/O/Q |

|

3608 |

|

6 |

P = 5818 |

|

I |

|

|

R = 5819 |

|

|

|

3652 |

|

|

Macro- |

17 |

|

cell |

|

|

|

I/O/Q |

7 |

4268 |

|

P = 5820 |

|

|

I |

|

|

R = 5821 |

|

|

|

4312 |

|

|

Macro- |

16 |

|

cell |

|

|

|

I/O/Q |

8 |

4840 |

|

P = 5822 |

|

|

I |

|

|

R = 5823 |

|

|

|

4884 |

|

|

Macro- |

15 |

|

cell |

|

|

|

I/O/Q |

|

5324 |

|

9 |

P = 5824 |

|

I |

|

|

R = 5825 |

|

|

|

5368 |

|

|

Macro- |

14 |

|

cell |

|

|

|

I/O/Q |

10 |

5720 |

|

P = 5826 |

|

|

I |

R = 5827 |

Synchronous Set |

|

5764 |

(to all registers) |

11 |

13 |

I |

I |

Fuse number = First fuse number + Increment

Inside each MACROCELL the ºPº fuse is the polarity fuse and the ºRº fuse is the register fuse.

1992 MARCH REVISED ± 1986 OCTOBER D2943, ± SRPS024 |

TIBPAL22V10AM TIBPAL22V10AC, TIBPAL22V10C, CIRCUITS LOGIC ARRAY PROGRAMMABLE IMPACT PERFORMANCE-HIGH |

TIBPAL22V10C, TIBPAL22V10AC, TIBPAL22V10AM

HIGH-PERFORMANCE IMPACT PROGRAMMABLE ARRAY LOGIC CIRCUITS

SRPS024 ± D2943, OCTOBER 1986 ± REVISED MARCH 1992

output logic macrocell diagram

|

|

Output Logic Macrocell |

|

|

|

|

|

2 |

MUX |

|

|

|

|

|

AR |

R |

I = 0 |

3 |

|

|

1D |

|

0 |

|

|

C1 |

1 |

|

|

SS |

1S |

|

1 |

0 |

|

|

|

0 |

G |

From Clock Buffer |

|

|

3 |

|

|

|

|

|

|

|

|

MUX |

S0 |

|

|

|

|

|

|

|

|

1 |

|

|

|

|

1 |

|

|

|

G1 |

|

|

|

S1

AR = asynchronous reset

SS = synchronous set

6 |

POST OFFICE BOX 655303 •DALLAS, TEXAS 75265 |

Loading...

Loading...