Analog Devices AD7862AN-10, AD7862SQ-10, AD7862BR-3, AD7862BR-10, AD7862ARS-3 Datasheet

...

Simultaneous Sampling

a Dual 250 kSPS 12-Bit ADC

AD7862

FEATURES

Two Fast 12-Bit ADCs

Four Input Channels

Simultaneous Sampling & Conversion 4 ms Throughput Time

Single Supply Operation

Selection of Input Ranges: 610 V for AD7862-10 62.5 V for AD7862-3

0 V to 2.5 V for AD7862-2 High Speed Parallel Interface Low Power, 60 mW typ

Power Saving Mode, 50 mW typ

Overvoltage Protection on Analog Inputs 14-Bit Pin Compatible Upgrade (AD7863)

APPLICATIONS

AC Motor Control

Uninterrupted Power Supplies

Data Acquisition Systems

Communications

GENERAL DESCRIPTION

The AD7862 is a high speed, low power, dual 12-bit A/D converter that operates from a single +5 V supply. The part contains two 4 μs successive approximation ADCs, two track/ hold amplifiers, an internal +2.5 V reference and a high speed parallel interface. There are four analog inputs that are grouped into two channels (A & B) selected by the A0 input. Each channel has two inputs (VA1 & VA2 or VB1 & VB2) that can be sampled and converted simultaneously thus preserving the relative phase information of the signals on both analog inputs. The part accepts an analog input range of ±10 V (AD7862-10),

±2.5 V (AD7862-3) and 0–2.5 V (AD7862-2). Overvoltage protection on the analog inputs for the part allows the input voltage to go to ±17 V, ±7 V or +7 V, respectively, without causing damage.

A single conversion start signal (CONVST) places both track/ holds into hold simultaneously and initiates conversion on both inputs. The BUSY signal indicates the end of conversion, and at this time the conversion results for both channels are available to be read. The first read after a conversion accesses the result from VA1 or VB1, while the second read accesses the result from VA2 or VB2, depending on whether the multiplexer select A0 is low or high, respectively. Data is read from the part via a 12-bit parallel data bus with standard CS and RD signals.

In addition to the traditional dc accuracy specifications such as linearity, full-scale and offset errors, the part is also specified for dynamic performance parameters including harmonic distortion and signal-to-noise ratio.

REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

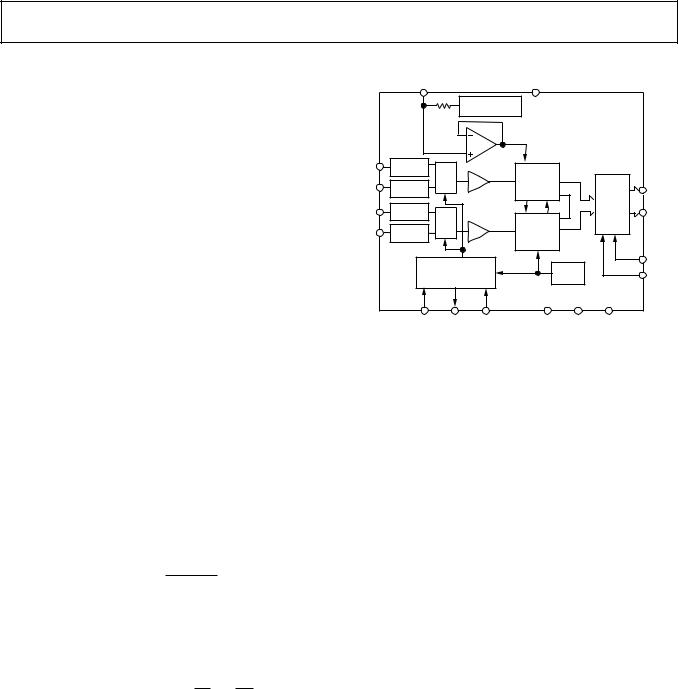

FUNCTIONAL BLOCK DIAGRAM

|

VREF |

|

VDD |

|

|

|

|

|

|

|

+2.5V |

|

|

|

|

|

|

2kΩ |

REFERENCE |

|

|

|

|

|

|

|

|

AD7862 |

|

||

|

|

|

|

|

|

||

VA1 |

SIGNAL |

|

TRACK/ |

|

|

|

|

SCALING |

|

|

|

|

|

||

|

MUX |

HOLD |

12-BIT |

|

|

|

|

|

|

|

|

|

|||

|

SIGNAL |

|

|

|

|

||

VB1 |

|

|

ADC |

|

|

DB0 |

|

SCALING |

|

|

|

|

|||

|

SIGNAL |

|

|

|

|

OUTPUT |

|

VA2 |

|

TRACK/ |

|

|

LATCH |

DB11 |

|

SCALING |

|

|

|

|

|||

|

SIGNAL |

MUX |

HOLD |

12-BIT |

|

|

|

VB2 |

|

|

|

|

|

||

SCALING |

|

|

ADC |

|

|

|

|

|

|

|

|

|

|

|

CS |

|

|

CONVERSION |

CLOCK |

|

RD |

||

|

CONTROL LOGIC |

|

|||||

|

|

|

|

|

|||

|

A0 |

BUSY |

CONVST |

AGND |

AGND |

DGND |

|

The AD7862 is fabricated in Analog Devices’ Linear Compatible CMOS (LC2MOS) process, a mixed technology process that combines precision bipolar circuits with low power CMOS logic. It is available in 28-lead SSOP, SOIC and DIP.

PRODUCT HIGHLIGHTS

1.The AD7862 features two complete ADC functions allowing simultaneous sampling and conversion of two channels. Each

ADC has a 2-channel input mux. The conversion result for both channels is available 3.6 μs after initiating conversion.

2.The AD7862 operates from a single +5 V supply and consumes 60 mW typ. The automatic power-down mode, where the part goes into power down once conversion is complete and “wakes up” before the next conversion cycle, makes the AD7862 ideal for battery-powered or portable applications.

3.The part offers a high speed parallel interface for easy connection to microprocessors, microcontrollers and digital signal processors.

4.The part is offered in three versions with different analog

input ranges. The AD7862-10 offers the standard industrial input range of ±10 V; the AD7862-3 offers the common signal processing input range of ±2.5 V; while the AD7862-2 can be used in unipolar 0 V – +2.5 V applications.

5.The part features very tight aperture delay matching between the two input sample-and-hold amplifiers.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 |

World Wide Web Site: http://www.analog.com |

Fax: 617/326-8703 |

© Analog Devices, Inc., 1996 |

AD7862–SPECIFICATIONS (VDD = +5 V 6 5%, AGND = DGND = 0 V, REF = Internal. All Specifications TMIN to TMAX unless otherwise noted.)

|

A |

B |

S |

|

|

Parameter |

Version1 |

Version |

Version |

Units |

Test Conditions/Comments |

SAMPLE AND HOLD |

|

|

|

|

|

–3 dB Small Signal Bandwidth |

3 |

3 |

3 |

MHz typ |

|

Aperture Delay |

20 |

20 |

20 |

ns typ |

|

Aperture Jitter |

100 |

100 |

100 |

ps typ |

|

Aperture Delay Matching |

200 |

200 |

200 |

ps typ |

|

|

|

|

|

|

|

DYNAMIC PERFORMANCE2 |

|

|

|

|

fIN = 100.0 kHz, fS = 250 kSPS |

Signal to (Noise+Distortion) Ratio3 |

|

|

|

|

|

@ +25°C |

70 |

71 |

70 |

dB min |

|

TMIN to TMAX |

70 |

70 |

70 |

dB min |

|

Total Harmonic Distortion3 |

–78 |

–78 |

–78 |

dB max |

|

Peak Harmonic or Spurious Noise3 |

–85 |

–85 |

–85 |

dB typ |

|

Intermodulation Distortion3 |

|

|

|

|

fa = 49 kHz, fb = 50 kHz |

2nd Order Terms |

–85 |

–85 |

–85 |

dB typ |

|

3rd Order Terms |

–85 |

–85 |

–85 |

dB typ |

|

Channel to Channel Isolation3 |

–80 |

–80 |

–80 |

dB max |

fIN = 100 kHz Sine Wave |

DC ACCURACY |

|

|

|

|

Any Channel |

Resolution |

12 |

12 |

12 |

Bits |

|

Minimum Resolution for which |

|

|

|

|

|

No Missing Codes are Guaranteed |

12 |

12 |

12 |

Bits |

|

Relative Accuracy3 |

±1 |

±1 |

±1 |

LSB max |

Typically 0.4 LSB |

Differential Nonlinearity3 |

±1 |

±1 |

±1 |

LSB max |

|

Positive Gain Error3 |

±4 |

±3 |

±4 |

LSB max |

|

Positive Gain Error Match3 |

4 |

3 |

4 |

LSB max |

|

AD7862-10 |

±4 |

±3 |

±4 |

|

|

Negative Gain Error3 |

LSB max |

|

|||

Bipolar Zero Error |

±4 |

±3 |

±4 |

LSB max |

|

Bipolar Zero Error Match |

4 |

3 |

4 |

LSB max |

|

AD7862-3 |

±4 |

±3 |

±4 |

|

|

Negative Gain Error3 |

LSB max |

|

|||

Bipolar Zero Error |

±4 |

±3 |

±4 |

LSB max |

|

Bipolar Zero Error Match |

4 |

3 |

4 |

LSB max |

|

AD7862-2 |

|

|

|

|

|

Unipolar Offset Error |

+4 |

+3 |

+4 |

LSB max |

|

Unipolar Offset Error Match |

4 |

3.5 |

4 |

LSB max |

|

|

|

|

|

|

|

ANALOG INPUTS |

|

|

|

|

|

AD7862-10 |

±10 |

±10 |

±10 |

|

|

Input Voltage Range |

Volts |

Input |

|||

Input Resistance |

24 |

24 |

24 |

kΩ min |

|

AD7862-3 |

±2.5 |

±2.5 |

±2.5 |

|

|

Input Voltage Range |

Volts |

Input |

|||

Input Resistance |

6 |

6 |

6 |

kΩ min |

|

AD7862-2 |

|

|

|

|

|

Input Voltage Range |

+2.5 |

+2.5 |

+2.5 |

Volts |

Input |

Input Current |

500 |

500 |

500 |

nA max |

|

|

|

|

|

|

|

REFERENCE INPUT/OUTPUT |

|

|

|

|

2.5 V ± 5% |

REF IN Input Voltage Range |

2.375/2.625 |

2.375/2.625 |

2.375/2.625 |

V min/V max |

|

REF IN Input Capacitance4 |

10 |

10 |

10 |

pF max |

|

REF OUT Output Voltage |

2.5 |

2.5 |

2.5 |

V nom |

|

REF OUT Error @ +25°C |

±10 |

±10 |

±10 |

mV max |

|

REF OUT Error TMIN to TMAX |

±25 |

±25 |

±25 |

mV max |

|

REF OUT Temperature Coefficient |

25 |

25 |

25 |

ppm/°C typ |

|

REF OUT Output Impedance |

2 |

2 |

2 |

kΩ nom |

|

LOGIC INPUTS |

|

|

|

|

VDD = 5 V ± 5% |

Input High Voltage, VINH |

2.4 |

2.4 |

2.4 |

V min |

|

Input Low Voltage, VINL |

0.8 |

0.8 |

0.8 |

V max |

VDD = 5 V ± 5% |

Input Current, IIN |

±10 |

±10 |

±10 |

μA max |

|

Input Capacitance, CIN4 |

10 |

10 |

10 |

pF max |

|

–2– |

REV. 0 |

|

|

|

|

|

AD7862 |

|

A |

B |

S |

|

|

Parameter |

Version1 |

Version |

Version |

Units |

Test Conditions/Comments |

LOGIC OUTPUTS |

|

|

|

|

ISOURCE = 200 μA |

Output High Voltage, VOH |

4.0 |

4.0 |

4.0 |

V min |

|

Output Low Voltage, VOL |

0.4 |

0.4 |

0.4 |

V max |

ISINK = 1.6 mA |

DB11–DB0 |

±10 |

±10 |

±10 |

μA max |

|

Floating-State Leakage Current |

|

||||

Floating-State Capacitance4 |

10 |

10 |

10 |

pF max |

|

Output Coding |

|

|

|

|

|

AD7862-10, AD7862-3 |

|

|

|

|

Twos Complement |

AD7863-2 |

|

|

|

|

Straight (Natural) Binary |

|

|

|

|

|

|

CONVERSION RATE |

|

|

|

μs max |

|

Conversion Time |

3.6 |

3.6 |

3.6 |

For Both Channels |

|

Track/Hold Acquisition Time2, 3 |

0.3 |

0.3 |

0.3 |

μs max |

|

POWER REQUIREMENTS |

|

|

|

|

±5% for Specified Performance |

VDD |

+5 |

+5 |

+5 |

V nom |

|

IDD |

|

|

|

|

|

Normal Mode |

15 |

15 |

15 |

mA max |

|

Standby Mode |

25 |

25 |

25 |

μA max |

Logic Inputs = 0 V or VDD |

Power Dissipation |

|

|

|

|

|

Normal Mode |

75 |

75 |

75 |

mW max |

Typically 60 mW |

Standby Mode |

125 |

125 |

125 |

μW max |

Typically 75 μW |

NOTES

1Temperature ranges are as follows: A, B Versions: –40°C to +85°C; S Version: –55°C to +125°C.

2 Performance measured through full channel (multiplexer, SHA and ADC). 3See Terminology.

4Sample tested @ +25°C to ensure compliance.

Specifications subject to change without notice.

ABSOLUTE MAXIMUM RATINGS*

(TA = +25°C unless otherwise noted) |

|

VDD to AGND . . . . . . . . . . . . . . . . . . . . |

. . . . . –0.3 V to +7 V |

VDD to DGND . . . . . . . . . . . . . . . . . . . . |

. . . . . –0.3 V to +7 V |

AGND to DGND . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . ±0.3 V |

Analog Input Voltage to AGND |

±17 V |

AD7862-10 . . . . . . . . . . . . . . . . . . . . |

|

AD7862-3 . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . ±7 V |

AD7862-2 . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . . . . . +7 V |

Reference Input Voltage to AGND . . . |

–0.3 V to VDD + 0.3 V |

Digital Input Voltage to DGND |

. . . . . –0.3 V to VDD + 0.3 V |

|

Digital Output Voltage to DGND |

. . . . –0.3 V to VDD + 0.3 V |

|

Operating Temperature Range |

|

–40°C to +85°C |

Commercial (A, B Version) . . |

. . . . . . . . . |

|

Extended (S Version) . . . . . . . |

. . . . . . . . . |

–55°C to +125°C |

Storage Temperature Range . . . . |

. . . . . . . . |

–65°C to +150°C |

Junction Temperature . . . . . . . . . |

. . . . . . . . |

. . . . . . . +150°C |

Plastic DIP Package, Power Dissipation . . . . |

. . . . . . 670 mW |

|

θJA Thermal Impedance . . . . . . |

. . . . . . . . . |

. . . . . 116°C/W |

Lead Temperature, (Soldering 10 sec) . . . . . . . . . . +260°C Ceramic DIP Package, Power Dissipation . . . . . . . . . 670 mW

θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . 116°C/W Lead Temperature, (Soldering 10 sec) . . . . . . . . . . +260°C

SOIC Package, Power Dissipation . . . . . . . . . . . . . . . 450 mW

θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . 110°C/W Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . +215°C Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . +220°C SSOP Package, Power Dissipation . . . . . . . . . . . . . . . 450 mW

θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . 110°C/W Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . +215°C Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

*Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

ORDERING GUIDE

|

Input |

Relative |

Temperature |

Package |

Package |

Model |

Input |

Accuracy |

Range |

Description |

Option |

|

|

|

|

|

|

AD7862AR-10 |

±10 V |

±1 LSB |

–40°C to +85°C |

28-Bit Small Outline Package |

R-28 |

AD7862BR-10 |

±10 V |

±1 LSB |

–40°C to +85°C |

28-Bit Small Outline Package |

R-28 |

AD7862ARS-10 |

±10 V |

±1 LSB |

–40°C to +85°C |

28-Bit Shrink Small Outline Package |

RS-28 |

AD7862AN-10 |

±10 V |

±1 LSB |

–40°C to +85°C |

28-Bit Plastic DIP |

N-28 |

AD7862SQ-10 |

±10 V |

±1 LSB |

–55°C to +125°C |

28-Bit Cerdip |

Q-28 |

AD7862AR-3 |

±2.5 V |

±1 LSB |

–40°C to +85°C |

28-Bit Small Outline Package |

R-28 |

AD7862BR-3 |

±2.5 V |

±1 LSB |

–40°C to +85°C |

28-Bit Small Outline Package |

R-28 |

AD7862ARS-3 |

±2.5 V |

±1 LSB |

–40°C to +85°C |

28-Bit Shrink Small Outline Package |

RS-28 |

AD7862AN-3 |

±2.5 V |

±1 LSB |

–40°C to +85°C |

28-Plastic DIP |

N-28 |

AD7862AR-2 |

0 V to 2.5 V |

±1 LSB |

–40°C to +85°C |

28-Bit Small Outline Package |

R-28 |

AD7862ARS-2 |

0 V to 2.5 V |

±1 LSB |

–40°C to +85°C |

28-Bit Shrink Small Outline Package |

RS-28 |

REV. 0 |

|

|

–3– |

|

|

AD7862

TIMING CHARACTERISTICS1, 2

(VDD = +5 V 6 5%, AGND = DGND = 0 V, REF = Internal. All Specifications TMIN to TMAX unless otherwise noted.)

|

A, B |

S |

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

Versions |

Version |

Units |

Test Conditions/Comments |

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

tCONV |

3.6 |

3.6 |

μs max |

|

Conversion Time |

||||||||||

tACQ |

0.3 |

0.3 |

us max |

Acquisition Time |

|||||||||||

Parallel Interface |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t1 |

0 |

0 |

ns min |

|

|

CS |

to |

RD |

Setup Time |

||||||

t2 |

0 |

0 |

ns min |

|

CS |

to |

RD |

Hold Time |

|||||||

t3 |

35 |

45 |

ns min |

|

CONVST Pulse Width |

||||||||||

t4 |

35 |

45 |

ns min |

|

|

Read Pulse Width |

|||||||||

t53 |

12 |

12 |

ns min |

|

|

Data Access Time After Falling Edge of |

RD |

|

|

||||||

t64 |

60 |

70 |

ns max |

|

|

|

|

|

|

|

|

|

|

|

|

5 |

5 |

ns min |

|

|

Bus Relinquish Time After Rising Edge of |

RD |

|

||||||||

|

30 |

40 |

ns max |

|

|

|

|

|

|

|

|

|

|

|

|

t7 |

40 |

40 |

ns min |

|

|

Time Between Consecutive Reads |

|||||||||

NOTES

1Sample tested at +25°C to ensure compliance. All input signals are measured with tr = tf = 1 ns (10% to 90% of +5 V) and timed from a voltage level of +1.6 V. 2 See Figure 1.

3Measured with the load circuit of Figure 2 and defined as the time required for an output to cross 0.8 V or 2.0 V.

4These times are derived from the measured time taken by the data outputs to change 0.5 V when loaded with the circuit of Figure 2. The measured number is then extrapolated back to remove the effects of charging or discharging the 50 pF capacitor. This means that the times quoted in the timing characteristics are the true bus relinquish times of the part and as such are independent of external bus loading capacitances.

Specifications subject to change without notice.

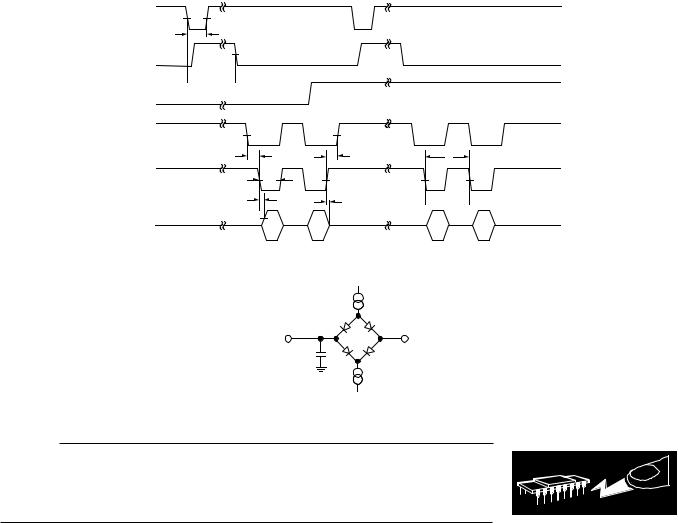

CONVST

t3

BUSY

tCONV

tCONV

A0

CS |

|

......... |

|

......... |

|

|

|

||

t1 |

|

t2 |

|

t7 |

RD |

t4 |

|

|

|

t5 |

|

t |

|

|

|

|

6 |

|

|

DATA |

VA1 |

VA2 |

VB1 |

VB2 |

Figure 1. Timing Diagram

|

1.6mA |

TO |

|

OUTPUT |

+1.6V |

PIN |

50pF |

|

|

|

200µA |

Figure 2. Load Circuit for Access Time and Bus Relinquish Time

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7862 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

–4–

WARNING!

ESD SENSITIVE DEVICE

REV. 0

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7862 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

PIN FUNCTION DESCRIPTION |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Pin |

|

Mnemonic |

Description |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

1 |

|

NC |

No Connect |

|

|

|

|

|

|

|

|

|

|

|

|

|||||

2 |

|

DB11 |

Data Bit 11 (MSB). Three-state TTL output. Output coding is twos complement for the AD7862- |

|||||||||||||||||

|

|

|

|

|

|

|

10 and AD7862-3. Output coding is straight (natural) binary for the AD7862-2. |

|||||||||||||

3–6 |

DB10–DB7 |

Data Bit 10 to Data Bit 7. Three-state TTL outputs. |

||||||||||||||||||

7 |

|

DGND |

Digital Ground. Ground reference for digital circuitry. |

|||||||||||||||||

8 |

|

|

|

|

|

|

Convert Start Input. Logic Input. A high to low transition on this input puts both track/holds into |

|||||||||||||

|

CONVST |

|||||||||||||||||||

|

|

|

|

|

|

|

their hold mode and starts conversion on both channels. |

|||||||||||||

9–15 |

DB6–DB0 |

Data Bit 6 to Data Bit 0. Three-state TTL outputs. |

||||||||||||||||||

16 |

|

|

AGND |

Analog Ground. Ground reference for mux, track/hold, reference and DAC circuitry. |

||||||||||||||||

17 |

|

|

VB2 |

Input Number 2 of Channel B. Analog Input voltage ranges of ±10 V (AD7862-10), ±2.5 V |

||||||||||||||||

|

|

|

|

|

|

|

(AD7862-3) and 0 V–2.5 V (AD7862-2). |

|

|

|

|

|

|

|

|

|

|

|||

18 |

|

|

VA2 |

Input Number 2 of Channel A. Analog Input voltage ranges of ±10 V (AD7862-10), ±2.5 V |

||||||||||||||||

|

|

|

|

|

|

|

(AD7862-3) and 0 V–2.5 V (AD7862-2). |

|

|

|

|

|

|

|

|

|

|

|||

19 |

|

VREF |

Reference Input/Output. This pin is connected to the internal reference through a series resistor and is |

|||||||||||||||||

|

|

|

|

|

|

|

the output reference source for the analog-to-digital converter. The nominal reference voltage is 2.5 V, |

|||||||||||||

|

|

|

|

|

|

|

and this appears at the pin. |

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

|

A0 |

Multiplexer Select. This input is used in conjunction with |

|

and |

|

|

low to enable the data outputs. |

||||||||||||

|

RD |

CS |

||||||||||||||||||

|

|

|

|

|

|

|

With A0 logic low, one read after a conversion will read the data from each of the ADCs in the sequence, |

|||||||||||||

|

|

|

|

|

|

|

VA1, VA2, and a subsequent read, when A0 goes high, reads the data from VB1, VB2. |

|||||||||||||

21 |

|

|

CS |

|

|

Chip Select Input. Active low logic input. The device is selected when this input is active. |

||||||||||||||

22 |

|

|

|

Read Input. Active low logic input. This input is used in conjunction with A0 and |

|

low to enable |

||||||||||||||

|

RD |

CS |

||||||||||||||||||

|

|

|

|

|

|

|

the data outputs. With A0 logic low, one read after a conversion will read the data from each of the |

|||||||||||||

|

|

|

|

|

|

|

ADCs in the sequence, VA1, VA2, and a subsequent read, when A0 goes high, reads the data from VB1, |

|||||||||||||

|

|

|

|

|

|

|

VB2. |

|

|

|

|

|

|

|

|

|

|

|

|

|

23 |

|

BUSY |

Busy Output. The busy output is triggered high by the falling edge of |

CONVST |

and remains high |

|||||||||||||||

|

|

|

|

|

|

|

until conversion is completed. |

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

|

|

VDD |

Analog and Digital Positive Supply Voltage, +5.0 V ± 5%. |

||||||||||||||||

25 |

|

|

VA1 |

Input Number 1 of Channel A. Analog Input voltage ranges of ±10 V (AD7862-10), ±2.5 V |

||||||||||||||||

|

|

|

|

|

|

|

(AD7862-3) and 0 V–2.5 V (AD7862-2). |

|

|

|

|

|

|

|

|

|

|

|||

26 |

|

VB1 |

Input Number 1 of Channel B. Analog Input voltage ranges of ±10 V (AD7862-10), ±2.5 V |

|||||||||||||||||

|

|

|

|

|

|

|

(AD7862-3) and 0 V–2.5 V (AD7862-2). |

|

|

|

|

|

|

|

|

|

|

|||

27 |

|

|

AGND |

Analog Ground. Ground reference for mux, track/hold, reference and DAC circuitry. |

||||||||||||||||

28 |

|

|

NC |

No Connect |

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

PIN CONFIGURATION |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

28 NC |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

NC |

|

1 |

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

DB11 |

|

2 |

|

27 AGND |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

DB10 |

|

3 |

|

26 VB1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

DB9 |

|

4 |

|

25 VA1 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

DB8 |

|

5 |

AD7862 |

24 VDD |

|||||||||

|

|

|

|

|

|

|

DB7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

6 |

TOP VIEW |

23 BUSY |

||||||||||

|

|

|

|

|

|

|

|

|

(Not to Scale) |

|

||||||||||

|

|

|

|

|

|

|

DGND |

|

7 |

22 RD |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

CONVST |

|

8 |

|

21 CS |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

DB6 |

|

9 |

|

20 A0 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

DB5 |

10 |

|

19 |

VREF |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

DB4 |

11 |

|

18 |

VA2 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

DB3 |

12 |

|

17 |

VB2 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

DB2 |

13 |

|

16 AGND |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

DB1 |

14 |

|

15 |

DB0 |

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NC = NO CONNECT |

|

|

|

|

|

|

|

|

|

||

REV. 0 |

–5– |

Loading...

Loading...