Analog Devices AD7303BRM, AD7303BR, AD7303BN Datasheet

a |

+2.7 V to +5.5 V, Serial Input, Dual |

|

Voltage Output 8-Bit DAC |

||

|

|

|

|

|

AD7303 |

|

|

|

FEATURES

Two 8-Bit DACs in One Package

8-Pin DIP/SOIC and microSOIC Packages

+2.7 V to +5.5 V Operation

Internal & External Reference Capability Individual DAC Power-Down Function Three-Wire Serial Interface

QSPI™, SPI™ and Microwire™ Compatible On-Chip Output Buffer

Rail-to-Rail Operation

On-Chip Control Register

Low Power Operation: 2.3 mA @ 3.3 V

Full Power-Down to 1 mA max, typically 80 nA

APPLICATIONS

Portable Battery Powered Instruments

Digital Gain and Offset Adjustment

Programmable Voltage and Current Sources

Programmable Attenuators

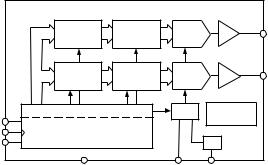

FUNCTIONAL BLOCK DIAGRAM

|

AD7303 |

|

|

|

|

|

INPUT |

DAC |

I DAC A |

I/V |

VOUT A |

|

REGISTER |

REGISTER |

|||

|

INPUT |

DAC |

I DAC B |

I/V |

VOUT B |

|

REGISTER |

REGISTER |

|||

|

|

|

|

||

|

DATA (8) |

CONTROL (8) |

MUX |

POWER ON |

|

DIN |

|

|

|

RESET |

|

|

|

|

|

|

|

SCLK |

16-BIT SHIFT REGISTER |

|

÷2 |

|

|

SYNC |

|

|

|

|

|

|

GND |

|

REF |

VDD |

|

GENERAL DESCRIPTION

The AD7303 is a dual, 8-bit voltage out DAC that operates from a single +2.7 V to +5.5 V supply. Its on-chip precision output buffers allow the DAC outputs to swing rail to rail. This device uses a versatile 3-wire serial interface that operates at clock rates up to 30 MHz, and is compatible with QSPI, SPI, microwire and digital signal processor interface standards. The serial input register is sixteen bits wide; 8 bits act as data bits for the DACs, and the remaining eight bits make up a control register.

The on-chip control register is used to address the relevant DAC, to power down the complete device or an individual DAC, to select internal or external reference and to provide a synchronous loading facility for simultaneous update of the DAC outputs with a software LDAC function.

The low power consumption of this part makes it ideally suited to portable battery operated equipment. The power consumption is 7.5 mW max at 3 V, reducing to less than 3 μW in full power-down mode.

The AD7303 is available in an 8-pin plastic dual in-line package, 8-lead SOIC and microSOIC packages.

QSPI and SPI are trademarks of Motorola.

Microwire is a trademark of National Semiconductor.

REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

PRODUCT HIGHLIGHTS

1.Low power, single supply operation. This part operates from a single +2.7 V to +5.5 V supply and consumes typically 15 mW at 5.5 V, making it ideal for battery powered applications.

2.The on-chip output buffer amplifiers allow the outputs of the DACs to swing rail to rail with a settling time of typically 1.2 μs.

3.Internal or external reference capability.

4.High speed serial interface with clock rates up to 30 MHz.

5.Individual power-down of each DAC provided. When completely powered down, the DAC consumes typically 80 nA.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 |

World Wide Web Site: http://www.analog.com |

Fax: 617/326-8703 |

© Analog Devices, Inc., 1997 |

|

(VDD = +2.7 V to +5.5 V, Internal Reference; RL = 10 kV to VDD and GND; CL = 100 pF |

||

AD7303–SPECIFICATIONS to GND; all specifications TMIN to TMAX unless otherwise noted) |

|||

Parameter |

B Versions1 |

Units |

Conditions/Comments |

STATIC PERFORMANCE |

|

|

|

Resolution |

8 |

Bits |

|

Relative Accuracy |

±1 |

LSB max |

Note 2 |

Differential Nonlinearity |

±1 |

LSB max |

Guaranteed Monotonic |

Zero-Code Error @ +25°C |

3 |

LSB max |

All Zeros Loaded to DAC Register |

Full-Scale Error |

–0.5 |

LSB typ |

All Ones Loaded to DAC Register |

Gain Error3 |

+1 |

% FSR typ |

|

Zero-Code Temperature Coefficient |

100 |

μV/°C typ |

|

DAC REFERENCE INPUT |

|

|

|

REFIN Input Range |

1 to VDD/2 |

V min to max |

|

REFIN Input Impedance |

10 |

ΜΩ typ |

|

Internal Voltage Reference Error 4 |

±1 |

% max |

|

OUTPUT CHARACTERISTICS |

|

|

|

Output Voltage Range |

0 to VDD |

V min to max |

Typically 1.2 μs |

Output Voltage Settling Time |

2 |

μs max |

|

Slew Rate |

7.5 |

V/μs typ |

|

Digital to Analog Glitch Impulse |

0.5 |

nV-s typ |

1 LSB Change Around Major Carry |

Digital Feedthrough |

0.2 |

nV-s typ |

|

Digital Crosstalk |

0.2 |

nV-s typ |

|

Analog Crosstalk |

±0.2 |

LSB typ |

|

DC Output Impedance |

40 |

Ω typ |

|

Short Circuit Current |

14 |

mA typ |

VDD = ±10% |

Power Supply Rejection Ratio |

0.0001 |

%/% max |

|

LOGIC INPUTS |

±10 |

μA max |

|

Input Current |

|

||

VINL, Input Low Voltage |

0.8 |

V max |

VDD = +5 V |

VINH, Input High Voltage |

0.6 |

V max |

VDD = +3 V |

2.4 |

V min |

VDD = +5 V |

|

|

2.1 |

V min |

VDD = +3 V |

Pin Capacitance |

5 |

pF max |

|

|

|

|

|

POWER REQUIREMENTS |

|

|

|

VDD |

2.7/5.5 |

V min/max |

|

IDD (Normal Mode) |

|

|

Both DACs Active and Excluding Load Currents, |

VDD = 3.3 V |

|

|

VIH = VDD, VIL = GND |

@ +25°C |

2.1 |

mA max |

See Figure 8 |

TMIN – TMAX |

2.3 |

mA max |

|

VDD = 5.5 V |

|

|

|

@ +25°C |

2.7 |

mA max |

|

TMIN – TMAX |

3.5 |

mA max |

|

IDD (Full Power-Down) |

|

|

|

@ +25°C |

80 |

nA typ |

VIH = VDD, VIL = GND |

TMIN – TMAX |

1 |

μA max |

See Figure 19 |

NOTES

1Temperature ranges are as follows: B Version, –40°C to +105°C.

2Relative Accuracy is calculated using a reduced digital code range of 15 to 245.

3Gain Error is specified between Codes 15 and 245. The actual error at Code 15 is typically 3 LSB.

4Internal Voltage Reference Error = (Actual VREF – Ideal VREF/Ideal VREF) • 100. Ideal VREF = VDD/2, actual VREF = voltage on reference pin when internal reference is selected.

Specifications subject to change without notice.

ORDERING GUIDE

|

Temperature |

Package |

Model |

Range |

Options* |

|

|

|

AD7303BN |

–40°C to +105°C |

N-8 |

AD7303BR |

–40°C to +105°C |

SO-8 |

AD7303BRM |

–40°C to +105°C |

RM-8 |

*N = Plastic DIP; R = SOIC; RM = microSOIC.

–2– |

REV. 0 |

|

|

|

|

|

AD7303 |

|

|

|

|

|

|

|

|

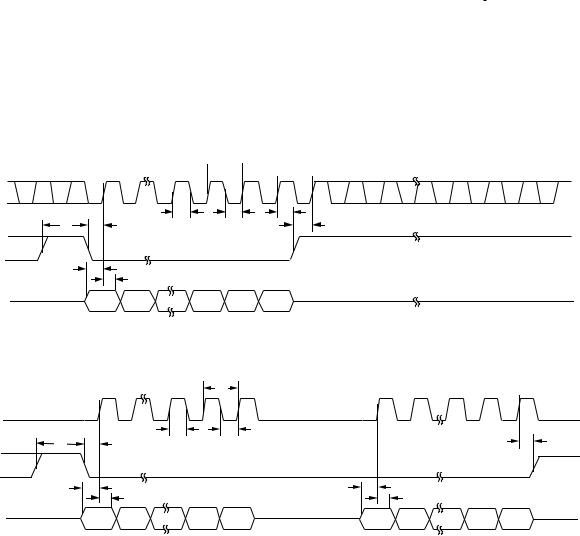

TIMING CHARACTERISTICS1, 2 |

(VDD = +2.7 V to +5.5 V; GND = 0 V; Reference = Internal VDD/2 Reference; all specifications |

|||||

TMIN to TMAX unless otherwise noted) |

|

|

|

|||

Parameter |

Limit at TMIN, TMAX (B Version) |

Units |

Conditions/Comments |

|||

|

|

|

|

|

|

|

t1 |

33 |

|

ns min |

SCLK Cycle Time |

||

t2 |

13 |

|

ns min |

SCLK High Time |

||

t3 |

13 |

|

ns min |

SCLK Low Time |

||

t4 |

5 |

|

ns min |

SYNC Setup Time |

||

t5 |

5 |

|

ns min |

Data Setup Time |

||

t6 |

4.5 |

|

ns min |

Data Hold Time |

||

t7 |

4.5 |

|

ns min |

SYNC Hold Time |

||

t8 |

33 |

|

ns min |

Minimum |

SYNC |

High Time |

NOTES

1Sample tested at +25°C to ensure compliance. All input signals are specified with tr = tf = 5 ns (10% to 90% of V DD) and timed from a voltage level of (VIL + VIH)/2, tr and tf should not exceed 1 μs on any input.

2See Figures 1 and 2.

t1

t1

SCLK (I) |

|

|

|

|

t2 |

t3 |

t7 |

t8 |

t4 |

|

t4 |

SYNC (I) |

|

|

|

|

t5 |

|

|

|

t6 |

|

|

DIN (I) |

DB15 |

|

DB0 |

Figure 1. Timing Diagram for Continuous 16-Bit Write

|

|

t1 |

|

|

SCLK (I) |

|

|

|

|

|

t2 |

t3 |

|

|

t8 |

t4 |

|

|

t7 |

SYNC (I) |

|

|

|

|

|

t5 |

|

t5 |

|

|

t6 |

|

t6 |

|

DIN (I) |

DB15 |

DB8 |

DB7 |

DB0 |

Figure 2. Timing Diagram for 2 × 8-Bit Writes

REV. 0 |

–3– |

AD7303

ABSOLUTE MAXIMUM RATINGS*

(TA = +25°C unless otherwise noted)

VDD to GND . . . . . . . . . . . . . . . . . . . . . |

. . . . . –0.3 V to +7 V |

Reference Input Voltage to GND . . . . |

–0.3 V to VDD + 0.3 V |

Digital Input Voltage to GND . . . . . . . |

–0.3 V to VDD + 0.3 V |

VOUT A, VOUT B to GND . . . . . . . . . . . |

–0.3 V to VDD + 0.3 V |

Operating Temperature Range |

–40°C to +105°C |

Commercial (B Version) . . . . . . . . . . |

|

Storage Temperature Range . . . . . . . . . |

. . . –65°C to +150°C |

Junction Temperature . . . . . . . . . . . . . . |

. . . . . . . . . . . +150°C |

Plastic DIP Package, Power Dissipation |

. . . . . . . . . . 800 mW |

θJA Thermal Impedance . . . . . . . . . . . . |

. . . . . . . . . 117°C/W |

Lead Temperature (Soldering, 10 sec) . |

. . . . . . . . . . +260°C |

SOIC Package, Power Dissipation . . . . . . . . . . . . . . . 450 mW

θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 157°C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

MicroSOIC Package, Power Dissipation . . . . . . . . . . 450 mW

θJA Thermal Impedance . . . . . . . . . . . . . . . . . . . . . 206°C/W

Lead Temperature, Soldering

Vapor Phase (60 sec) . . . . . . . . . . . . . . . . . . . . . . +215°C

Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . . +220°C

*Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7303 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

PIN CONFIGURATIONS (DIP, SOIC and microSOIC)

WARNING!

ESD SENSITIVE DEVICE

|

|

|

|

|

|

VOUT B |

|

VOUT A |

1 |

|

|

|

8 |

||

|

|

AD7303 |

|

|

|||

VDD |

2 |

7 |

SYNC |

||||

|

|

TOP VIEW |

|

|

|||

GND |

3 |

6 |

DIN |

||||

(Not to Scale) |

|||||||

|

|

|

|

||||

REF |

4 |

|

|

|

5 |

SCLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

PIN FUNCTION DESCRIPTIONS |

||

|

|

|

|

|

|

|

|

|

Pin |

|

|

|

|

|

|

|

|

No. |

|

Mnemonic |

|

Function |

||||

|

|

|

|

|

|

|

|

|

1 |

|

VOUT A |

|

Analog Output Voltage from DAC A. The output amplifier swings rail to rail on its output. |

||||

2 |

|

VDD |

|

Power Supply Input. These parts can be operated from +2.7 V to +5.5 V and should be decoupled to GND. |

||||

3 |

|

GND |

Ground reference point for all circuitry on the part. |

|||||

4 |

|

REF |

External Reference Input. This can be used as the reference for both DACs, and is selected by setting the |

|||||

|

|

|

|

|

INT |

/EXT bit in the control register to a logic one. The range on this reference input is 1 V to VDD/2. When |

||

|

|

|

|

|

the internal reference is selected, this voltage will appear as an output for decoupling purposes at the REF Pin. |

|||

|

|

|

|

|

When using the internal reference, external voltages should not be connected to the REF Pin, see Figure 21. |

|||

5 |

SCLK |

Serial Clock. Logic Input. Data is clocked into the input shift register on the rising edge of the serial clock |

||||||

|

|

|

|

|

input. Data can be transferred at rates up to 30 MHz. |

|||

6 |

DIN |

Serial Data Input. This device has a 16-bit shift register, 8 bits for data and 8 bits for control. Data is clocked |

||||||

|

|

|

|

|

into the register on the rising edge of the clock input. |

|||

7 |

|

|

|

|

Level Triggered Control Input (active low). This is the frame synchronization signal for the input data. When |

|||

|

SYNC |

|

||||||

|

|

|

|

|

SYNC goes low, it enables the input shift register and data is transferred in on the rising edges of the following |

|||

|

|

|

|

|

clocks. The rising edge of the |

SYNC |

causes the relevant registers to be updated. |

|

8 |

|

VOUT B |

|

Analog output voltage from DAC B. The output amplifier swings rail to rail on its output. |

||||

–4– |

REV. 0 |

AD7303

TERMINOLOGY

INTEGRAL NONLINEARITY

For the DACs, relative accuracy or endpoint nonlinearity is a measure of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function. A graphical representation of the transfer curve is shown in Figure 15.

DIFFERENTIAL NONLINEARITY

Differential nonlinearity is the difference between the measured change and the ideal 1 LSB change of any two adjacent codes. A specified differential nonlinearity of ±1 LSB maximum ensures monotonicity.

ZERO CODE ERROR

Zero code error is the measured output voltage from VOUT of either DAC when zero code (all zeros) is loaded to the DAC latch. It is due to a combination of the offset errors in the DAC and output amplifier. Zero-scale error is expressed in LSBs.

GAIN ERROR

This is a measure of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from ideal expressed as a percent of the full-scale value. Gain error is calculated between Codes 15 and 245.

FULL-SCALE ERROR

Full-Scale Error is a measure of the output error when the DAC latch is loaded with FF Hex. Full-scale error includes the offset error.

DIGITAL-TO-ANALOG GLITCH IMPULSE

Digital-to-analog glitch impulse is the impulse injected into the analog output when the digital inputs change state with the DAC selected and the software LDAC used to update the DAC. It is normally specified as the area of the glitch in nV-s and is measured when the digital input code is changed by 1 LSB at the major carry transition.

DIGITAL FEEDTHROUGH

Digital feedthrough is a measure of the impulse injected into the analog output of a DAC from the digital inputs of the same DAC, but is measured when the DAC is not updated. It is specified in nV-s and measured with a full-scale code change on the data bus, i.e., from all 0s to all 1s and vice versa.

DIGITAL CROSSTALK

Digital crosstalk is the glitch impulse transferred to the output of one converter due to a digital code change to another DAC. It is specified in nV-s.

ANALOG CROSSTALK

Analog crosstalk is a change in output of any DAC in response to a change in the output of the other DAC. It is measured in LSBs.

POWER SUPPLY REJECTION RATIO (PSRR)

This specification indicates how the output of the DAC is affected by changes in the power supply voltage. Power supply rejection ratio is quoted in terms of % change in output per % of change in VDD for full-scale output of the DAC. VDD is varied

± 10%. This specification applies to an external reference only because the output voltage will track the VDD voltage when internal reference is selected.

REV. 0 |

–5– |

Loading...

Loading...