Analog Devices AD7245ATQ, AD7245ATE, AD7245ABR, AD7245ABN, AD7245AAR Datasheet

...

a |

LC2MOS |

|

12-Bit DACPORTs |

||

|

|

|

|

|

AD7245A/AD7248A |

|

|

|

FEATURES

12-Bit CMOS DAC with Output Amplifier and Reference

Improved AD7245/AD7248: 12 V to 15 V Operation1/2 LSB Linearity Grade

Faster Interface—30 ns Typ Data Setup Time Extended Plastic Temperature Range (–40 C to +85 C)

Single or Dual Supply Operation

Low Power—65 mW Typ in Single Supply Parallel Loading Structure: AD7245A (8+4) Loading Structure: AD7248A

GENERAL DESCRIPTION

The AD7245A/AD7248A is an enhanced version of the industry standard AD7245/AD7248. Improvements include operation from 12 V to 15 V supplies, a ± 1/2 LSB linearity grade, faster interface times and better full scale and reference variations with VDD. Additional features include extended temperature range operation for commercial and industrial grades.

The AD7245A/AD7248A is a complete, 12-bit, voltage output, digital-to-analog converter with output amplifier and Zener voltage reference on a monolithic CMOS chip. No external user trims are required to achieve full specified performance.

Both parts are microprocessor compatible, with high speed data latches and double-buffered interface logic. The AD7245A accepts 12-bit parallel data that is loaded into the input latch on the rising edge of CS or WR. The AD7248A has an 8-bit-wide data bus with data loaded to the input latch in two write operations. For both parts, an asynchronous LDAC signal transfers data from the input latch to the DAC latch and updates the analog output. The AD7245A also has a CLR signal on the DAC latch which allows features such as power-on reset to be implemented.

The on-chip 5 V buried Zener diode provides a low noise, temperature compensated reference for the DAC. For single supply operation, two output ranges of 0 V to 5 V and 0 V to 10 V are available, while these two ranges plus an additional ±5 V range are available with dual supplies. The output amplifiers are capable of developing 10 V across a 2 kΩ load to GND.

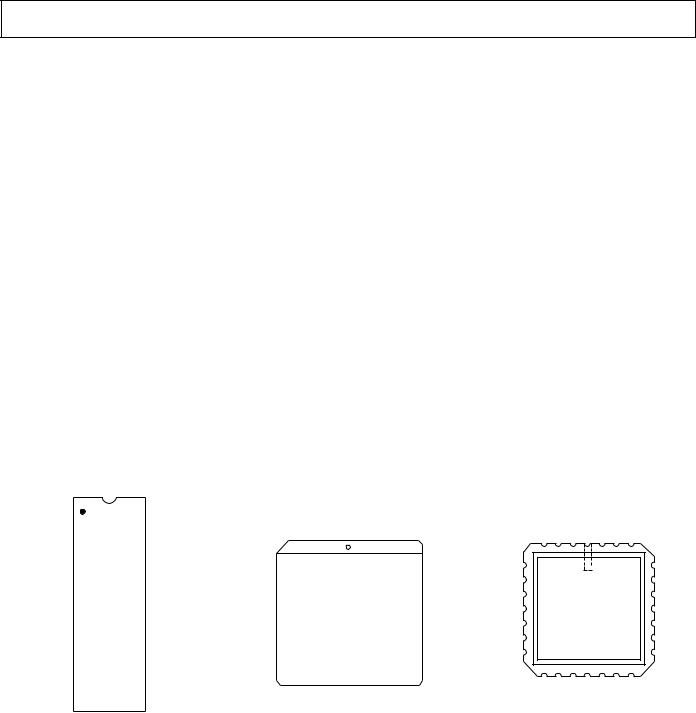

The AD7245A/AD7248A is fabricated in linear compatible CMOS (LC2MOS), an advanced, mixed technology process that combines precision bipolar circuits with low power CMOS logic. The AD7245A is available in a small, 0.3" wide, 24-lead DIP and SOIC and in 28-terminal surface mount packages. The AD7248A is packaged in a small, 0.3" wide, 20-lead DIP and SOIC and in 20-terminal surface mount packages.

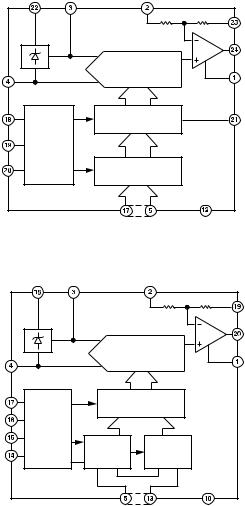

AD7245A FUNCTIONAL BLOCK DIAGRAM

|

VDD |

REF OUT |

ROFS |

|

|

|

|

2R |

2R |

|

|

|

|

RFB |

|

|

|

|

VOUT |

|

|

VREF |

DAC |

|

|

|

|

VSS |

|

AGND |

|

|

|

|

CS |

|

|

DAC LATCH |

CLR |

WR |

CONTROL |

|

AD7245A |

|

LOGIC |

|

|||

LDAC |

|

|

INPUT LATCH |

|

|

|

|

DB0 DB11 |

DGND |

AD7248A FUNCTIONAL BLOCK DIAGRAM

VDD REF OUT |

ROFS |

|

|

|

2R |

2R |

|

|

|

|

RFB |

|

|

|

|

VOUT |

|

VREF |

DAC |

|

|

|

|

VSS |

||

AGND |

|

|

|

|

LDAC |

|

DAC LATCH |

|

|

WR |

CONTROL |

|

|

AD7248A |

|

|

|

||

CSLSB |

LOGIC |

|

|

|

|

4-BIT |

8-BIT |

|

|

|

|

|

||

CSMSB |

|

INPUT |

INPUT |

|

|

LATCH |

LATCH |

|

|

|

|

|

||

|

|

DB7 |

DB0 |

DGND |

PRODUCT HIGHLIGHTS

1.The AD7245A/AD7248A is a 12-bit DACPORT® on a single chip. This single chip design and small package size offer considerable space saving and increased reliability over multichip designs.

2.The improved interface times on the part allows easy, direct interfacing to most modern microprocessors.

3.The AD7245A/AD7248A features a wide power supply range allowing operation from 12 V supplies.

DACPORT is a registered trademark of Analog Devices, Inc.

REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 |

World Wide Web Site: http://www.analog.com |

Fax: 781/326-8703 |

© Analog Devices, Inc., 2001 |

AD7245A/AD7248A–SPECIFICATIONS (VDD = +12 V to +15 V,1 VSS = O V or –12 V to –15 V,1 AGND = DGND = O V, RL = 2 k , CL = 100 pF. All specifications TMIN to TMAX unless otherwise noted.)

|

A2 |

B2 |

T2 |

|

|

Parameter |

Version |

Version |

Version |

Unit |

Test Conditions/Comments |

|

|

|

|

|

|

STATIC PERFORMANCE |

|

|

|

|

|

Resolution |

12 |

12 |

12 |

Bits |

|

Relative Accuracy @ 25°C3 |

± 3/4 |

± 1/2 |

± 1/2 |

LSB max |

|

TMIN to TMAX |

± 1 |

± 3/4 |

± 3/4 |

LSB max |

|

TMIN to TMAX |

± 1 |

± 1/2 |

± 1 |

LSB max |

VDD = 15 V ± 10% |

Differential Nonlinearity3 |

± 1 |

LSB max |

Guaranteed Monotonic |

||

Unipolar Offset Error @ 25°C3 |

± 3 |

± 3 |

± 3 |

LSB max |

VSS = 0 V or –12 V to –15 V4 |

TMIN to TMAX |

± 5 |

± 5 |

± 5 |

LSB max |

Typical Tempco is ± 3 ppm of FSR5/°C. |

Bipolar Zero Error @ 25°C3 |

± 3 |

± 2 |

± 2 |

LSB max |

ROFS connected to REF OUT; VSS = –12 V to –15 V4 |

TMIN to TMAX |

± 5 |

± 4 |

± 4 |

LSB max |

Typical Tempco is ± 3 ppm of FSR5/°C. |

DAC Gain Error3, 6 |

± 2 |

± 2 |

± 2 |

LSB max |

|

Full-Scale Output Voltage Error7 @ 25°C |

± 0.2 |

± 0.2 |

± 0.2 |

% of FSR max |

VDD = 15 V |

∆Full Scale/∆VDD |

± 0.06 |

± 0.06 |

± 0.06 |

% of FSR/V max |

VDD = +12 V to +15 V4 |

∆Full Scale/∆VSS |

± 0.01 |

± 0.01 |

± 0.01 |

% of FSR/V max |

VSS = –12 V to –15 V4 |

Full-Scale Temperature Coefficient8 |

± 40 |

± 30 |

± 40 |

ppm of FSR/°C max |

VDD = 15 V |

REFERENCE OUTPUT |

|

|

|

|

|

REF OUT @ 25°C |

4.99/5.01 |

4.99/5.01 |

4.99/5.01 |

V min/V max |

VDD = 15 V |

∆REF OUT/∆VDD |

2 |

2 |

2 |

mV/V max |

VDD = 12 V to 15 V4 |

Reference Temperature Coefficient |

± 25 |

± 25 |

± 35 |

ppm/°C typ |

|

Reference Load Change |

|

|

|

|

|

(∆REF OUT vs. ∆I) |

–1 |

–1 |

–1 |

mV max |

Reference Load Current Change (0–100 µA) |

|

|

|

|

|

|

DIGITAL INPUTS |

|

|

|

|

|

Input High Voltage, VINH |

2.4 |

2.4 |

2.4 |

V min |

|

Input Low Voltage, VINL |

0.8 |

0.8 |

0.8 |

V max |

|

Input Current, IIN |

± 10 |

± 10 |

± 10 |

µA max |

VIN = 0 V to VDD |

Input Capacitance9 |

8 |

8 |

8 |

pF max |

|

ANALOG OUTPUTS |

|

|

|

kΩ min/kΩ max |

|

Output Range Resistors |

15/30 |

15/30 |

15/30 |

|

|

Output Voltage Ranges10 |

5, 10 |

5, 10 |

5, 10 |

V |

VSS = 0 V; Pin Strappable |

|

5, 10, |

5, 10, |

5, 10, |

|

VSS = –12 V to –15 V;4 Pin Strappable |

|

± 5 |

± 5 |

± 5 |

V |

|

DC Output Impedance |

0.5 |

0.5 |

0.5 |

Ω typ |

|

|

|

|

|

|

|

AC CHARACTERISTICS9 |

|

|

|

|

Settling Time to Within ± 1/2 LSB of Final Value |

Voltage Output Settling Time |

|

|

|

µs max |

|

Positive Full-Scale Change |

7 |

7 |

10 |

DAC Latch All 0s to All 1s |

|

Negative Full-Scale Change |

7 |

7 |

10 |

µs max |

DAC Latch All 1s to All 0s; VSS = –12 V to –15 V4 |

Output Voltage Slew Rate |

2 |

2 |

1.5 |

V/µs min |

|

Digital Feedthrough3 |

10 |

10 |

10 |

nV-s typ |

|

Digital-to-Analog Glitch Impulse |

30 |

30 |

30 |

nV-s typ |

|

|

|

|

|

|

|

POWER REQUIREMENTS |

|

|

|

|

|

VDD |

+10.8/ |

+10.8/ |

+10.8/ |

V min/ |

For Specified Performance Unless Otherwise Stated |

|

+16.5 |

+16.5 |

+16.5 |

V max |

|

VSS |

–10.8/ |

–10.8/ |

–10.8/ |

V min/ |

For Specified Performance Unless Otherwise Stated |

IDD @ 25°C |

–16.5 |

–16.5 |

–16.5 |

V max |

|

9 |

9 |

9 |

mA max |

Output Unloaded; Typically 5 mA |

|

TMlN to TMAX |

10 |

10 |

12 |

mA max |

Output Unloaded |

ISS (Dual Supplies) |

3 |

3 |

5 |

mA max |

Output Unloaded; Typically 2 mA |

NOTES

1Power supply tolerance is ±10%.

2Temperature ranges are as follows: A/B Versions; –40°C to +85°C; T Version; –55°C to +125°C. 3See Terminology.

4With appropriate power supply tolerances.

5FSR means Full-Scale Range and is 5 V for the 0 V to 5 V output range and 10 V for both the 0 V to 10 V and ± 5 V output ranges. 6This error is calculated with respect to the reference voltage and is measured after the offset error has been allowed for.

7This error is calculated with respect to an ideal 4.9988 V on the 0 V to 5 V and ±5 V ranges; it is calculated with respect to an ideal 9.9976 V on the 0 V to 10 V range. It includes the effects of internal voltage reference, gain and offset errors.

8Full-Scale TC = ∆FS/∆T, where ∆FS is the full-scale change from TA = 25°C to TMIN or TMAX. 9Guaranteed by design and characterization, not production tested.

100 V to 10 V output range is available only when VDD ≥ +14.25 V.

Specifications subject to change without notice.

–2– |

REV. B |

AD7245A/AD7248A

SWITCHING CHARACTERISTICS1 (VDD = +12 V to +15 V;2 VSS = 0 V to –12 V to –15 V;2 See Figures 5 and 7.)

Parameter |

A, B Versions |

T Version |

Unit |

Conditions |

|

|

|

|

|

t1 |

|

|

|

|

@ 25°C |

55 |

55 |

ns typ |

Chip Select Pulsewidth |

TMIN to TMAX |

80 |

100 |

ns min |

|

t2 |

|

|

|

|

@ 25°C |

40 |

40 |

ns typ |

Write Pulsewidth |

TMIN to TMAX |

80 |

100 |

ns min |

|

t3 |

|

|

|

|

@ 25°C |

0 |

0 |

ns min |

Chip Select to Write Setup Time |

TMIN to TMAX |

0 |

0 |

ns min |

|

t4 |

|

|

|

|

@ 25°C |

0 |

0 |

ns min |

Chip Select to Write Hold Time |

TMIN to TMAX |

0 |

0 |

ns min |

|

t5 |

|

|

|

|

@ 25°C |

40 |

40 |

ns typ |

Data Valid to Write Setup Time |

TMIN to TMAX |

80 |

80 |

ns min |

|

t6 |

|

|

|

|

@ 25°C |

10 |

10 |

ns min |

Data Valid to Write Hold Time |

TMIN to TMAX |

10 |

10 |

ns min |

|

t7 |

|

|

|

|

@ 25°C |

40 |

40 |

ns typ |

Load DAC Pulsewidth |

TMIN to TMAX |

80 |

100 |

ns min |

|

t8 (AD7245A Only) |

|

|

|

|

@ 25°C |

40 |

40 |

ns typ |

Clear Pulsewidth |

TMIN to TMAX |

80 |

100 |

ns min |

|

NOTES

1Sample tested at 25°C to ensure compliance. 2Power supply tolerance is ±10%.

ABSOLUTE MAXIMUM RATINGS1 |

|

|

VDD to AGND . . . . . . . . . . . . . . . . . . . . . |

. . . –0.3 V to +17 V |

|

VDD to DGND . . . . . . . . . . . . . . . . . . . . . . |

. . –0.3 V to +17 V |

|

VDD to VSS . . . . . . . . . . . . . . . . . . . . . . . . . |

. . –0.3 V to +34 |

V |

AGND to DGND . . . . . . . . . . . . . . . . . . . |

. . . . . –0.3 V, VDD |

|

Digital Input Voltage to DGND . . . . . . . |

–0.3 V, VDD + 0.3 |

V |

VOUT to AGND2 . . . . . . . . . . . . . . . . . . . . |

. . . . . . . . VSS, VDD |

|

VOUT to VSS2 . . . . . . . . . . . . . . . . . . . . . . . |

. . . . . . . 0 V, 24 |

V |

2 |

–32 V, 0 |

V |

VOUT to VDD . . . . . . . . . . . . . . . . . . . . . . . |

||

REF OUT2 to AGND . . . . . . . . . . . . . . . . |

. . . . . . . . 0 V, VDD |

|

Power Dissipation (Any Package) to 75°C . |

. . . . . . . . 450 mW |

|

Derates above 75°C by . . . . . . . . . . . . . |

. . . . . . . 6 mW/°C |

|

Operating Temperature

Commercial (A, B Versions) . . . . . . . . . . . –40°C to +85°C Extended (S Version) . . . . . . . . . . . . . . . –55°C to +125°C Storage Temperature . . . . . . . . . . . . . . . . . . –65°C to +150°C Lead Temperature (Soldering, 10 secs) . . . . . . . . . . . . . 300°C

NOTES

1Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2The output may be shorted to voltages in this range provided the power dissipation of the package is not exceeded. VOUT short circuit current is typically 80 mA.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7245A/AD7248A features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

REV. B |

–3– |

AD7245A/AD7248A

AD7245A ORDERING GUIDE

|

Temperature |

Relative |

Package |

Model1 |

Range |

Accuracy |

Option2 |

AD7245AAN |

–40°C to +85°C |

±3/4 LSB |

N-24 |

AD7245ABN |

–40°C to +85°C |

±1/2 LSB |

N-24 |

AD7245AAQ |

–40°C to +85°C |

±3/4 LSB |

Q-24 |

AD7245ATQ3 |

–55°C to +125°C |

±3/4 LSB |

Q-24 |

AD7245AAP |

–40°C to +85°C |

±3/4 LSB |

P-28A |

AD7245AAR |

–40°C to +85°C |

±3/4 LSB |

R-24 |

AD7245ABR |

–40°C to +85°C |

±1/2 LSB |

R-24 |

AD7245ATE3 |

–55°C to +125°C |

±3/4 LSB |

E-28A |

NOTES

1To order MIL-STD-883, Class B processed parts, add /883B to part number. Contact our local sales office for military data sheet and availability.

2E = Leadless Ceramic Chip Carrier; N = Plastic DIP; P = Plastic Leaded Chip Carrier; Q = Cerdip; R = SOIC.

3This grade will be available to /883B processing only.

AD7248A ORDERING GUIDE

|

Temperature |

Relative |

Package |

Model1 |

Range |

Accuracy |

Option2 |

AD7248AAN |

–40°C to +85°C |

±3/4 LSB |

N-20 |

AD7248ABN |

–40°C to +85°C |

±1/2 LSB |

N-20 |

AD7248AAQ |

–40°C to +85°C |

±3/4 LSB |

Q-20 |

AD7248ATQ3 |

–55°C to +125°C |

±3/4 LSB |

Q-20 |

AD7248AAP |

–40°C to +85°C |

±3/4 LSB |

P-20A |

AD7248AAR |

–40°C to +85°C |

±3/4 LSB |

R-20 |

AD7248ABR |

–40°C to +85°C |

±1/2 LSB |

R-20 |

NOTES

1To order MIL-STD-883, Class B processed parts, add /883B to part number. Contact our local sales office for military data sheet and availability.

2N = Plastic DIP; P = Plastic Leaded Chip Carrier; Q = Cerdip; R = SOIC. 3This grade will be available to /883B processing only.

TERMINOLOGY

RELATIVE ACCURACY

Relative Accuracy, or endpoint nonlinearity, is a measure of the actual deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after allowing for zero and full scale and is normally expressed in LSBs or as a percentage of full-scale reading.

DIFFERENTIAL NONLINEARITY

Differential Nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of ±1 LSB max over the operating temperature range ensures monotonicity.

DIGITAL FEEDTHROUGH

Digital Feedthrough is the glitch impulse injected from the digital inputs to the analog output when the inputs change state. It is measured with LDAC high and is specified in nV-s.

DAC GAIN ERROR

DAC Gain Error is a measure of the output error between an ideal DAC and the actual device output with all 1s loaded after offset error has been allowed for. It is, therefore defined as:

Measured Value—Offset—Ideal Value

where the ideal value is calculated relative to the actual reference value.

UNIPOLAR OFFSET ERROR

Unipolar Offset Error is a combination of the offset errors of the voltage mode DAC and the output amplifier and is measured when the part is configured for unipolar outputs. It is present for all codes and is measured with all 0s in the DAC register.

BIPOLAR ZERO OFFSET ERROR

Bipolar Zero Offset Error is measured when the part is configured for bipolar output and is a combination of errors from the DAC and output amplifier. It is present for all codes and is measured with a code of 2048 (decimal) in the DAC register.

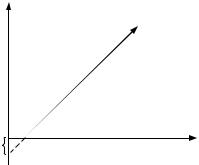

SINGLE SUPPLY LINEARITY AND GAIN ERROR

The output amplifier of the AD7245A/AD7248A can have a true negative offset even when the part is operated from a single positive power supply. However, because the lower supply rail to the part is 0 V, the output voltage cannot actually go negative. Instead the output voltage sits on the lower rail and this results in the transfer function shown. This is an offset effect and the transfer function would have followed the dotted line if the output voltage could have gone negative. Normally, linearity is measured after offset and full scale have been adjusted or allowed for. On the AD7245A/AD7248A the negative offset is allowed for by calculating the linearity from the code which the amplifier comes off the lower rail. This code is given by the negative offset specification. For example, the single supply linearity specification applies between Code 3 and Code 4095 for the 25°C specification and between Code 5 and Code 4095 over the TMIN to TMAX temperature range. Since gain error is also measured after offset has been allowed for, it is calculated between the same codes as the linearity error. Bipolar linearity and gain error are measured between Code 0 and Code 4095.

OUTPUT

VOLTAGE

0V

NEGATIVE DAC CODE OFFSET

–4– |

REV. B |

AD7245A/AD7248A

AD7245A PIN FUNCTION DESCRIPTIONS

(DIP PIN NUMBERS)

Pin |

Mnemonic |

Description |

|

|

|

l |

VSS |

Negative Supply Voltage (0 V for single |

|

|

supply operation). |

2 |

ROFS |

Bipolar Offset Resistor. This provides |

|

|

access to the on-chip application resistors |

|

|

and allows different output voltage ranges. |

3 |

REF OUT |

Reference Output. The on-chip reference |

|

|

is provided at this pin and is used when |

|

|

configuring the part for bipolar outputs. |

4 |

AGND |

Analog Ground. |

5 |

DB11 |

Data Bit 11. Most Significant Bit (MSB). |

6–11 |

DB10–DB5 |

Data Bit 10 to Data Bit 5. |

12 |

DGND |

Digital Ground. |

13–16 |

DB4–DB1 |

Data Bit 4 to Data Bit 1. |

17 |

DB0 |

Data Bit 0. Least Significant Bit (LSB). |

18 |

CS |

Chip Select Input (Active LOW). The |

|

|

device is selected when this input is active. |

|

|

|

Pin |

Mnemonic |

Description |

|

|

|

19 |

WR |

Write Input (Active LOW). This is used in |

|

|

conjunction with CS to write data into the |

|

|

input latch of the AD7245A. |

20 |

LDAC |

Load DAC Input (Active LOW). This is |

|

|

an asynchronous input which when active |

|

|

transfers data from the input latch to the |

|

|

DAC latch. |

21 |

CLR |

Clear Input (Active LOW). When this |

|

|

input is active the contents of the DAC |

|

|

latch are reset to all 0s. |

22 |

VDD |

Positive Supply Voltage. |

23 |

RFB |

Feedback Resistor. This allows access to |

|

|

the amplifier’s feedback loop. |

24 |

VOUT |

Output Voltage. Three different output |

|

|

voltage ranges can be chosen: 0 V to 5 V, |

|

|

0 V to 10 V or –5 V to +5 V. |

|

|

|

AD7245A PIN CONFIGURATIONS

DIP and SOIC |

PLCC |

LCCC |

VSS |

1 |

|

24 |

VOUT |

|

|

|

|

|

ROFS |

2 |

|

23 |

RFB |

|

|

|

|

|

REF OUT |

3 |

|

22 |

VDD |

OUT |

OFS |

SS |

NC |

OUT |

FB |

DD |

||||

REF |

R |

V |

V |

R |

V |

|||||

4 |

3 |

2 |

|

1 |

|

28 |

|

27 |

|

26 |

OUTREF 4

OFS |

SS |

R |

V |

3 |

2 |

NC |

OUT |

V |

|

1 |

28 |

FB |

DD |

R |

V |

27 |

26 |

AGND |

4 |

|

21 |

CLR |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AGND |

5 |

|

|

|

|

|

|

|

25 |

CLR |

AD7245A |

AGND |

5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

25 |

CLR |

|

|

|

|

|

|

|

||||||||

(MSB) DB11 |

5 |

20 |

LDAC |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB11 |

6 |

|

|

|

|

|

|

|

24 |

LDAC |

|

TOP VIEW |

DB11 |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

24 |

LDAC |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

DB10 |

6 |

(NOT TO SCALE) |

19 |

WR |

DB10 |

7 |

|

|

|

AD7245A |

|

|

|

|

23 |

WR |

DB10 |

7 |

|

|

AD7245A |

|

23 |

WR |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||||||

DB9 |

7 |

|

18 |

CS |

|

|

|

|

|

TOP VIEW |

|

|

|

|

22 |

NC |

NC |

8 |

|

|

TOP VIEW |

|

22 NC |

|||||||||

|

NC |

8 |

|

|

|

|

|

|

|

|

|

|

(NOT TO SCALE) |

|

|

|||||||||||||||||

|

|

|

|

DB0 (LSB) |

|

|

|

|

|

(NOT TO SCALE) |

|

|

|

|

DB9 |

9 |

|

|

|

|

|

|

|

21 |

CS |

|||||||

DB8 |

8 |

|

17 |

DB9 |

9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

21 |

CS |

DB8 |

10 |

|

|

|

|

|

|

|

20 |

DB0 |

|

|

|

|

|

DB1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

DB7 |

9 |

|

16 |

DB8 |

10 |

|

|

|

|

|

|

|

|

|

|

|

|

|

20 |

DB0 |

DB7 11 |

|

|

|

|

|

|

|

19 |

DB1 |

||

|

|

|

|

DB2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

DB6 |

10 |

|

15 |

DB7 |

11 |

|

|

|

|

|

|

|

|

|

|

|

|

|

19 |

DB1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DB3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

DB5 |

11 |

|

14 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 13 14 15 16 17 18 |

|

||||||||

|

|

|

|

|

|

|

|

DB6 |

DB5 |

DGND |

|

NC |

|

DB4 |

|

DB3 |

|

DB2 |

|

|

|

|

DB6 |

DB5 |

DGND |

NC |

|

DB4 |

DB3 |

DB2 |

|

|

DGND |

12 |

|

13 |

DB4 |

|

|

12 |

13 |

14 |

|

15 |

|

16 |

|

17 |

|

18 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

NC = NO CONNECT

NC = NO CONNECT

REV. B |

–5– |

Loading...

Loading...