Analog Devices AD7569AR, AD7569AQ, AD7569AN, AD7569TQ, AD7569TE Datasheet

...

LC2MOS

a Complete, 8-Bit Analog I/0 Systems

AD7569/AD7669

FEATURES

2 ms ADC with Track/Hold

1 ms DAC with Output Amplifier

AD7569, Single DAC Output AD7669, Dual DAC Output

On-Chip Bandgap Reference Fast Bus Interface

Single or Dual 5 V Supplies

GENERAL DESCRIPTION

The AD7569/AD7669 is a complete, 8-bit, analog I/O system on a single monolithic chip. The AD7569 contains a high speed successive approximation ADC with 2 μs conversion time, a track/ hold with 200 kHz bandwidth, a DAC and an output buffer amplifier with 1 μs settling time. A temperature-compensated 1.25 V bandgap reference provides a precision reference voltage for the ADC and the DAC. The AD7669 is similar, but contains two DACs with output buffer amplifiers.

A choice of analog input/output ranges is available. Using a supply voltage of +5 V, input and output ranges of zero to 1.25 V and zero to 2.5 volts may be programmed using the RANGE input pin. Using a ±5 V supply, bipolar ranges of ±1.25 V or

±2.5 V may be programmed.

Digital interfacing is via an 8-bit I/O port and standard microprocessor control lines. Bus interface timing is extremely fast, allowing easy connection to all popular 8-bit microprocessors. A separate start convert line controls the track/hold and ADC to give precise control of the sampling period.

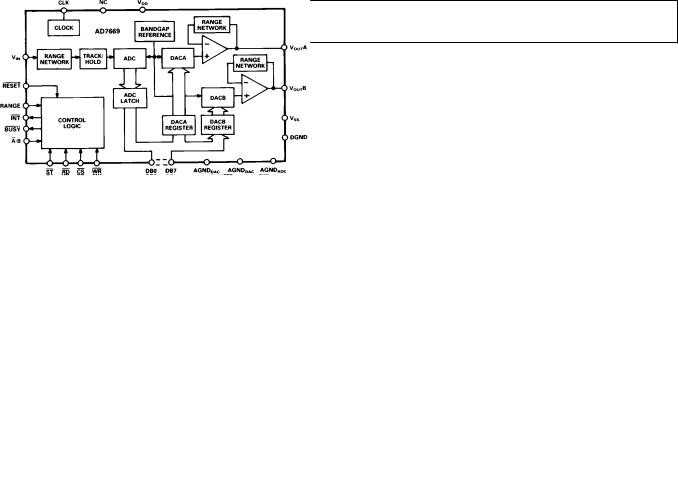

AD7569 FUNCTIONAL BLOCK DIAGRAM

AD7669 FUNCTIONAL BLOCK DIAGRAM

PRODUCT HIGHLIGHTS

The AD7569/AD7669 is fabricated in Linear-Compatible CMOS (LC2MOS), an advanced, mixed technology process combining precision bipolar circuits with low power CMOS logic. The AD7569 is packaged in a 24-pin, 0.3" wide “skinny” DIP, a 24-terminal SOIC and 28-terminal PLCC and LCCC packages. The AD7669 is available in a 28-pin, 0.6" plastic DIP, 28-terminal SOIC and 28-terminal PLCC package.

REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

1.Complete Analog I/O on a Single Chip.

The AD7569/AD7669 provides everything necessary to interface a microprocessor to the analog world. No external components or user trims are required and the overall accuracy of the system is tightly specified, eliminating the need to calculate error budgets from individual component specifications.

2.Dynamic Specifications for DSP Users.

In addition to the traditional ADC and DAC specifications, the AD7569/AD7669 is specified for ac parameters, including signal-to-noise ratio, distortion and input bandwidth.

3.Fast Microprocessor Interface.

The AD7569/AD7669 has bus interface timing compatible with all modern microprocessors, with bus access and relinquish times less than 75 ns and write pulse width less than 80 ns.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 |

World Wide Web Site: http://www.analog.com |

Fax: 617/326-8703 |

© Analog Devices, Inc., 1996 |

AD7569/AD7669–SPECIFICATIONS

|

|

|

|

|

|

1 |

(VDD = +5 V 6 5%; VSS2 = RANGE = AGNDDAC = AGNDADC = DGND = 0 V; RL = 2 kV, CL = 100 pF to AGNDDAC |

|||||||||

DAC SPECIFICATIONS |

unless otherwise noted. All specifications TMIN to TMAX unless otherwise noted.) |

|||||||||||||||

|

|

|

|

|

|

|

|

|

AD7569 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J, A Versions3 |

AD7569 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7669 |

K, B |

AD7569 |

AD7569 |

|

|

|

|

Parameter |

|

|

|

J Version |

Versions |

S Version |

T Version |

Units |

Conditions/Comments |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

STATIC PERFORMANCE |

|

|

|

|

|

|

|

|

||||||||

Resolution4 |

|

|

|

8 |

8 |

8 |

8 |

Bits |

|

|

|

|||||

|

Total Unadjusted Error5 |

±2 |

±2 |

±3 |

±3 |

LSB typ |

|

|

|

|||||||

|

Relative Accuracy5 |

±1 |

±1/2 |

±1 |

±1/2 |

LSB max |

|

|

|

|||||||

|

Differential Nonlinearity5 |

±1 |

±3/4 |

±1 |

±3/4 |

LSB max |

Guaranteed Monotonic |

|||||||||

|

Unipolar Offset Error |

±2 |

±1.5 |

±2 |

±1.5 |

|

DAC data is all 0s; VSS = 0 V |

|||||||||

|

@ +25°C |

|

|

|

LSB max |

Typical tempco is 10 μV/°C for +1.25 V range |

||||||||||

|

TMIN to TMAX |

±2.5 |

±2 |

±2.5 |

±2 |

LSB max |

DAC data is all 0s; VSS = –5 V |

|||||||||

|

Bipolar Zero Offset Error |

±2 |

±1 5 |

±2 |

±1.5 |

|

||||||||||

|

@ +25°C |

|

|

|

LSB max |

Typical tempco is 20 μV/°C for ±1.25 V range |

||||||||||

|

TMIN to TMAX |

±2.5 |

±2 |

±2.5 |

±2 |

LSB max |

|

|

|

|||||||

|

Full-Scale Error6 (AD7569 Only) |

±2 |

±1 |

±2 |

±1 |

|

VDD = 5 V |

|

|

|||||||

|

@ +25°C |

|

|

|

LSB max |

|

|

|

||||||||

|

TMIN to TMAX |

±3 |

±2 |

±4 |

±3 |

LSB max |

|

|

|

|||||||

|

Full-Scale Error6 (AD7669 Only) |

±3 |

|

|

|

|

VDD = 5 V |

|

|

|||||||

|

@ +25°C |

|

|

|

|

|

|

LSB max |

|

|

|

|||||

|

TMIN to TMAX |

±4.5 |

|

|

|

LSB max |

|

|

|

|||||||

|

DACA/DACB Full-Scale Error Match6 |

±2.5 |

|

|

|

|

|

|

|

|||||||

|

(AD7669 Only) |

|

|

|

LSB max |

VDD = 5 V |

VDD = ±5% |

|||||||||

|

Full Scale/ |

VDD, TA = +25°C |

0.5 |

0.5 |

0.5 |

0.5 |

LSB max |

VOUT = 2.5 V; |

||||||||

|

Full Scale/ |

VSS, TA = +25°C |

0.5 |

0.5 |

0.5 |

0.5 |

LSB max |

VOUT = –2.5 V; |

VSS = ±5% |

|||||||

|

Load Regulation at Full Scale |

0.2 |

0.2 |

0.2 |

0.2 |

LSB max |

RL = 2 kΩ to °/C |

|||||||||

DYNAMIC PERFORMANCE |

|

|

|

|

|

|

|

|

||||||||

|

Signal-to-Noise Ratio5 (SNR) |

44 |

46 |

44 |

46 |

dB min |

VOUT = 20 kHz full-scale sine wave with fSAMPLING = 400 kHz |

|||||||||

Total Harmonic Distortion5 (THD) |

48 |

48 |

48 |

48 |

dB max |

VOUT = 20 kHz full-scale sine wave with fSAMPLING = 400 kHz |

||||||||||

|

Intermodulation Distortion5 (IMD) |

55 |

55 |

55 |

55 |

dB typ |

fa = 18.4 kHz, fb = 14.5 kHz with fSAMPLING = 400 kHz |

|||||||||

ANALOG OUTPUT |

|

|

|

|

|

|

|

|

||||||||

Output Voltage Ranges |

|

|

|

|

|

|

|

|

||||||||

|

Unipolar |

|

|

|

0 to +1.25/2.5 |

|

|

|

Volts |

VDD = +5 V, VSS = 0 V |

||||||

|

Bipolar |

|

|

|

±1.25/±2.5 |

|

|

|

Volts |

VDD = +5 V, VSS = –5 V |

||||||

LOGIC INPUTS |

|

|

|

|

|

|

|

|

||||||||

|

CS |

, |

X |

/B, |

WR |

, RANGE, |

RESET |

, DB0–DB7 |

|

|

|

|

|

|

|

|

|

Input Low Voltage, VINL |

0.8 |

0.8 |

0.8 |

0.8 |

V max |

|

|

|

|||||||

|

Input High Voltage, VINH |

2.4 |

2.4 |

2.4 |

2.4 |

V min |

|

|

|

|||||||

|

Input Leakage Current |

10 |

10 |

10 |

10 |

μA max |

VIN = 0 to VDD |

|

|

|||||||

|

Input Capacitance7 |

10 |

10 |

10 |

10 |

pF max |

|

|

|

|||||||

|

DB0–DB7 |

|

|

|

|

|

|

|

|

|

|

|

||||

|

Input Coding (Single Supply) |

|

|

Binary |

|

|

|

|

|

|||||||

|

Input Coding (Dual Supply) |

|

|

2s Complement |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

||||||||

AC CHARACTERlSTICS7 |

|

|

|

|

|

Settling time to within ±1/2 LSB of final value |

||||||||||

|

Voltage Output Settling Time |

|

|

|

|

|

||||||||||

|

Positive Full-Scale Change |

2 |

2 |

2 |

2 |

μs max |

Typically 1 μs |

|

|

|||||||

|

Negative Full-Scale Change (Single Supply) |

4 |

4 |

4 |

4 |

μs max |

Typically 2 μs |

|

|

|||||||

|

Negative Full-Scale Change (Dual Supply) |

2 |

2 |

2 |

2 |

μs max |

Typically 1 μs |

|

|

|||||||

Digital-to-Analog Glitch Impulse5 |

15 |

15 |

15 |

15 |

nV secs typ |

|

|

|

||||||||

|

Digital Feedthrough5 |

1 |

1 |

1 |

1 |

nV secs typ |

VIN = ±2.5 V, 50 kHz Sine Wave |

|||||||||

|

VIN to VOUT Isolation |

60 |

60 |

60 |

60 |

dB typ |

||||||||||

DAC to DAC Crosstalk5 (AD7669 Only) |

1 |

|

|

|

nV secs typ |

|

|

|

||||||||

|

DACA to DACB Isolation5 (AD7669 Only) |

–70 |

|

|

|

dB max |

|

|

|

|||||||

POWER REQUIREMENTS |

|

|

|

|

|

|

|

|

||||||||

VDD Range |

|

|

|

4.75/5.25 |

4.75/5.25 |

4.75/5.25 |

4.75/5.25 |

V min/V max |

For Specified Performance |

|||||||

VSS Range (Dual Supplies) |

–4.75/–5.25 |

–4.75/–5.25 |

–4.75/–5.25 |

–4.75/–5.25 |

V min/V max |

Specified Performance also applies to VSS = 0 V |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

for unipolar ranges. |

||

IDD |

|

|

|

|

|

|

|

|

VOUT = VIN = 2.5 V; Logic Inputs = 2.4 V; CLK = 0.8 V |

|||||||

|

(AD7569) |

|

|

|

13 |

13 |

13 |

13 |

mA max |

Output unloaded |

||||||

|

(AD7669) |

|

|

|

18 |

|

|

|

mA max |

Outputs unloaded |

||||||

|

ISS (Dual Supplies) |

|

|

|

|

|

VOUT = VIN = –2.5 V; Logic Inputs = 2.4 V; CLK = 0.8 V |

|||||||||

|

(AD7569) |

|

|

|

4 |

4 |

4 |

4 |

mA max |

Output unloaded |

||||||

|

(AD7669) |

|

|

|

6 |

|

|

|

mA max |

Outputs unloaded |

||||||

|

|

|

|

|

|

|

|

|

||||||||

DAC/ADC MATCHING |

|

|

|

|

|

VIN to VOUT match with VIN = ±2.5 V, |

||||||||||

Gain Matching6 |

|

|

|

|

|

|||||||||||

|

@ +25°C |

|

|

|

1 |

1 |

1 |

1 |

% typ |

20 kHz sine wave |

||||||

|

TMIN to TMAX |

1 |

1 |

1 |

1 |

% typ |

|

|

|

|||||||

NOTES

1Specifications apply to both DACs in the AD7669. VOUT applies to both VOUTA and VOUTB of the AD7669. 2Except where noted, specifications apply for all output ranges including bipolar ranges with dual supply operation.

3Temperature ranges as follows: |

J, K versions; 0°C to +70°C |

|

A, B versions; –40°C to +85°C |

S, T versions; –55°C to +125°C

41 LSB = 4.88 mV for 0 V to +1.25 V output range, 9.76 mV for 0 V to +2.5 V and ±1.25 V ranges and 19.5 mV for ±2.5 V range. 5See Terminology.

6Includes internal voltage reference error and is calculated after offset error has been adjusted out. Ideal unipolar full-scale voltage is (FS – 1 LSB); ideal bipolar positive full-scale voltage is (FS/2 – 1 LSB) and ideal bipolar negative full-scale voltage is –FS/2.

7Sample tested at +25°C to ensure compliance.

Specifications subject to change without notice.

–2– |

REV. B |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7569/AD7669 |

ADC SPECIFICATIONS |

(VDD = +5 V 6 5%; VSS1 = RANGE = AGNDDAC = AGNDDAC = DGND = 0 V; fCLK = 5 MHz external unless other- |

|||||||||||||||||||||

wise noted. All specifications TMIN to TMAX unless otherwise noted.) Specifications apply to Mode 1 interface. |

|

|||||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7569 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

J, A Versions3 |

AD7569 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

AD7669 |

K, B |

AD7569 |

AD7569 |

|

|

|

|

Parameter |

|

|

|

|

|

|

|

|

J Version |

Versions |

S Version |

T Version |

Units |

Conditions/Comments |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DC ACCURACY |

|

|

|

|

|

|

|

|

||||||||||||||

|

Resolution3 |

|

|

|

|

|

|

|

|

8 |

|

8 |

8 |

8 |

Bits |

|

|

|||||

|

Total Unadjusted Error4 |

±3 |

|

±3 |

±4 |

±4 |

LSB typ |

|

|

|||||||||||||

Relative Accuracy4 |

±1 |

|

±1/2 |

±1 |

±1/2 |

LSB max |

|

|

||||||||||||||

Differential Nonlinearity4 |

±1 |

|

±3/4 |

±1 |

±3/4 |

LSB max |

No Missing Codes |

|||||||||||||||

Unipolar Offset Error |

±2 |

|

± 1.5 |

±2 |

± 1.5 |

|

Typical tempco is 10 μV/°C for +1.25 V range; VSS = 0 V |

|||||||||||||||

|

@ +25°C |

|

|

|

|

|

|

|

|

|

LSB max |

|

|

|||||||||

|

TMIN to TMAX |

±3 |

|

± 2.5 |

±3 |

± 2.5 |

LSB max |

Typical tempco is 20 μV/°C for + 1.25 V range; VSS = –5 V |

||||||||||||||

Bipolar Zero Offset Error |

±3 |

|

± 2.5 |

±3 |

± 2.5 |

|

||||||||||||||||

|

@ +25°C |

|

|

|

|

|

|

|

|

|

LSB max |

|

|

|||||||||

|

TMIN to TMAX |

± 3.5 |

|

±3 |

±4 |

± 3.5 |

LSB max |

|

|

|||||||||||||

Full-Scale Error5 |

|

|

|

|

|

|

VDD = 5 V |

|

||||||||||||||

|

@ +25°C |

|

|

|

|

|

|

|

|

–4, +0 |

–4, +0 |

–4, +0 |

–4, +0 |

LSB max |

|

|

||||||

|

TMIN to TMAX |

–5.5, +1.5 |

–5.5, +1.5 |

–7.5, +2 |

–7.5, +2 |

LSB max |

|

VDD = ±5% |

||||||||||||||

|

Full Scale/ |

VDD, TA = +25°C |

0.5 |

|

0.5 |

0.5 |

0.5 |

LSB max |

VIN = +2.5 V; |

|||||||||||||

|

Full Scale/ |

VSS, TA = +25°C |

0.5 |

|

0.5 |

0.5 |

0.5 |

LSB max |

VIN = –2.5 V; |

VSS = ±5% |

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DYNAMIC PERFORMANCE |

|

|

|

|

|

|

|

|

||||||||||||||

Signal-to-Noise Ratio4 (SNR) |

44 |

|

46 |

44 |

45 |

dB min |

VIN = 100 kHz full-scale sine wave with fSAMPLING = 400 kHz6 |

|||||||||||||||

|

Total Harmonic Distortion4 (THD) |

48 |

|

48 |

48 |

48 |

dB max |

VIN = 100 kHz full-scale sine wave with fSAMPLING = 400 kHz6 |

||||||||||||||

|

Intermodulation Distortion4 (IMD) |

60 |

|

60 |

60 |

60 |

dB typ |

fa = 99 kHz, fb = 96.7 kHz with fSAMPLING = 400 kHz |

||||||||||||||

|

Frequency Response |

0.1 |

|

0.1 |

0.1 |

0.1 |

dB typ |

VIN = ±2.5 V, dc to 200 kHz sine wave |

||||||||||||||

|

Track/Hold Acquisition Time7 |

200 |

|

200 |

300 |

300 |

ns typ |

|

|

|||||||||||||

ANALOG INPUT |

|

|

|

|

|

|

|

|

||||||||||||||

|

Input Voltage Ranges |

|

|

|

|

|

|

|

|

|||||||||||||

|

Unipolar |

|

|

|

|

|

|

|

|

0 to +1.25/ +2.5 |

|

|

Volts |

VDD = +5 V; VSS = 0 V |

||||||||

|

Bipolar |

|

|

|

|

|

|

|

|

±1.25/±2.5 |

|

|

Volts |

VDD = +5 V; VSS = –5 V |

||||||||

|

Input Current |

±300 |

|

±300 |

±300 |

±300 |

μA max |

See equivalent circuit Figure 5 |

||||||||||||||

|

|

|||||||||||||||||||||

|

Input Capacitance |

10 |

|

10 |

10 |

10 |

pF typ |

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

LOGIC INPUTS |

|

|

|

|

|

|

|

|

||||||||||||||

|

CS |

, |

RD |

, |

ST |

, CLK, |

RESET |

, RANGE |

|

|

|

|

|

|

|

|

||||||

|

Input Low Voltage, VINL |

0.8 |

|

0.8 |

0.8 |

0.8 |

V max |

|

|

|||||||||||||

|

Input High Voltage, VINH |

2.4 |

|

2.4 |

2.4 |

2.4 |

V min |

|

|

|||||||||||||

|

Input Capacitance8 |

10 |

|

10 |

10 |

10 |

pF max |

|

|

|||||||||||||

|

CS |

, |

RD |

, |

ST |

, RANGE, |

RESET |

|

|

|

|

|

|

μA max |

|

|

||||||

|

Input Leakage Current |

10 |

|

10 |

10 |

10 |

V IN = 0 to VDD |

|

||||||||||||||

|

CLK |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

Input Current |

|

|

|

|

|

|

|

|

|||||||||||||

|

|

IINL |

|

|

|

|

|

|

|

|

–1.6 |

|

–1.6 |

–1.6 |

–1.6 |

mA max |

VIN = 0 V |

|

||||

|

|

IINH |

|

|

|

|

|

|

|

|

40 |

|

40 |

40 |

40 |

μA max |

VIN = VDD |

|

||||

LOGIC OUTPUTS |

|

|

|

|

|

|

|

|

||||||||||||||

|

DB0–DB7, |

INT |

, |

BUSY |

|

|

|

|

|

|

|

|

|

|||||||||

|

VOL, Output Low Voltage |

0.4 |

|

0.4 |

0.4 |

0.4 |

V max |

ISINK = 1.6 mA |

|

|||||||||||||

|

VOH, Output High Voltage |

4.0 |

|

4.0 |

4.0 |

4.0 |

V min |

ISOURCE = 200 μA |

||||||||||||||

|

DB0–DB7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

μA max |

|

|

|||||

|

Floating State Leakage Current |

10 |

|

10 |

10 |

10 |

|

|

||||||||||||||

|

Floating State Output Capacitance8 |

10 |

|

10 |

10 |

10 |

pF max |

|

|

|||||||||||||

|

Output Coding (Single Supply) |

|

|

Binary |

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|||||||||||||||

|

Output Coding (Dual Supply) |

|

|

2s Complement |

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

||||||||||||||

CONVERSION TIME |

|

|

|

|

|

μs max |

|

|

||||||||||||||

|

With External Clock |

2 |

|

2 |

2 |

2 |

fCLK = 5 MHz |

|

||||||||||||||

|

With Internal Clock, TA = +25°C |

1.6 |

|

1.6 |

1.6 |

1.6 |

μs min |

Using recommended clock components shown in Figure 21. |

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2.6 |

|

2.6 |

2.6 |

2.6 |

μs max |

Clock frequency can be adjusted by varying RCLK. |

|

|

|

|

|

|

|

|

|

|

||||||||||||||

POWER REQUIREMENTS |

As per DAC Specifications |

|

|

|

|

|||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

NOTES

1Except where noted, specifications apply for all ranges including bipolar ranges with dual supply operation. 2Temperature ranges are as follows: J, K versions; 0°C to +70°C

A, B versions; –40°C to +85°C S, T versions; –55°C to +125°C

31 LSB = 4.88 mV for 0 V to +1.25 V range, 9.76 mV for 0 V to +2.5 V and ±1.25 V ranges and 19.5 mV for +2.5 V range. 4See Terminology.

5Includes internal voltage reference error and is calculated after offset error has been adjusted out. Ideal unipolar last code transition occurs at (FS – 3/2 LSB). Ideal bipolar last code transition occurs at (FS/2 – 3/2 LSB).

6Exact frequencies are 101 kHz and 384 kHz to avoid harmonics coinciding with sampling frequency.

7Rising edge of BUSY to falling edge of ST. The time given refers to the acquisition time, which gives a 3 dB degradation in SNR from the tested figure. 8Sample tested at +25°C to ensure compliance.

Specifications subject to change without notice.

REV. B |

–3– |

AD7569/AD7669–TIMING CHARACTERISTICS1 (See Figures 8, 10, 12; VDD = 5 V 6 5%; VSS = 0 V or –5 V 6 5%)

|

|

Limit at |

Limit at |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Limit at |

TMIN, TMAX |

TMIN, TMAX |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Parameter |

258C (All Grades) |

(J, K, A, B Grades) |

(S, T Grades) |

Units |

|

Test Conditions/Comments |

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

DAC Timing |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t1 |

80 |

80 |

90 |

ns min |

|

WR |

Pulse Width |

||||||||||||

t2 |

0 |

0 |

0 |

ns min |

|

CS, A/B to WR Setup Time |

|||||||||||||

t3 |

0 |

0 |

0 |

ns min |

|

CS, A/B to WR Hold Time |

|||||||||||||

t4 |

60 |

70 |

80 |

ns min |

|

Data Valid to WR Setup Time |

|||||||||||||

t5 |

10 |

10 |

10 |

ns min |

|

Data Valid to WR Hold Time |

|||||||||||||

ADC Timing |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t6 |

50 |

50 |

50 |

ns min |

|

ST |

|

Pulse Width |

|||||||||||

t7 |

110 |

130 |

150 |

ns max |

|

ST to BUSY Delay |

|||||||||||||

t8 |

20 |

30 |

30 |

ns max |

|

BUSY to INT Delay |

|||||||||||||

t9 |

0 |

0 |

0 |

ns min |

|

BUSY to CS Delay |

|||||||||||||

t10 |

0 |

0 |

0 |

ns min |

|

CS to |

RD |

Setup Time |

|||||||||||

t11 |

60 |

75 |

90 |

ns min |

|

RD Pulse Width Determined by t13. |

|||||||||||||

t12 |

0 |

0 |

0 |

ns min |

|

CS to RD Hold Time |

|||||||||||||

t132 |

60 |

75 |

90 |

ns max |

|

Data Access Time after |

RD |

; CL = 20 pF |

|||||||||||

t143 |

95 |

120 |

135 |

ns max |

Data Access Time after RD; CL = 100 pF |

||||||||||||||

10 |

10 |

10 |

ns min |

|

Bus Relinquish Time after |

RD |

|

||||||||||||

|

60 |

75 |

85 |

ns max |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

t15 |

65 |

75 |

85 |

ns max |

|

RD |

to |

INT |

Delay |

||||||||||

t16 |

120 |

140 |

160 |

ns max |

|

RD to BUSY Delay |

|||||||||||||

t172 |

60 |

75 |

90 |

ns max |

|

Data Valid Time after |

BUSY |

; CL = 20 pF |

|||||||||||

|

90 |

115 |

135 |

ns max |

Data Valid Time after |

BUSY |

; CL = 100 pF |

||||||||||||

NOTES

1Sample tested at +25°C to ensure compliance. All input control signals are specified with tR = tF = 5 ns (10% to 90% of +5 V) and timed from a voltage level of 1.6 V. 2t13 and t17 are measured with the load circuits of Figure 1 and defined as the time required for an output to cross either 0.8 V or 2.4 V.

3tl4 is defined as the time required for the data line to change 0.5 V when loaded with the circuit of Figure 2. Specifications subject to change without notice.

a. High-Z to VOH |

b. High-Z to VOL |

Figure 1. Load Circuits for Data Access Time Test

ABSOLUTE MAXIMUM RATINGS

VDD to AGNDDAC or AGNDADC . . . . . . . . . . . . . –0.3 V, +7 V VDD to DGND . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +7 V VDD to VSS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3 V, +14 V AGNDDAC or AGNDADC to DGND . . . . –0.3 V, VDD + 0.3 V AGNDDAC to AGNDADC . . . . . . . . . . . . . . . . . . . . . . . . . ±5 V Logic Voltage to DGND . . . . . . . . . . . . . –0.3 V, VDD + 0.3 V CLK Input Voltage to DGND . . . . . . . . . –0.3 V, VDD + 0.3 V

VOUT (VOUTA, VOUTB) to

AGND1DAC . . . . . . . . . . . . . . . . . VSS – 0.3 V, VDD + 0.3 V VIN to AGNDADC . . . . . . . . . . . . . . . VSS – 0.3 V, VDD + 0.3 V

NOTE

1Output may be shorted to any voltage in the range VSS to VDD provided that the power dissipation of the package is not exceeded. Typical short circuit current for a short to AGND or VSS is 50 mA.

a. VOH to High-Z |

b. VOL to High-Z |

Figure 2. Load Circuits for Bus Relinquish Time Test

Power Dissipation (Any Package) to +75°C . . . . . . . . 450 mW Derates above 75°C by . . . . . . . . . . . . . . . . . . . . . 6 mW/°C

Operating Temperature Range

Commercial (J, K) . . . . . . . . . . . . . . . . . . . . . . 0°C to +70°C Industrial (A, B) . . . . . . . . . . . . . . . . . . . . . –40°C to +85°C Extended (S, T) . . . . . . . . . . . . . . . . . . . . –55°C to +125°C Storage Temperature Range . . . . . . . . . . . . –65°C to +150°C Lead Temperature (Soldering, 10 secs) . . . . . . . . . . . +300°C

*Stresses above those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7569/AD7669 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

WARNING!

ESD SENSITIVE DEVICE

–4– |

REV. B |

AD7569/AD7669

NOTE:

The term DAC (Digital-to-Analog Converter) throughout the data sheet applies equally to the dual DACs in the AD7669 as well as to the single DAC of the AD7569 unless otherwise stated. It follows that the term VOUT applies to both VOUTA and VOUTB of the AD7669 also.

TERMINOLOGY Total Unadjusted Error

Total unadjusted error is a comprehensive specification that includes internal voltage reference error, relative accuracy, gain and offset errors.

Relative Accuracy (DAC)

Relative Accuracy or endpoint nonlinearity is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after allowing for offset and gain errors. For the bipolar output ranges, the endpoints of the DAC transfer function are defined as those voltages that correspond to negative full-scale and positive fullscale codes. For the unipolar output ranges, the endpoints are code 1 and code 255. Code 1 is chosen because the amplifier is now working in single supply and, in cases where the true offset of the amplifier is negative, it cannot be seen at code 0. If the relative accuracy were calculated between code 0 and code 255, the “negative offset” would appear as a linearity error. If the offset is negative and less than 1 LSB, it will appear at code 1, and hence the true linearity of the converter is seen between code 1 and code 255.

Relative Accuracy (ADC)

Relative Accuracy is the deviation of the ADC’s actual code transition points from a straight line drawn between the endpoints of the ADC transfer function. For the bipolar input ranges, these points are the measured, negative, full-scale transition point and the measured, positive, full-scale transition point. For the unipolar ranges, the straight line is drawn between the measured first LSB transition point and the measured full-scale transition point.

Differential Nonlinearity

Differential Nonlinearity is the difference between the measured change and an ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of ±1 LSB max ensures monotonicity (DAC) or no missed codes (ADC). A differential nonlinearity of ±3/4 LSB max ensures that the minimum step size (DAC) or code width (ADC) is 1/4 LSB, and the maximum step size or code width is 3/4 LSB.

Digital-to-Analog Glitch Impulse

Digital-to-Analog Glitch Impulse is the impulse injected into the analog output when the digital inputs change state with the DAC selected. It is normally specified as the area of the glitch in nV secs and is measured when the digital input code is changed by 1 LSB at the major carry transition.

Digital Feedthrough

Digital Feedthrough is also a measure of the impulse injected to the analog output from the digital inputs, but is measured when the DAC is not selected. It is essentially feedthrough across the die and package. It is also a measure of the glitch impulse transferred to the analog output when data is read from the internal ADC. It is specified in nV secs and is measured with WR high and a digital code change from all 0s to all 1s.

DAC-to-DAC Crosstalk (AD7669 Only)

The glitch energy transferred to the output of one DAC due to an update at the output of the second DAC. The figure given is the worst case and is expressed in nV secs. It is measured with an update voltage of full scale.

DAC-to-DAC Isolation (AD7669 Only)

DAC-to-DAC Isolation is the proportion of a digitized sine wave from the output of one DAC, which appears at the output of the second DAC (loaded with all 1s). The figure given is the worst case for the second DAC output and is expressed as a ra-

tio in dBs. It is measured with a digitized sine wave (fSAMPLING = 100 kHz) of 20 kHz at 2.5 V pk-pk.

Signal-to-Noise Ratio

Signal-to-Noise Ratio (SNR) is the measured signal to noise at the output of the converter. The signal is the rms magnitude of the fundamental. Noise is the rms sum of all the nonfundamental signals (excluding dc) up to half the sampling frequency.

SNR is dependent on the number of quantization levels used in the digitization process; the more levels, the smaller the quantization noise. The theoretical SNR for a sine wave is given by

SNR = (6.02N + 1.76) dB

where N is the number of bits. Thus for an ideal 8-bit converter, SNR = 50 dB.

Harmonic Distortion

Harmonic Distortion is the ratio of the rms sum of harmonics to the fundamental. For the AD7569/AD7669, Total Harmonic Distortion (THD) is defined as

20 log V22 +V32 +V42 +V52 +V62

V1

where V1 is the rms amplitude of the fundamental and V2, V3, V4, V5 and V6 are the rms amplitudes of the individual harmonics.

Intermodulation Distortion

With inputs consisting of sine waves at two frequencies, fa and fb, any active device with nonlinearities will create distortion products, of order (m + n), at sum and difference frequencies of mfa ± nfb where m, n = 0, l, 2, 3,… . Intermodulation terms are those for which m or n is not equal to zero. For example, the second order terms include (fa + fb) and (fa – fb) and the third order terms include (2fa + fb), (2fa – fb), (fa + 2fb) and (fa – 2fb).

REV. B |

–5– |

AD7569/AD7669

|

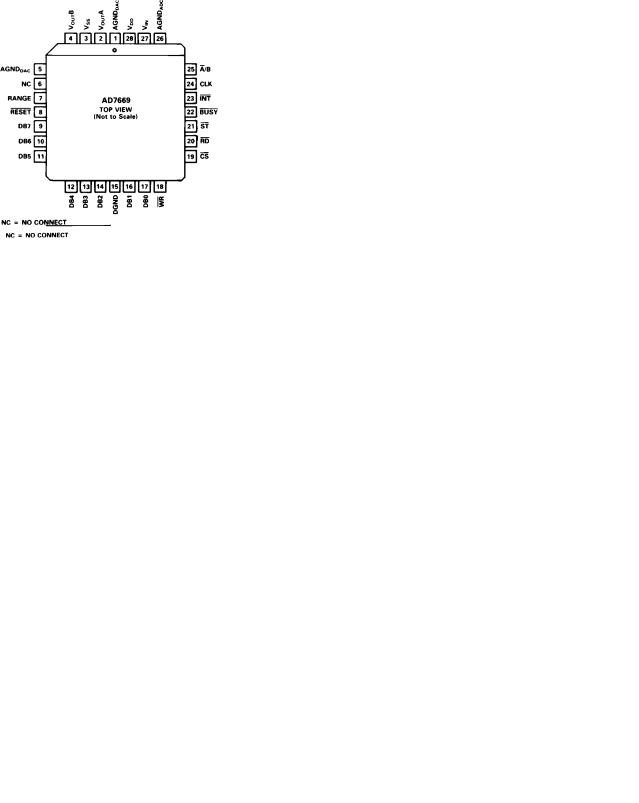

AD7569 PIN CONFIGURATIONS |

|

DIP, SOIC |

PLCC |

LCCC |

AD7669 PIN CONFIGURATIONS

DIP, SOIC

PLCC

ORDERING GUIDE

|

|

Relative |

|

|

Temperature |

Accuracy |

Package |

Model |

Range |

TMIN –TMAX |

Option1 |

AD7569JN |

0°C to +70°C |

±1 LSB |

N-24 |

AD7569JR |

0°C to +70°C |

±1 LSB |

R-24 |

AD7569AQ |

–40°C to +85°C |

±1 LSB |

Q-24 |

AD7569SQ2 |

–55°C to +125°C |

±1 LSB |

Q-24 |

AD7569BN |

–40°C to +85°C |

±0.5 LSB |

N-24 |

AD7569KN |

0°C to +70°C |

±0.5 LSB |

N-24 |

AD7569BR |

–40°C to +85°C |

±0.5 LSB |

R-24 |

AD7569BQ |

–40°C to +85°C |

±0.5 LSB |

Q-24 |

AD7569TQ2 |

–55°C to +125°C |

±1/2 LSB |

Q-24 |

AD7569JP |

0°C to +70°C |

±1 LSB |

P-28A |

AD7569SE2 |

–55°C to +125°C |

±1 LSB |

E-28A |

AD7569KP |

0°C to +70°C |

±1/2 LSB |

P-28A |

AD7569TE2 |

–55°C to +125°C |

±1/2 LSB |

E-28A |

AD7669AN |

–40°C to +85°C |

±1 LSB |

N-28 |

AD7669JN |

0°C to +70°C |

±1 LSB |

N-28 |

AD7669JP |

0°C to +70°C |

±1 LSB |

P-28A |

AD7669AR |

–40°C to +85°C |

±1 LSB |

R-28 |

AD7669JR |

0°C to +70°C |

±1 LSB |

R-28 |

NOTES

1E = Leadless Ceramic Chip Carrier; N = Plastic DIP; P = Plastic Leaded Chip Carrier; Q = Cerdip; R = Small Outline SOIC.

2To order MIL-STD-883, Class B processed parts, add /883B to part number. Contact your local sales office for military data sheet.

–6– |

REV. B |

Loading...

Loading...